1 电感主要类型

注:引用奇力新资料,本次主要介绍一体成型(molding)电感。

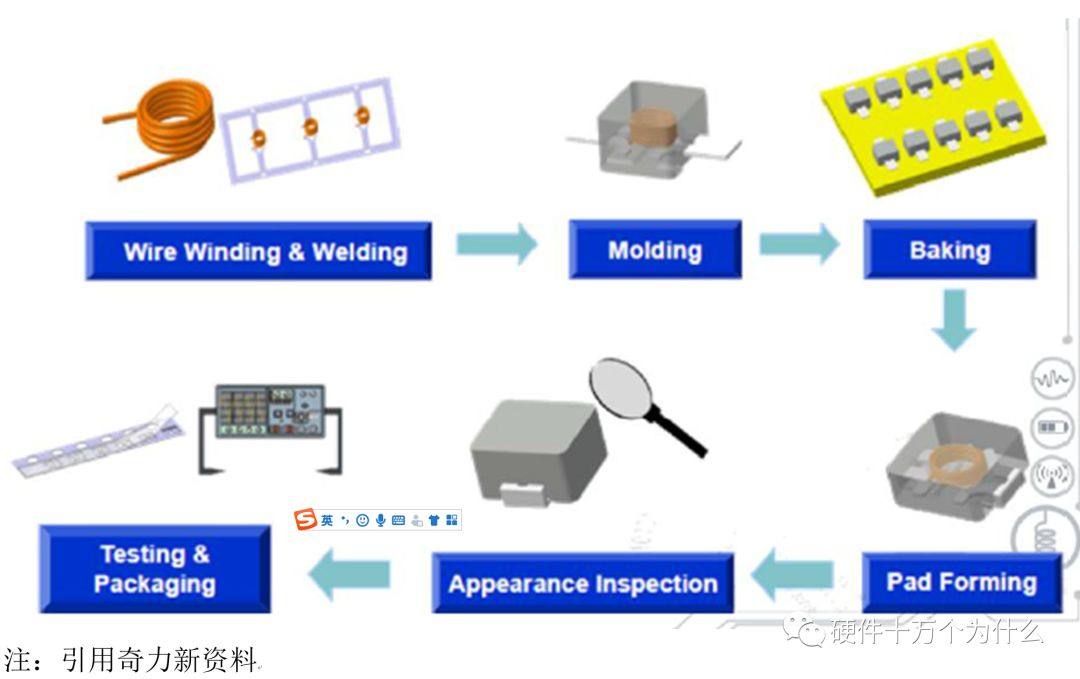

2 Molding电感生产工艺流程

3 一体成型电感的优势和“坑”

一体成型电感是通过铁粉模压成型而成,因此可以在相同封装条件下实现更大的额定电流,且由于一体成型电感更适合批量自动化生产,因此较传统绕线电感还具有明显的成本优势;另外一体成型电感较磁封胶结构电感具有更好的磁屏蔽效果,适合于EMI无法调试通过的项目使用。

但人无完人,一体成型电感也是有缺点的:常见的问题是生锈, 但今天我们来讲一讲一体成型电感隐藏的“坑”。

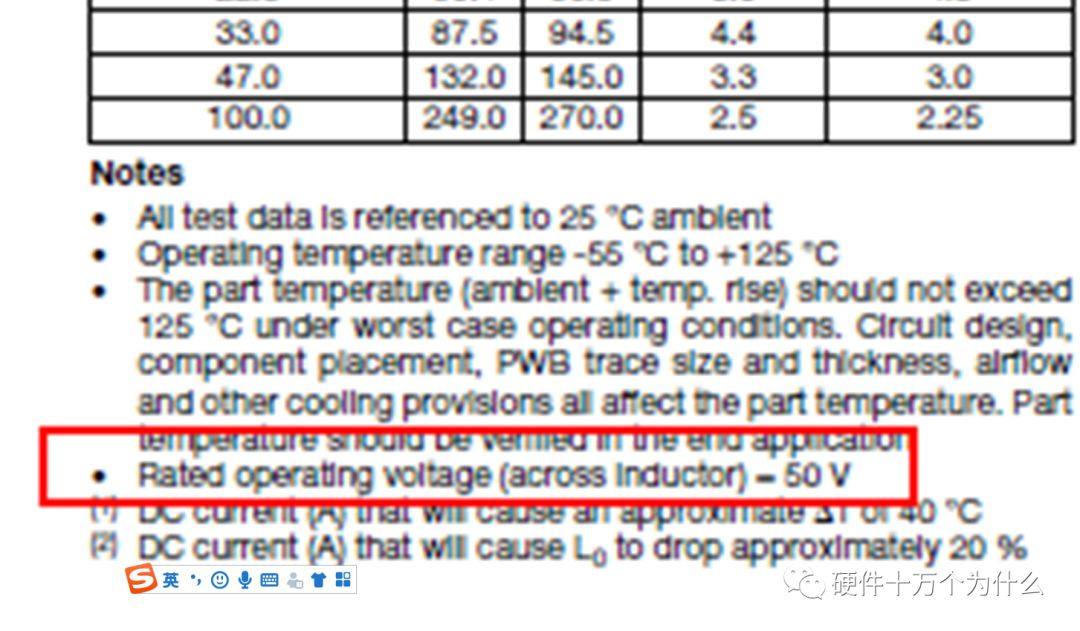

电感常见的降额是电流和温度,但是细心的用户会发现业界部分厂家在规格书上标识了额定工作电压,如果按照常规思维忽略那就离“坑”不远了。Vishay(业界最早开发一体成型的厂家)规格书中标示应用于50V以下电路,见下图所示。

4 正确理解一体成型电感额定电压参数

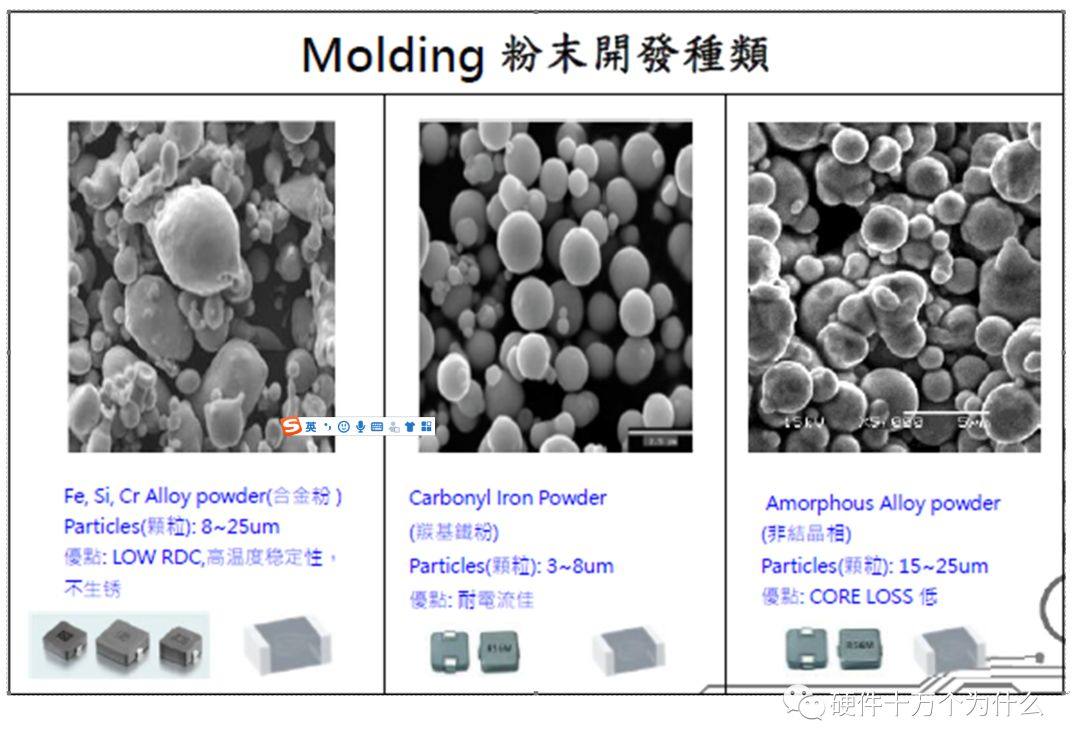

一体成型电感之前已提到是通过模压成型的,模压成型的材料是铁粉,常见的铁粉材料有如下3种:

一体成型电感的额定电压来源也是因为所用铁粉:传统绕线和磁封胶结构电感工字环材料是铁氧体(绝缘材质),漆包线耐电压一般是1KV,因此传统绕线和磁封胶结构电感没有耐电压指标一说,降额设计只需考虑电流和温度即可;一体成型铁粉是在合金粉外裹了一层环氧树脂绝缘层,环氧树脂绝缘层很薄,故一体成型电感会因加在电感两端电压过高造成铁粉耐压不足导致粉体击穿。

电感两端的压差从哪来:DC-DC应用,如下图典型的DC-DC降压电路,电压为50V转3V,实测电感两端的压差超过50V。

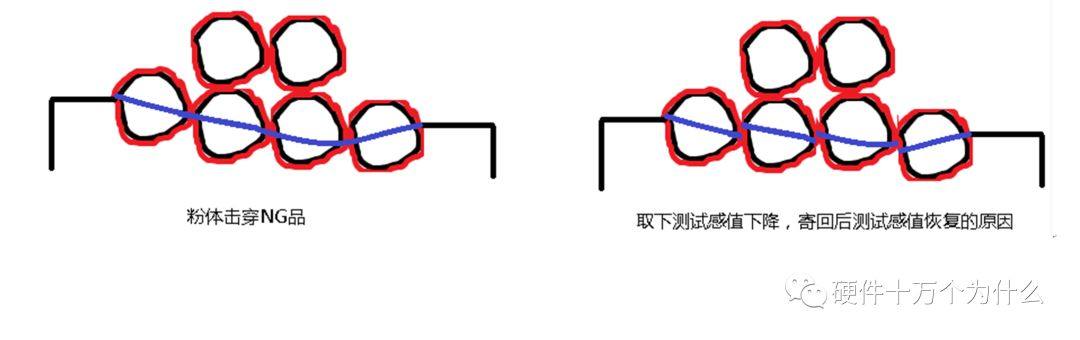

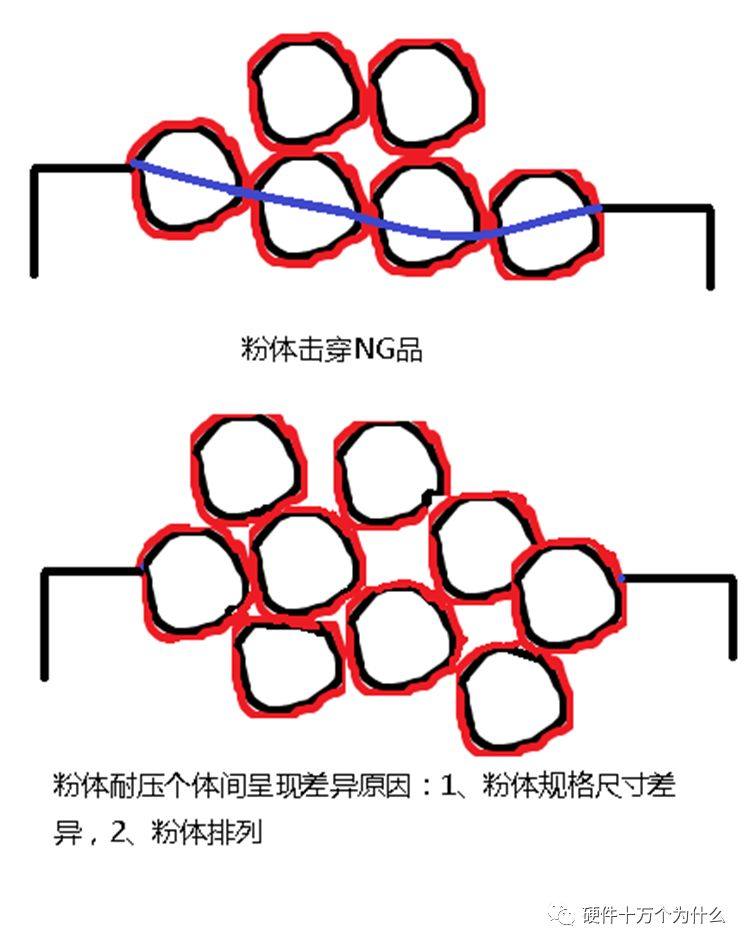

铁粉击穿导致电感失效很多是不可复现的(电路表现失效但在板或拆下使用LCR测试电感是合格的),此前本人分析时遇到过下面的这种情况:马上取下时由于击穿导电通路存在,量测感值偏小,但因委托第三方或投递给原厂分析时会因运输振动导致铁粉间的运动导致铁粉击穿形成的导电通路消除或击穿导电通道存在通路但由于未紧密接触仍存在绝缘层厚度仅电压较高时才形成通道,因此使用LCR测试是因测试条件电压过低(一般为0.5V或1V)及导电通道消除一体成型电感感值正常。一体成型电感粉体击穿失效示意图及失效单体测试合格原理示意图如下所示。

黑色为铁粉,红色为铁粉外围包裹环氧树脂绝缘层,蓝色为击穿导电通道

同时一体成型电感同一批次不同个体间额定电压耐压也存在差异,原因如下:耐压低的个体由于压力问题粉体排列呈直线,两个引出端之间的粉体个数少,示意图如下。

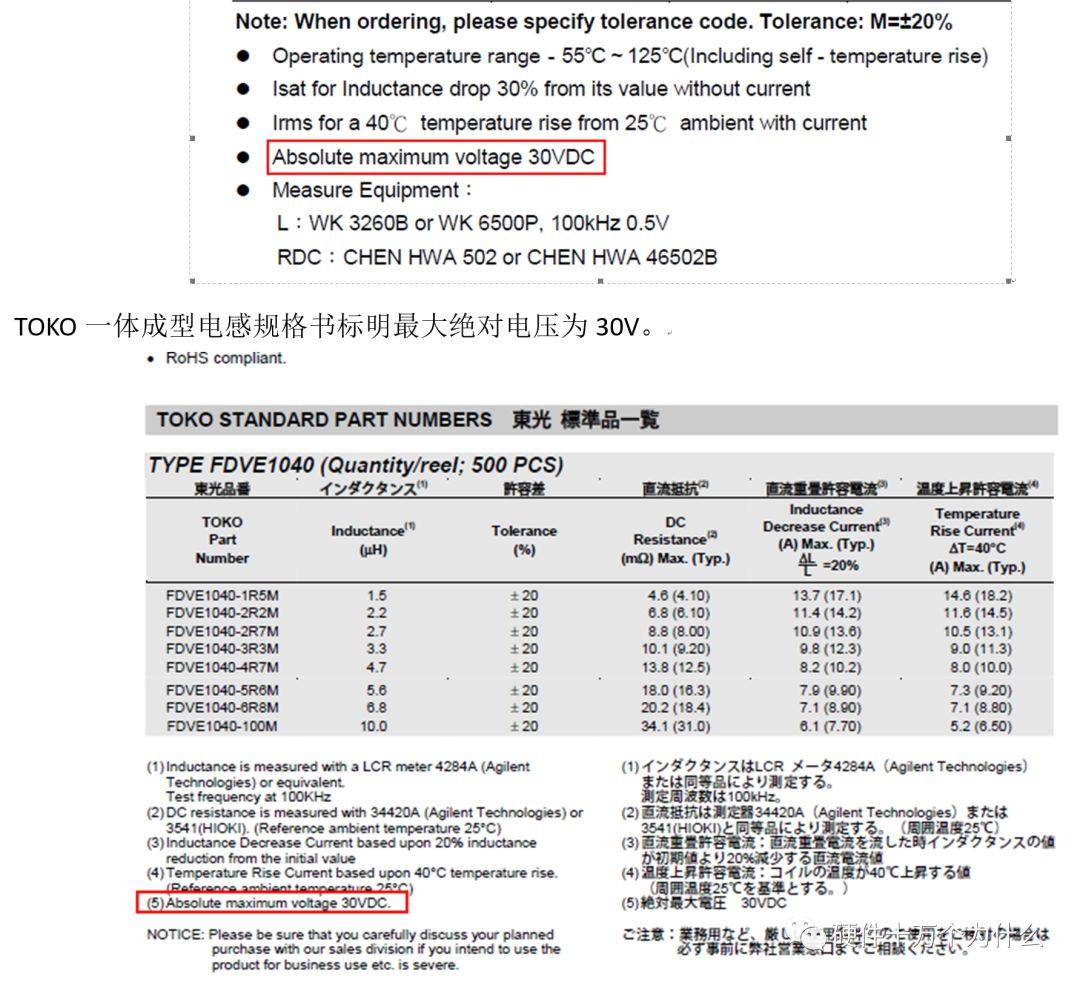

5 业界一体成型电感额定工作电压都是50V吗?

答案是不是的,因为铁粉供应商不同,因此绝缘层厚度也不尽相同,同时因molding压力会损伤部分铁粉的绝缘层,因此不同电感厂家会有不同的额定工作电压,对业界相关一体成型电感厂家额定工作电压进行了调研:

奇力新:30V。但如果采用的粉体使用德国进口的粉体耐压可做到60V,电压指标的制定与粉体本体特性及行业应用经验共同决定。

6 一体成型有“坑”,但切勿因噎废食

一体成型电感有耐电压问题,只需应用时注意即可,DC-DC降压或升压压差低于规格书额定电压值是没有风险的。

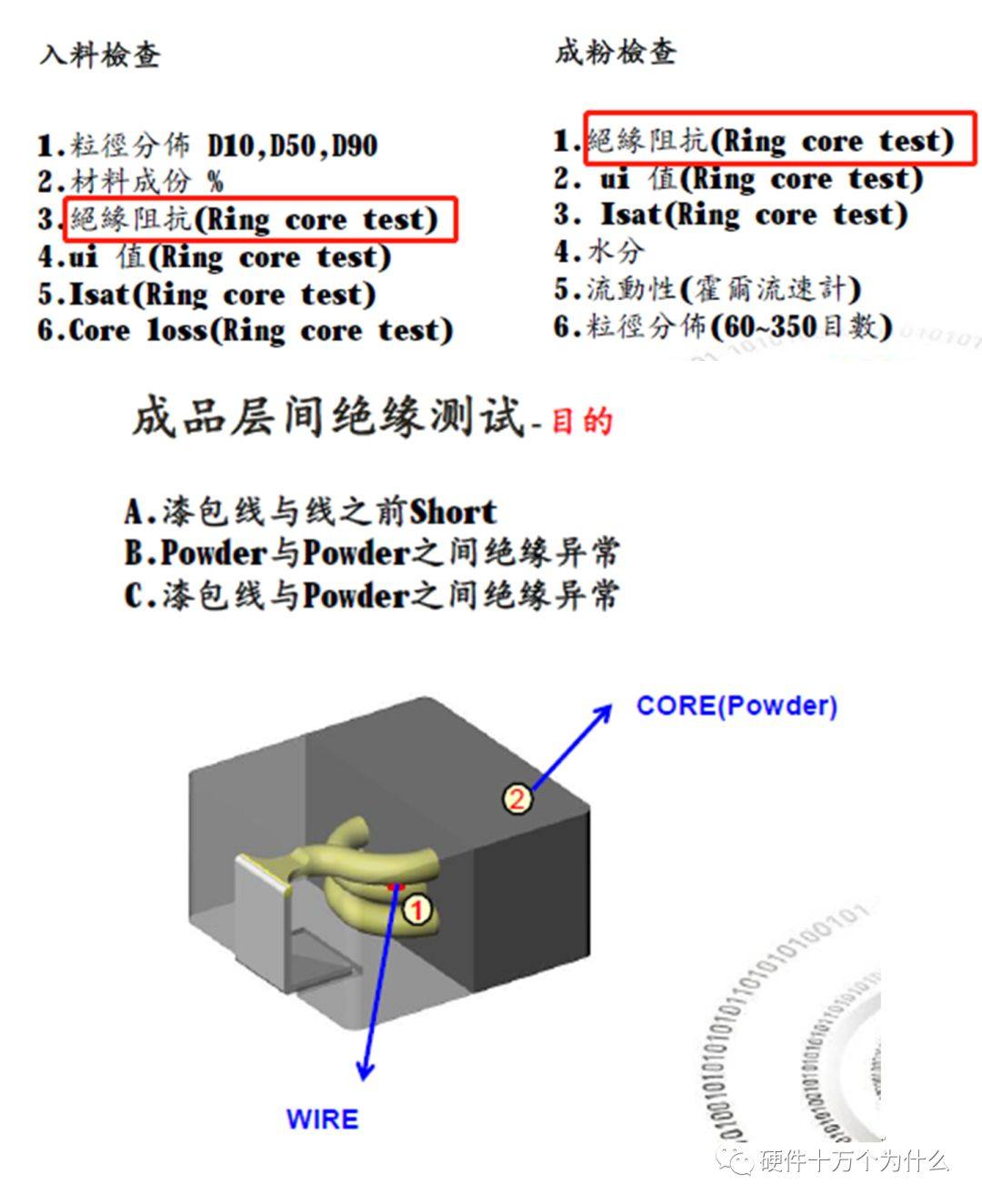

另附一体成型电感生产厂家主要管控措施,一体成型电感耐电压指标也是有保障的:

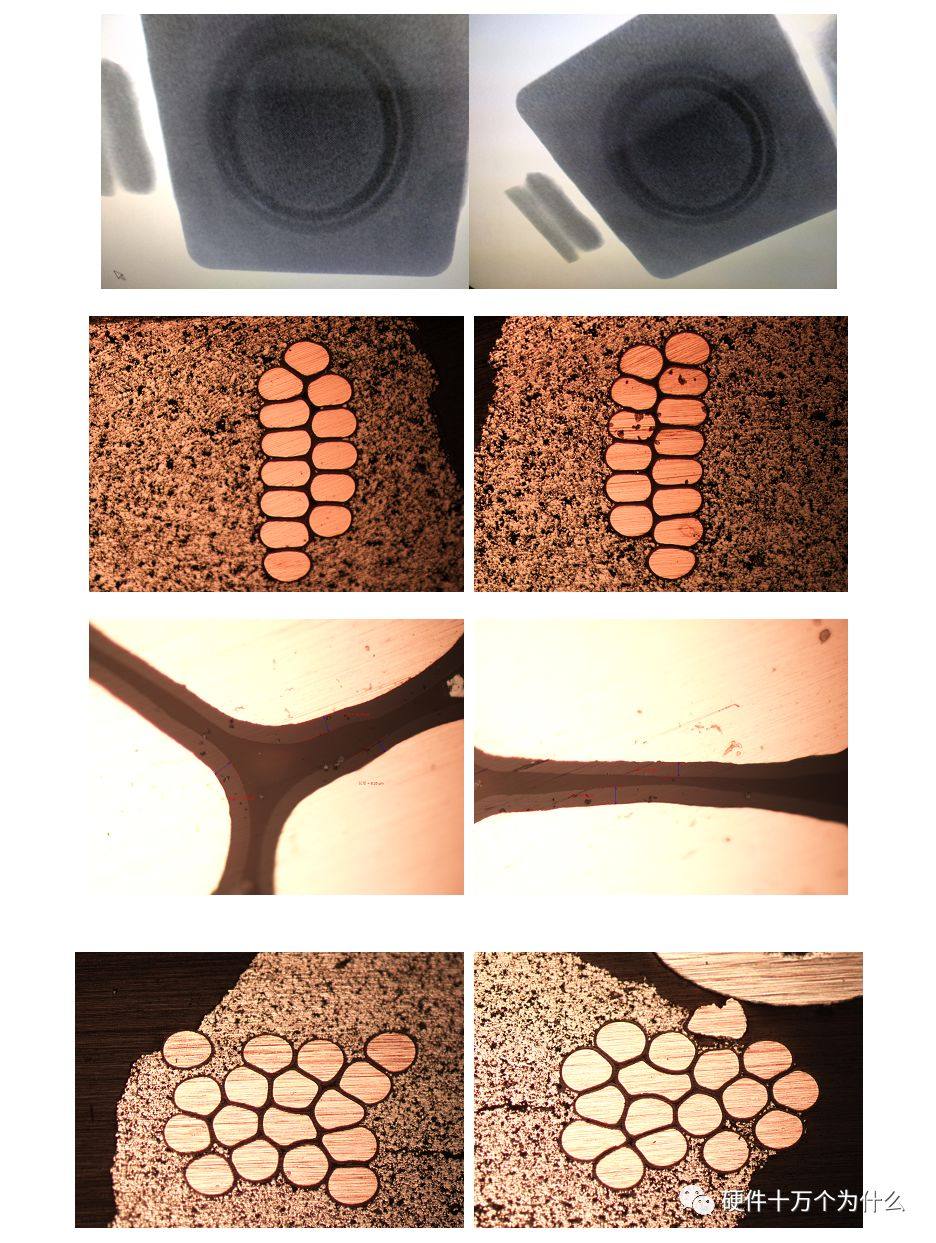

彩蛋:一体成型电感X射线图和切片图

本文硬十原创,已经在《硬件十万个为什么》头条号发布原创申明,谢绝一切微信公众号转载。本头条号已经与维权骑士签约,违者必究。

原文始发于微信公众号(硬件十万个为什么):一体成型电感这个“坑”你踩过吗