-相较三星5纳米(nm)而言,优化的3纳米(nm)工艺,性能提高23%,功耗降低45%,芯片面积减少16%

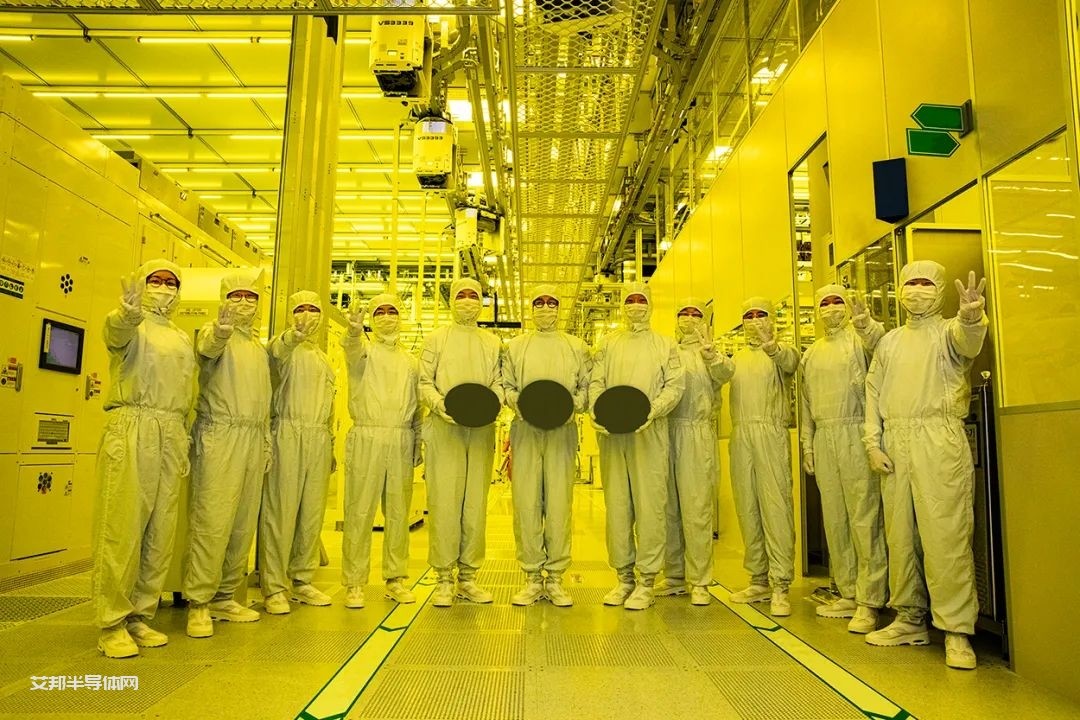

2022年6月30日,作为先进的半导体技术厂商之一的三星电子今日宣布, 基于3nm全环绕栅极(Gate-All-AroundT,简称 GAA)制程工艺节点的芯片已经开始初步生产。

三星电子首次实现GAA“多桥-通道场效应晶体管”(简称: MBCFET™ Multi-Bridge-Channel FET)应用打破了FinFET技术的性能限制,通过降低工作电压水平来提高能耗比,同时还通过增加驱动电流增强芯片性能。

三星首先将纳米片晶体管应用于高性能、低功耗计算领域的半导体芯片,并计划将其扩大至移动处理器领域。

一直以来,三星电子不断将新一代工艺技术应用于生产制造中。例如:三星的第一个High-K Metal Gate (HKMG) 工艺、FinFET 以及 EUV等。三星希望通过率先采用3nm工艺的‘多桥-通道场效应晶体管’( MBCFET™),将继续保持半导体行业前沿地位。同时,三星将继续在竞争性技术开发方面积极创新,并建立有助于加速实现技术成熟的流程。

3nm GAA技术采用了更宽通的纳米片,与采用窄通道纳米线的GAA技术相比能提供更高的性能和能耗比。3nm GAA技术上,三星能够调整纳米晶体管的通道宽度,优化功耗和性能,从而能够满足客户的多元需求。

此外,GAA的设计灵活性对设计技术协同优化(DTCO)²非常有利,有助于实现更好的PPA优势。与三星5nm工艺相比,第一代3nm工艺可以使功耗降低45%,性能提升23%,芯片面积减少16%;而未来第二代3nm工艺则使功耗降低50%,性能提升30%,芯片面积减少 35%。

与SAFE™合作伙伴一起,提供3nm设计基础设施和服务

随着工艺节点变得越来越小,而芯片性能需求越来越高,IC设计师们需要面对处理海量数据,以及验证功能更多、扩展更紧密的复杂产品的挑战。为了满足这些需求,三星致力于提供更稳定的设计环境,以帮助减少设计、验证和批准过程所需的时间,同时也提高了产品的可靠性。

自2021年第三季度以来,三星电子一直通过与包括ANSYS、楷登电子、西门子和新思科技在内的三星先进晶圆代工生态系统SAFE™(Samsung Advanced Foundry Ecosystem)合作伙伴的紧密协作,提供成熟的设计基础设施,使其能够在更短的时间内完善其产品。

1.PPA:Performance(性能)、Power(功耗)、Area(尺寸)三者的缩写。芯片的设计目标是实现更高的性能、更低的功耗和更小的面积。

2.有关设计技术协同优化(DTCO)的更多信息,请参阅以下链接:

《寻找最佳方案(Find the optimal for the best)》第一部分

https://semiconductor.samsung.com/us/newsroom/tech-blog/gaa-dtco-for-ppa/

《寻找最佳方案(Find the optimal for the best)》第二部分

https://semiconductor.samsung.com/us/newsroom/tech-blog/gaa-dtco-for-ppa-part-2/

三星以创新理念和技术激励世界,塑造未来。三星正致力于定义电视、智能手机、可穿戴设备、平板电脑、数字家电、网络系统以及内存、系统LSI、芯片代工和LED解决方案的世界。

欲知最新消息,请访问并关注三星半导体微信(三星半导体和显示官方)和微博(三星半导体)平台。

来自SAFE™合作伙伴

●ANSYS,[John Lee, Ansys电子、半导体和光学业务部副总裁兼总经理]

“ANSYS和三星携手合作,使用3nm GAA技术继续为最先进的设计提供支持技术。目前,Ansys多物理场仿真平台的签核精度,保证了我们与行业前沿地位的三星晶圆代工持续合作伙伴关系。Ansys始终致力于为我们共同的重要客户提供最佳的设计体验。”

●楷登电子,[Tom Beckley,楷登电子定制IC和PCB部门高级副总裁兼总经理]

“楷登电子祝贺三星实现了3nm GAA技术工艺节点的生产这一行业里程碑。我们与三星晶圆代工密切合作,让客户能够通过使用我们的数字解决方案实现3nm GAA技术工艺节点的最佳功率、性能和尺寸。从数据描述到全数字流程实施和签名,所有这些都基于Cadence Cerebrus AI的技术驱动,以最大限度地提高生产率。通过定制解决方案,我们与三星共同启用并验证了完整的AMS流程,通过自动化布局提高了电路设计和模拟的生产效率。我们期待着继续以这样的合作,取得更大的成功。”

●西门子 EDA,[Joe Sawicki, 西门子EDA IC 部门执行副总裁]

“西门子EDA很高兴通过与三星的合作,从最初开发阶段确保我们现有的软件平台也能够在三星新的3nm工艺节点上运行。通过SAFE™计划,西门子行业领先的3nm EDA工具得已认证,我们与三星的长期合作也为我们的共同客户创造了巨大的价值。与三星建立了长期的伙伴关系,为我们的共同客户创造了重大价值。”

●新思科技,[ Shankar Krishnamoorthy, 新思科技芯片实现事业部总经理]

“通过我们与三星代工事业部的长期战略合作,使得我们的解决方案能够支持三星的先进工艺,帮助我们共同的客户加快他们的设计周期。现在通过新思科技数字设计、模拟设计和IP产品,继续扩大对三星采用GAA架构的3nm工艺的支持,使客户能够为关键的高性能计算应用提供差异化的SoC。

*本文中的产品图片以及型号、数据、功能、性能、规格参数等仅供参考,三星有可能对上述内容进行改进,具体信息请参照产品实物、产品说明书或三星官网(www.samsung.com/cn)。除非经特殊说明,本网站中所涉及的数据均为三星内部测试结果,涉及的对比均为与三星产品相比较。

原文始发于微信公众号(三星半导体和显示官方):三星半导体|3纳米GAA架构制程技术芯片开始生产