今天主要以安靠技术(Amkor Technology)于2021年发表的一篇关于高密度超薄interposer Package on Package的研究论文《Chip-Last HDFO (High-Density Fan-Out) Interposer-PoP》为基础,聊聊中介层Package on Package技术发展趋势。备注:安靠是全球前三的封测代工企业。

看看名字“Chip-Last HDFO (High-Density Fan-Out) Interposer-PoP” 分为几个关键词:Chip-Last, HDFO(High-Density Fan-Out), Interposer, POP。接下来我们一一对其进行简述。

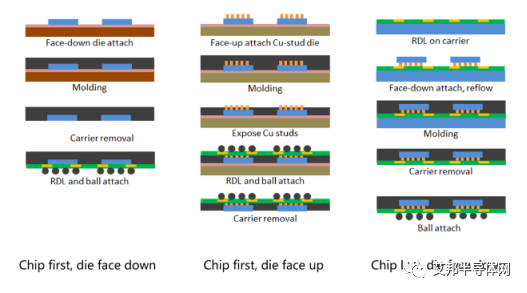

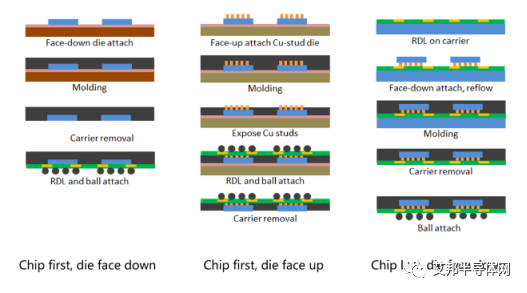

Chip-Last: 很简单有chip-last 就应该有chip-first。如图1所示,chip first 是指先制备好芯粒将其放于不同形式的Carrier 上,然后制备RDL层最后贴焊锡球。而Chip last 是先将RDL制备好,然后贴装芯粒,塑封最后再贴焊锡球。

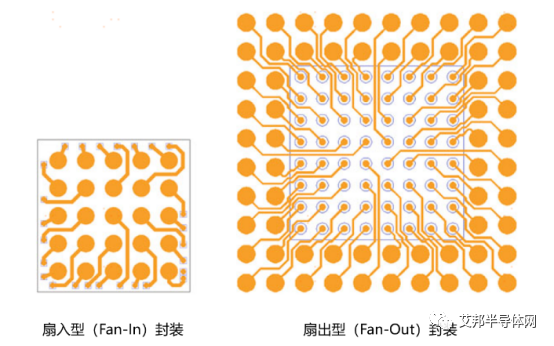

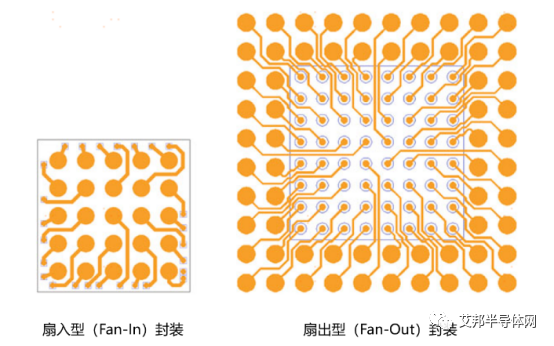

HDFO(High-Density Fan-Out)高密度扇出,这个概念对应的就有Fan-In。两者最大的差异为RDL布线,在扇入型封装中,RDL向内布线,而在扇出型封装中,RDL既可向内又可向外布线,所以扇出型封装可以实现更多的I/O。

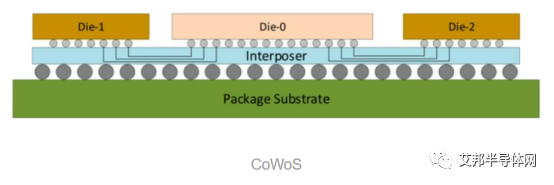

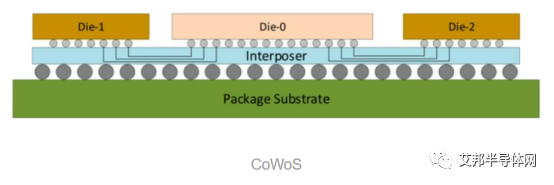

Interposer在我们艾邦半导体公众号里已经有多篇介绍。中介层利用硅通孔技术TSV,最终起到链接芯粒与Substrate的作用。

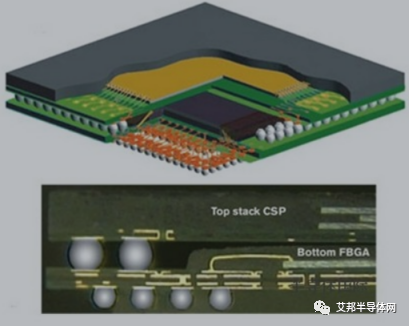

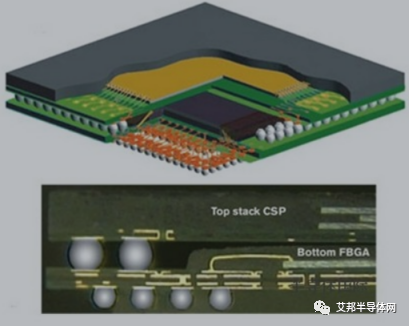

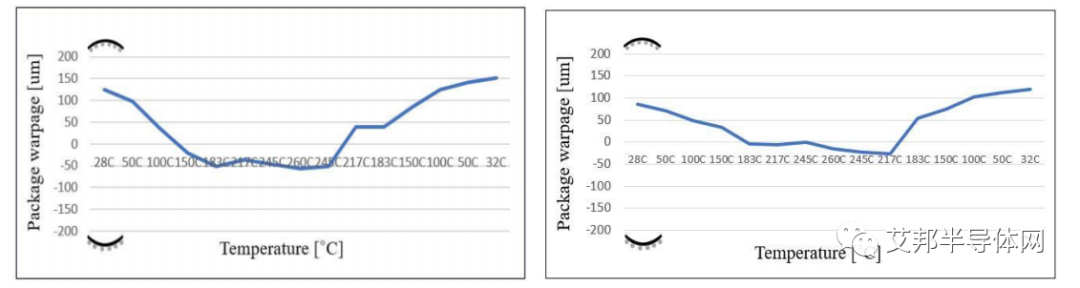

POP (Package on Package)是指叠层封装技术,通常应用在手机及笔记本电脑等领域,通过将逻辑芯片及存储芯片等不同芯片叠层封装从而实现超薄、低功耗、低信号损失的目的。在POP工艺中核心难点在于控制产品室温到260°的翘曲变形。

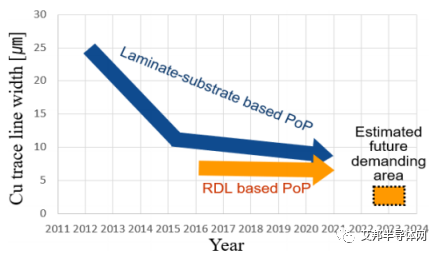

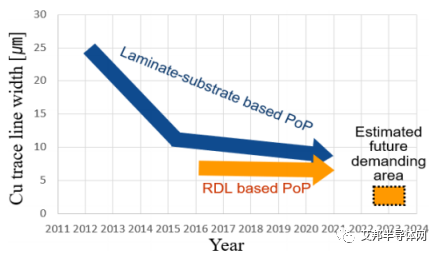

如图5所示,POP要不断的变薄还分两条技术路线:层压基板POP和RDL(重布线)POP。层压基板由于本身工艺很难再继续减薄,而RDL有着巨大的空间。

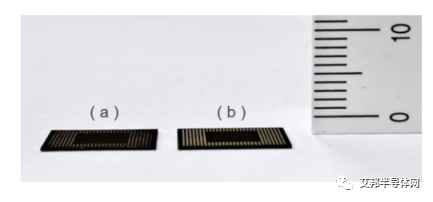

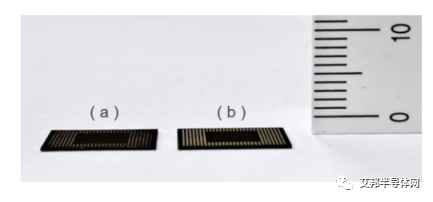

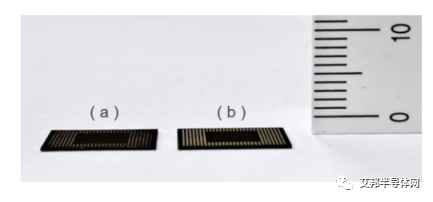

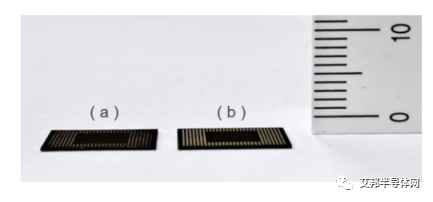

从图6和图7可以直接对比出RDL Layer于普通层压基板的厚度差异。上下都采用RDL层的产品厚度仅为400微米,而采用层压基板的同类产品厚度为450微米。通过使用RDL层可以减少近50微米。

图6 (a) interposer-PoP 上下层都为RDL

(b) interposer-PoP 下层为RDL上层为层压式substrate

图7 (a) interposer-PoP 下层为RDL上层为层压式substrate ;(b) interposer-PoP 上下层都为RDL

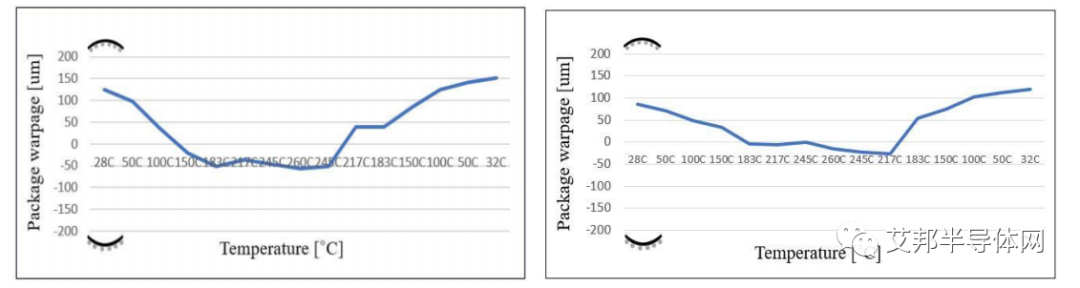

接着再对比一下两种产品动态翘曲的差异,两者翘曲差异不大,上下两层皆为RDL的翘起要略高于RLD+层压基板。当然还可以通过后续的RDL层设计优化进一步减少翘曲。

图8 左图为上下两层RDL的POP产品动态翘曲曲线

右图为RDL+层压基板POP产品动态翘曲曲线

最后,由于RDL具备超薄,良好的电性能,制备精度高等优点,随着业界对RDL层研发设备及工艺的不断投入,RDL技术在未来将会逐步进入越来越多的应用领域。当然还有一个更利于我国的优势,RDL的制程当前国内设备基本可以满足,没有卡脖子问题。相信我国RDL相关领域将会突飞猛进。

Chip-Last HDFO (High-Density Fan-Out) Interposer-PoP,Amkor Technology

原文始发于微信公众号(艾邦半导体网):先进封装之高密度超薄叠层封装(POP)介绍