艾邦半导体网在之前介绍过晶圆级和面板级的扇出型封装,包括eWLB, M Series等封装技术。在这里我们来介绍另一个衍生版本:天水华天在2015年推出了eSiFO(Embedded Silicon Fan-Out)技术,硅晶圆刻蚀后,晶片逐颗放入,随后被封起来,eSiFO属于Chip-first Die Face-up工艺。华天的该方案结合了高精度硅刻蚀,晶圆重构,高密度再布线等技术,具有多芯片高密度系统集成,小型化,翘曲小,适于多芯片和三维集成等突出特点。阅读本文前欢迎加入艾邦半导体封装产业链交流群。

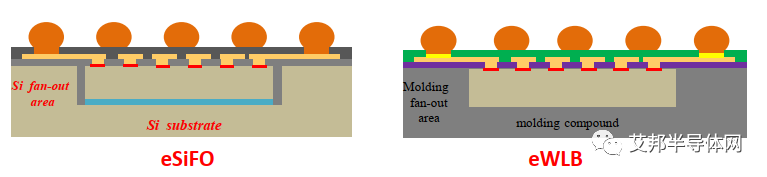

图一给出了华天的eSiFO跟之前介绍过的eWLB技术结构相比较,可以看出结构是非常相似的。最大的不同在于eSiFO将塑封料(EMC epoxy molding compound)改为silicon。用硅片作为承载,可以很好地解决EMC方案的多个痛点:

1.大大降低CTE mismatch带来的翘曲,降低内部应力

2.硅的mechanical modulus也比EMC要强,所以也能降低翘曲,从而降低封装难度,提升良品率;

3.硅的热导性能也远高于EMC,这大大提升了整个package的散热能力;

4.在硅中做通孔的密度要远大于在EMC中的通孔密度,也就是说TSV(through silicon via)要比TMV(through mold via)更容易做到高密度,高深宽比等;

6.硅承载片比EMC的表面更加平整,加上翘曲小,可以做更高密度的重布线层RDL;

7.整个package的厚度可以做得更薄,这对移动端的应用非常有吸引力;

8.相比于eWLB Die shift会更小, 更适合多芯片集成。

尽管华天在多个场合宣称相比于eWLB他们的eSiFO方案工序更简单,成本也更低。笔者持有不同的看法,目前eSiFO也只是在电容式指纹传感器等少数领域得到应用,并没有大规模普及。笔者认为eSiFO工艺更复杂,技术难度更大,成本也不会低。这个技术方案能不能大规模应用取决于诸多方面,比如技术方案能不能进一步降成本并提升性能,以及能不能开发出适合该方案的产品应用。

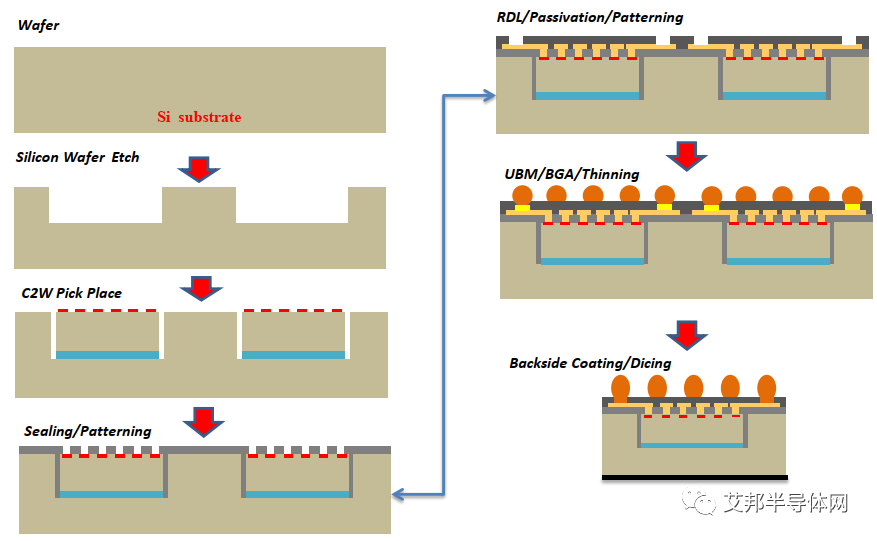

接下来我们来介绍一下华天的eSiFO的大体流程工艺,如图二所示。

1.8寸或者12寸晶圆清洗

2.Bosch工艺来制造直槽

3.芯片晶圆减薄抛光

4.芯片晶圆背面涂敷DAF膜(图中蓝色部分)。取决于产品应用,也可以用高热导的膜或者胶来提高散热性能, DAF的厚度通常在10-25微米

5.芯片晶圆切割

6.芯片贴片,需要高精度高速贴片机来完成此项任务。DAF是可被压缩的,所以直槽深度和芯片厚度的差别在一定程度上可以通过控制DAF被压缩后的厚度来调节

7.DAF烘烤固化

8.真空压膜机填充芯片和沟槽之间的缝隙。这一步骤往往也同时在重建晶圆表面形成钝化层。填充材料的选择至关重要,其CTE,Dk/Df等性能直接影响芯片的CTE mismatch,翘曲,电损耗,带宽等。该材料通常需要可光刻,低膨胀系数,低介电常数。干膜是常用的材料

9.形成第一重布层(RDL1),通常使用SAP(semi additive process)工艺流程来完成,可参照我们之前的文章。由于硅承载片优于EMC, 所以RDL的制造也相对容易些,线距线宽也可以做到更小

10.取决于产品性能需求,制造更多层的RDL

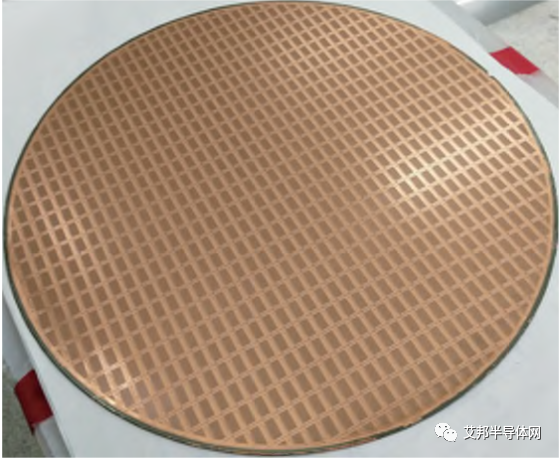

11.Surface finish,LGA和BGA都能实现。图三给出了一个应用例子

12.硅承载片也可以根据需要进行减薄来降低整个芯片的厚度

13.整个晶圆singulation

14.测试后放入某种carrier media,比如tape reel里

通常直槽深度在100微米左右,整个晶圆直槽的深度变化量不能超过5-10微米。不同芯片(包含DAF)的厚度也要求有比较小的变化。设计目标是芯片的表面跟硅承载片表面齐平。大cavity加上高精度要求使得Bosch工艺比较有挑战性。目前嵌入的芯片一般在15 mm x 15 mm以下。直槽的长宽都只比芯片的尺寸大40-50微米。直槽的底部和侧壁都要求比较平整。较低的Bosch刻蚀速率可以取得低于1微米的表面粗糙度。

图三:华天基于eSiFO技术的电容式指纹传感器晶圆封装后外观

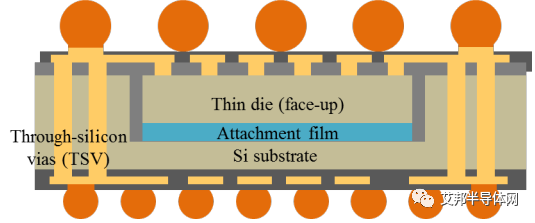

用硅做承载片的另一个优势是可以做TSV用于上下垂直互联,如图四所示。在做直槽时,我们也可以同样采用Bosch法制造TSV通孔。使用PECVD沉积制作绝缘层、使用物理气相沉积的方法沉积制作阻挡层(通常是300 nm的钛层)和种子层(通常是500 nm的铜层);选择一种电镀方法在盲孔中进行铜填充;使用化学和机械抛光(CMP)法去除多余的铜。对于低电流应用场景,TSV中心也可以使用polymer来填充。

使用图二中类似的工艺流程可以完成上面的RDL和表面植球。接下去采用临时键合技术(通常采用激光解键合)完成背面工艺。将晶圆临时键合到玻璃载体上然后减薄至目标厚度,使得TSV裸露出来。接下去完成芯片下表面的重布层和表面植球等工艺。

图四:华天基于eSiFO技术和TSV相结合来做芯片的3D stacking

多芯片的eSiFO方案也是非常相似和straightforward,在这里我们不再赘述。总结来讲,eSiFO方案是一种非常不错的尝试,体现了中国大陆坚持创新,努力实现技术自主的奋斗精神。而且某些对成本不是特别敏感且对性能需要更高的应用场景或许非常适合采用该方案。除了用硅来替代EMC,玻璃也是一种不错的材料,厦门云天开发了eGFO,嵌入式玻璃封装技术。相比于硅,玻璃在某些方面性能更好,比如其绝缘性好,还可以透可见光,天生适合高频的射频应用和光电应用。但是玻璃有个巨大的问题,就是容易裂,良率是个大的挑战。艾邦半导体在之前也介绍了玻璃加工工艺,以后有机会我们也会进一步介绍eGFO方案。

1.Ma, S, C. Wang, F. Zheng, D. Yu, H. Xie, X. Yang, L. Ma, P. Li , W. Liu , J. Yu , J. Goodelle, “Development of Wafer Level Process for the Fabrication of Advanced Capacitive Fingerprint Sensors Using Embedded Silicon Fan-Out (eSiFO®) Technology”, IEEE/ECTC Proceedings, May 2019, pp. 28–34

2.Ma, Shuying, et al. "Embedded silicon fan-out (eSiFO): A promising wafer level packaging technology for multi-chip and 3D system integration." 2018 IEEE 68th Electronic Components and Technology Conference (ECTC). IEEE, 2018

3.Wei, Hao, et al. "Warpage and Reliability Simulation of Super-Size Embedded Silicon Fan-out (eSiFO) Package with size 40mm× 40mm." 2022 23rd International Conference on Electronic Packaging Technology (ICEPT). IEEE, 2022

4.Gu, Xiaomin, et al. "Process development of large size embedded silicon fan-out (eSiFO) package." 2020 21st International Conference on Electronic Packaging Technology (ICEPT). IEEE, 2020

5.Chen, Cheng, et al. "Reliability of ultra-thin embedded silicon fan-out (eSiFO) package directly assembled on PCB for mobile applications." 2018 IEEE 68th Electronic Components and Technology Conference (ECTC). IEEE, 2018

6.Yu, Daquan. "Embedded Silicon Fan‐Out (eSiFO®) Technology for Wafer‐Level System Integration." Advances in Embedded and Fan‐Out Wafer‐Level Packaging Technologies (2019): 169-184.

7.Ma, Shuying, et al. "Progress and applications of embedded system in chip (eSinC®) technology." 2020 IEEE 70th Electronic Components and Technology Conference (ECTC). IEEE, 2020.

展出2万平米、1,000个摊位、500多家展商、50,000名专业观众;汇聚IGBT产业链上游陶瓷衬板(DBC/AMB)、散热器、焊料、烧结银等材料,超声波焊接、超声波检测、焊接等设备;精密陶瓷、电子陶瓷、陶瓷基板、陶瓷封装、LTCC/HTCC/MLCC加工产业链等产业链上下游企业!

观众预登记:

长按识别二维码,关注“艾邦陶瓷展”公众号,底部菜单进行观众预登记。

※功率器件(IGBT、SiC)IGBT、半导体封装、光通信,通讯设备、消费电子、电子陶瓷、元器件等企业可享受VIP参观福利(免费午餐、饮用水、赠送会刊);

※18岁以下未成年谢绝参观,请勿携带儿童进场!

原文始发于微信公众号(艾邦半导体网):华天eSiFO封装技术