背景技术

第三代半导体材料SiC(碳化硅)是由碳元素和硅元素稳定结合而成的晶体,具有宽禁带、高热导率、高载流子饱和迁移率等优越性能,在高功率、高频率、高电压等领域有着独特优势及广泛前景。SiC材料本身具有的这些优势使得SiC功率器件能够在目前大部分的功率器件应用范围内展现出足以取代Si基功率器件的潜力。

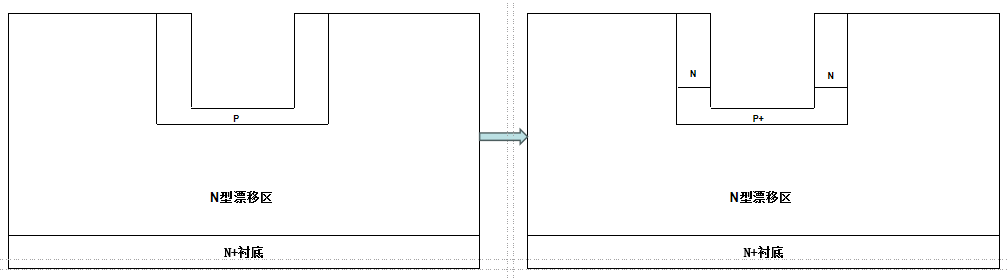

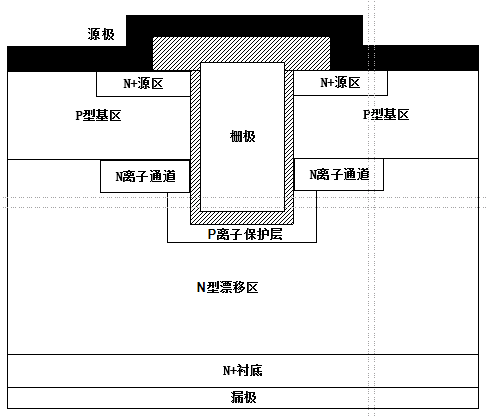

目前,SiC功率器件已经在650V~1200V电压等级的区间占有了一部分市场。其中SiC Trench MOSFET器件凭借导通电阻小、元胞密度大等优势成为SiC功率器件的研究热点之一。但由于沟槽的引入导致在栅氧化层拐角处容易集中极大电场,使栅氧化层被击穿,存在可靠性问题。因此本领域需一种新的SiC Trench MOSFET器件及其制备方法,以有效地保护沟槽底部的栅氧化层,提高器件的可靠性。

方案内容

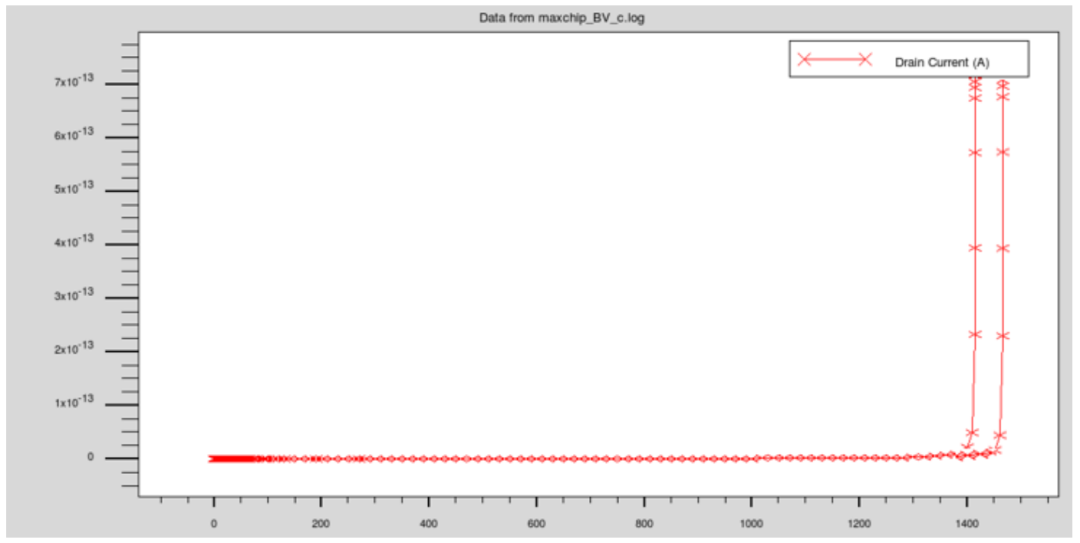

仿真数据

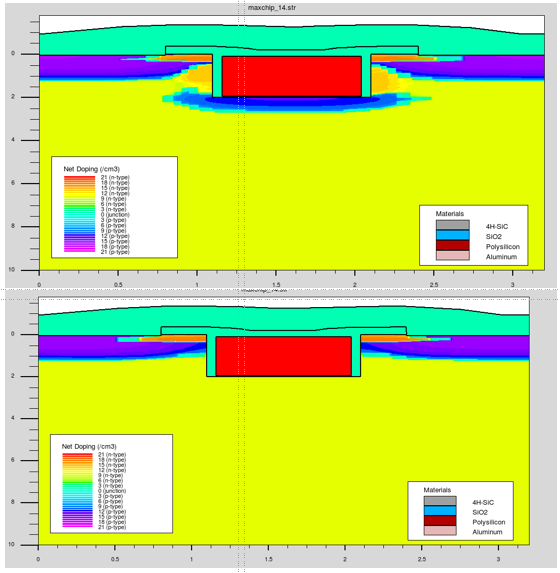

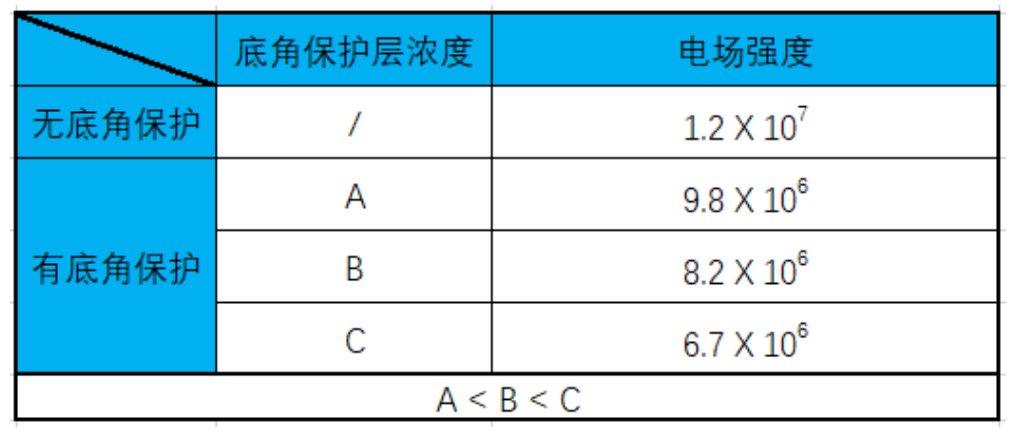

结构仿真后有进行电场强度分析,确认底角有P离子区保护的结构电场强度有明显的降低。并且通过提高保护层的P离子浓度可以进一步降低底角电场强度从而达到更好的保护作用,如图5所示。

△图5

END

原文始发于微信公众号(芯达茂微电子):「技术介绍」提高SiC Trench MOSFET可靠性的一种制备方法

应用终端 SIC IGBT模块 SIC模块 碳化硅衬底 IGBT芯片 分立器件 材料 焊接材料 真空回流焊炉 烧结银 烧银炉 烧结炉 陶瓷基板 铜底板 焊接设备 划片机 晶圆贴片机 灌胶机 贴片 表面处理 硅凝胶 环氧树脂 散热器 铝碳化硅 五金 键合机 键合丝 超声焊接机 陶瓷劈刀 激光设备 设备配件 PVD设备 ALD 电子浆料 CVD 导热材料 元器件 密封胶 X-Ray 配件 超声波扫描显微镜 塑胶外壳 玻璃 塑料 线路板 设备 散热材料 热敏电阻 点胶机 胶水 自动化设备 运动控制 封装设备 检测设备 认证检测 夹治具 清洗设备 测试设备 磨抛耗材 磨抛设备 代理 贸易 其他