Heraeus Electronic

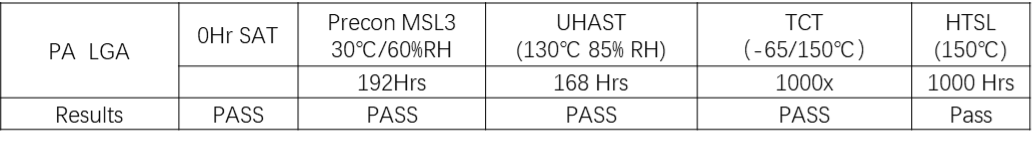

应用在通讯终端中的功率放大器 (PA,Power Amplifier) 已经成熟批量生产。随着电子设备朝高性能、小型化和封装成本的要求发展,高密度封装成为必然趋势。在这一背景下,DA295A 无压烧结银为高密度、高性能的封装(LGA/QFN) 提供了理想的 GaAs、GaN 芯片与基板互连解决方案。

高密度封装指在一条基板上会有 2000 到 3000 颗独立的芯片。这种封装在 die bond 过程中通常会面临点胶/画胶的稳定性、RBO(树脂溢出)、open time(点胶到装芯片的停留时间)以及银膏覆盖率的挑战。贺利氏研发团队通过修改配方和工艺流程等方案克服了这些挑战。

- 画胶图案:Double Y

- 画胶速度:70% (ESEC 2100)

- 画胶压力:0.85 bar

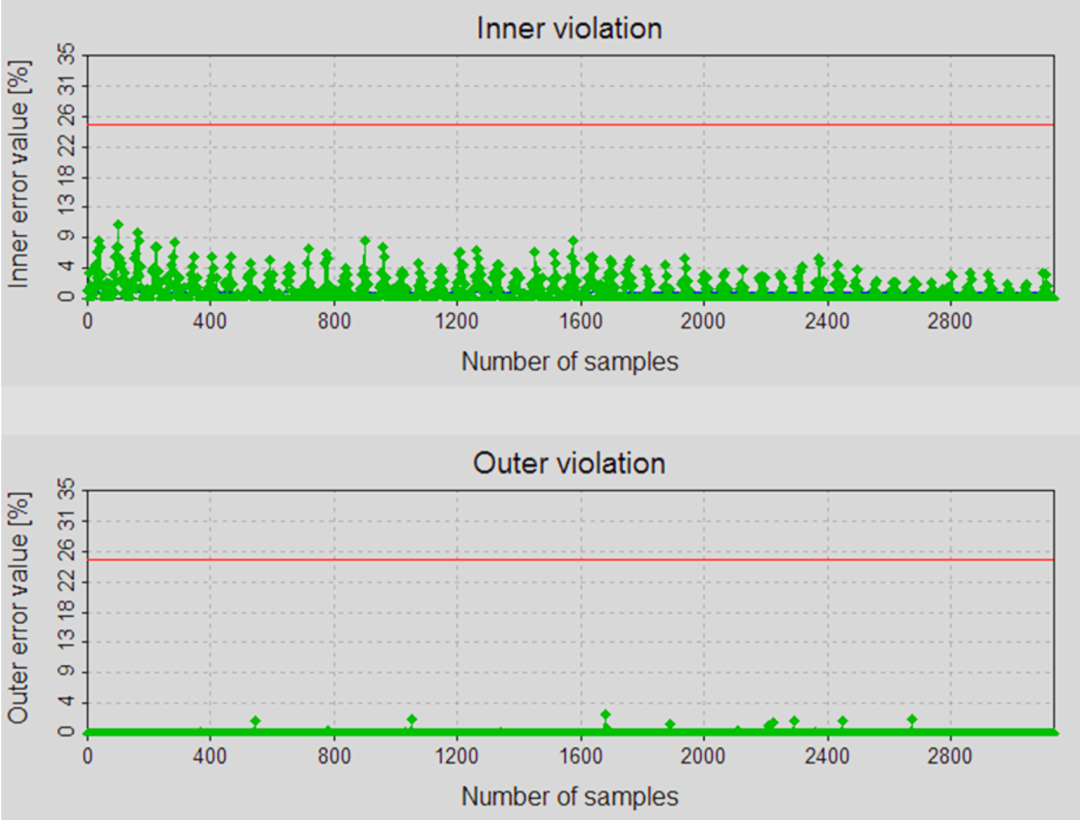

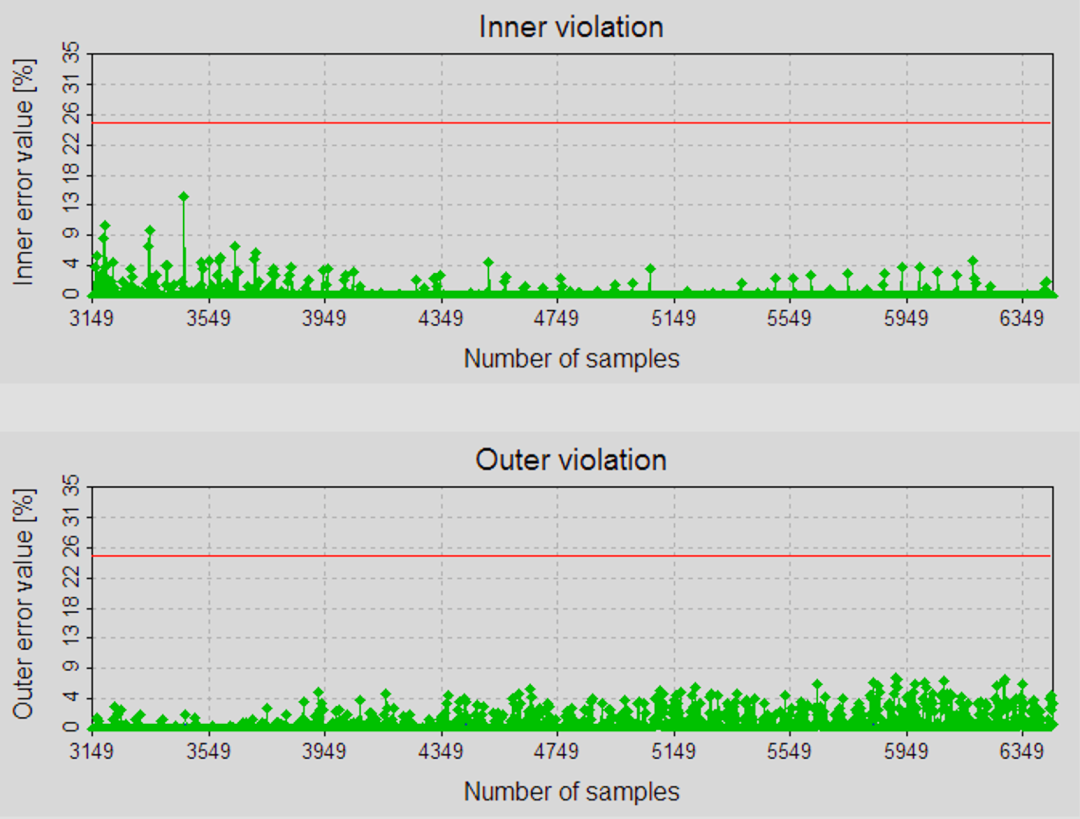

产品结构:高密度基板,一条基板有3200多颗GaAs芯片需要贴装。

测试方法:使用相同的参数连续画胶

判断标准:基于ESEC2100对胶形的检测,客户设定的规格胶型变化<25%

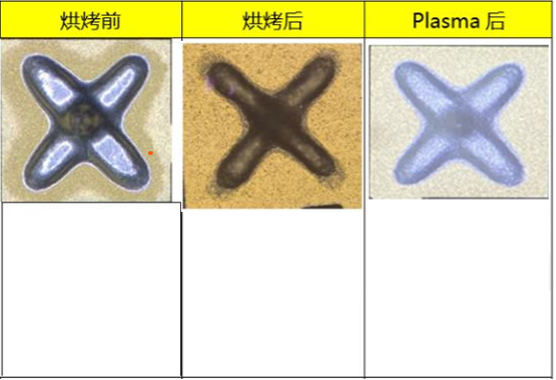

RBO(树脂溢出,Resin Bleeding Out)在烘烤过程中无法去除,也无法在wire bonding前的等离子清洗中完全清除,因此对打线和封装会产生一定影响。

贺利氏的ASP/DA295系列产品均采用无树脂添加的溶剂配方体系,即全烧结配方体系(烧结完成后无残留树脂成分)。溶剂配方体系通常使用沸点较低的溶剂,在烘烤过程中达到沸点后溶剂将会挥发掉。

在实际实验中,不同的基板DPAD表面处理会导致不同程度的溶剂溢出,如下图所示。图3-1展示了较少的溶剂溢出,而图3-2则显示了接近100%的溶剂溢出。

溶剂溢出(Solvents bleeding out)在烘烤前后和等离子清洗后我们做了对比测试,如表1所示:

*备注:显微镜的灯光影响了照片的颜色

选用常见芯片尺寸(mm):0.74*0.70

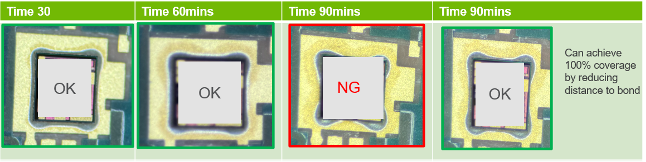

测试条件:使用相同的画胶参数以获得一致的胶量,在同一时间画胶,根据不同的时间间隔使用相同的参数进行贴装芯片。

判断标准:在BLT(Bond Line Thickness)在20~30um内,银膏覆盖率达到100%。

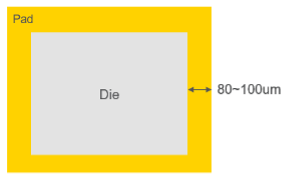

高密度封装意味着在当前标准的基板尺寸内排列更多的个体单元,即减小焊盘尺寸压缩芯片的贴装面积。

在高密度封装中,芯片边缘到焊盘的距离变得更小,例如有些产品设计了80~100um的距离,如图5所示。

测试方法:通过控制画胶图案的尺寸和装片的高度,在装片时控制银膏的溢出。

检测方法:在显微镜下检查芯片底部银膏覆盖。

判断标准:银膏覆盖率达到100%,且没有超出焊盘。

● 改善版的DA295A具有稳定的作业性。

● 溶剂体系的配方在烘烤后溢出的溶剂能够挥发掉,不会对打线键合产生影响。

● 较长的open time能够满足高密度封装的需求,避免分段式作业。

● 能够解决紧凑型设计的银膏覆盖率问题。

原文始发于微信公众号(贺利氏电子):技术博客|适用于高密度封装的无压烧结银方案