芯片焊接失效模式与焊接空洞

失效模式分析

2025

芯片焊接强度受多种因素影响,涵盖焊料、工艺条件、管壳衬底质量以及芯片背面的粗糙度和洁净度等。对于气密封装的集成电路而言,把控电路内部气氛、确保封装腔体内维持较低水汽含量至关重要。

芯片焊接的直接失效模式主要包含以下两种:

芯片脱落:芯片从粘片区域或腔体内脱离。这属于严重的失效情形,会致使集成电路完全丧失功能。引发芯片脱落的因素主要有芯片背面洁净度、粗糙度,芯片背面金属化层质量,以及烧结工艺等。

焊接空洞:在合金烧结时,空洞的产生难以避免。若空洞率过高、空洞面积过大,会增大器件热阻,降低可靠性,还会增加芯片碎裂、脱落的可能性。影响粘接空洞率的主要因素有烧结过程中焊料的浸润性、粘接面的洁净程度以及烧结工艺等。

间接致使密封失效的模式主要是内部水汽含量超标:电路封装后,若腔体内气氛超出 GJB 548B - 2005 规定的水汽含量小于 5000ppm 标准,就会导致功能失效以及贮存寿命缩短等问题。不合格原因主要包括半成品电路吸附水汽、芯片粘接或焊接材料挥发有害气体、封盖工艺气体纯度不足等。

芯片脱落失效原因及应对措施

2025

1.背金前硅片存在杂质及氧化层:若背面金属化前采用有机溶剂清洗,虽能去除有机杂质,但可能因冲水不彻底,使溶剂自身成为新的污染物。硅片减薄后,在有机溶剂漂洗过程中产生的自然氧化层,同样会对芯片质量产生影响。可选用适当比例的 HF 去除硅片背面在此期间生成的自然氧化层,露出新鲜的硅表面,以保障金属与硅片充分粘结,确保背金质量。

2.金属化层与硅的粘附性欠佳:现有的 Ni - Au 结构中,Ni 兼具粘附层和阻挡层的作用,当 Au 与焊料发生反应生成合金后,会粘附在 Ni 层上。采用 Ti - Ni - Au 三层金属进行背面金属化,能够提升背面金属与硅的粘附性。多层金属化结构还可兼顾芯片与焊料之间的机械强度和电学性能,提高器件的热疲劳寿命。

3.硅片背面过于光滑或粗糙:减薄时,若芯片背面过于光滑,不利于增大焊料与芯片的接触面积;若过于粗糙,则不利于焊料浸润。可通过背面腐蚀改善硅片背面粗糙度,提高芯片粘接强度。

4.芯片背面被污染:芯片在传递过程中可能会被污染,影响焊料的浸润性。因此,有必要进行有效的超声清洗和等离子清洗,并严格检查,以确保芯片粘接前的表面状态良好。

5.背金未熔化:对于大面积芯片电路,容易出现管壳温度低于焊料共晶温度的状况。在此情况下,焊料虽能熔化,但没有足够温度扩散到芯片背金层,造成局部冷焊。优化温度曲线,充分预热,可使热容较大的管壳与芯片处于等温状态,提高焊接质量。

粘接空洞失效原因及采取措施

2025

1.焊料浸润性差:浸润性优劣直接关乎焊料的流淌特性以及焊接强度。浸润性能良好时,可有效减少空洞,增强焊接强度。我们选用的铅铟银焊料属于软焊料,能轻松与含金界面结合,且使接面具备更强的延展性与出色的耐疲劳寿命。依据实际需求,焊料面积设定为芯片面积的 90%,厚度保持在 50um。当焊料浸润性欠佳时,一方面意味着焊料与芯片背面接触面积较小;另一方面表明浸润液体边缘所受界面张力较大,阻碍了焊料的铺展。此时,对芯片施加一定正压力,在焊料熔化时能抗衡表面张力,增加焊料与芯片背面的接触面积,提升浸润性,扩大接面面积和接强度。

2.焊料表面氧化层:若焊料存放时长过久,其表面会生成过厚氧化层。倘若焊接过程中无人工干预,该氧化层极难去除,焊料熔化后形成的氧化膜在焊接后会产生空洞。为解决此问题,焊料需进行真空防氧化处理,并抽真空保存;运用等离子清洗技术对焊接表面进一步清洗,清除材料表面杂质,最大程度降低管壳、焊料、芯片的氧化程度;在真空环境下开展共晶焊接,可防止焊接时产生氧化物,同时若在焊接过程中充入甲酸气体等还原性气体,还能还原焊料中已形成的氧化膜,进而减少空洞,提高焊接质量。

3.焊接表面颗粒及粘污:在焊接期间,若使用的管壳不洁净,或者芯片背面遭受污染,会致使焊接时焊料无法充分扩散,产生空洞,影响焊接成效。所以,管壳、芯片、片在焊接前需严格处理,去除材料在加工和传递过程中沾染的污染物。采用超声和等离子清洗,能够有效去除材料表面的颗粒、有机粘污和离子沾污。

4.焊接时气泡未排出:焊接时,焊接区周围的气体以及焊接材料释放出的气体,在焊接后容易形成空洞。通过优化烧结工艺曲线,在焊料充分熔化浸润后,增加抽真空排气环节,尽可能排出气泡,减少空洞产生。

内部气氛不合格原因及采取措施

2025

1.封装材料释放:在对有害气氛来源深入剖析后,针对性地拟定解决办法。对管壳实施预烘烤操作,能够有效减少腔体内氢气含量;利用等离子清洗技术处理焊片表面,去除焊片表面的碳酸铅及其他氧化物,从而进一步降低内部二氧化碳含量。

2.半成品电路吸附水汽:因水分子具有亲和力,水汽极易在管壳腔体或芯片表面吸附,进而形成一层水分子膜。特别是封装管壳的内表面较为粗糙,存在凹凸不平的情况,凹陷处对水分子的吸附力远超过平面处,所以在表面凹陷处水分子容易聚集。为解决管壳和芯片表面吸附的水汽问题,电路在封盖前需进行预烘焙等高温烘烤,以此去除表面吸附的水汽。

3.封盖工艺气体含杂质:为严格把控水汽含量,要求在封装过程中,在高纯氮气的气氛下进行封盖,以此解决因环境因素导致的水汽含量超标问题,即封装气氛采用高纯氮气。同时,还需依据设备特性设置适宜的氮气流量,维持管道内的正压力。

焊接空洞

2025

1.焊接空洞的标准

焊接空洞具体是指,在焊料与母材相互接触的界面位置,存在未能被焊料充分浸润的空隙;或者在焊料自身内部,出现了空洞情形。导致空洞缺陷产生的原因是多维度的,主要涵盖残留气体、材料表面的氧化状况、表面是否受到污染、焊剂残渣留存,以及母材表面的粗糙程度等因素。

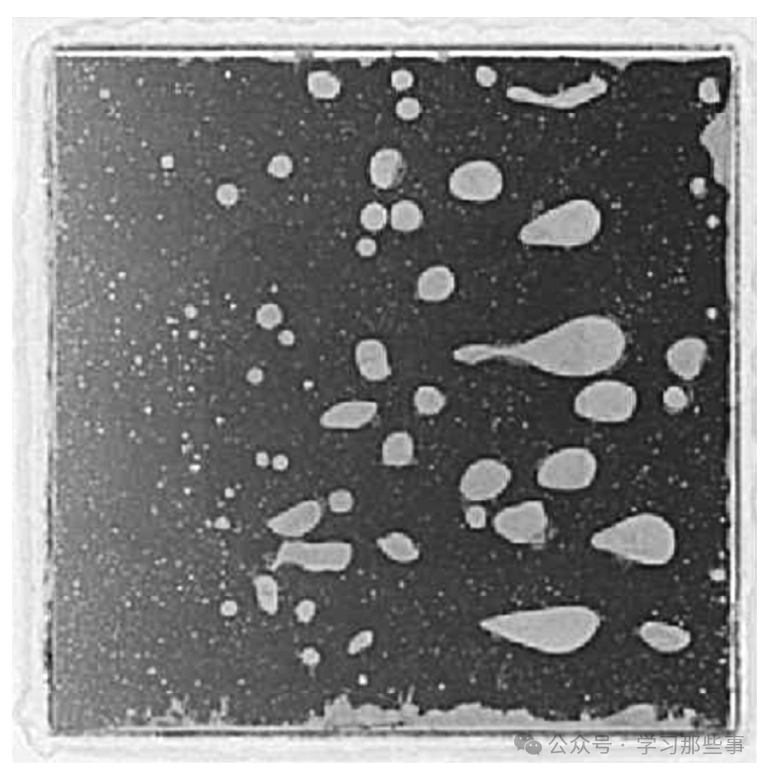

空洞率是空洞面积与芯片面积的比值。在焊接质量检验环节中,检测焊接空洞率是一项关键任务。当前,常用的空洞率检测方法主要是 X 射线照相检查方式,也有部分情况会采用超声检测技术来观察空洞情况。一般来说,在高可靠性要求的电路里,通常规定芯片空洞率需小于 50%;而对于航天专项工程所涉及的电子元器件,其标准要求更为严格,空洞率必须小于 25%。图 1 展示的便是焊接空洞通过 X 射线照相观察所得到的结果。

图1:焊接空洞的X射线照相观察结果

2.氧化对空洞的影响

部分研究人员选取了保存状态良好的 IGBT 散热底板以及已被氧化的散热底板,开展焊接空洞率的对比实验。在保持其他各项实验条件均不变的情况下,通过对空洞进行超声扫描检测,结果显示:当散热底板发生氧化后,在使用 SnPbAg 焊料片进行焊接的样品中,空洞率范围从原本的 0.24% - 1.57% 增长至 0.78% - 6.64%;最大空洞面积占焊接区域的比例范围,也从 0.04% - 0.33% 上升到 0.04% - 0.64% 。由此可见,焊接母材一旦发生氧化,会使焊接空洞率以及最大空洞面积范围的上限数值大幅增加。

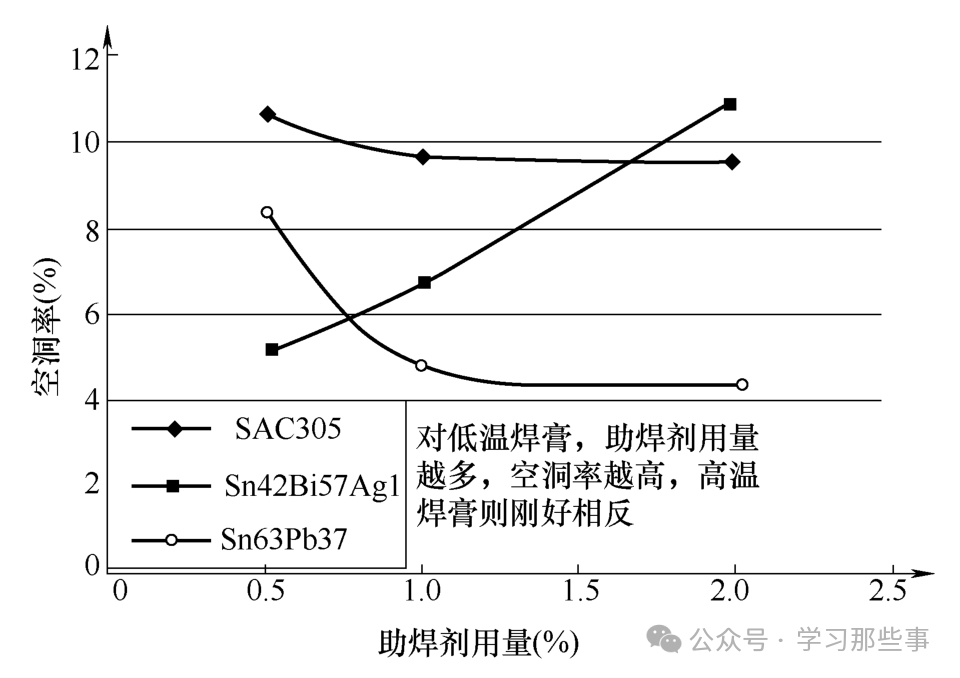

3.助焊剂选型与空洞

在集成电路封装过程中,大多数焊料在使用时无需额外添加助焊剂,然而助剂在器件的表面贴装工艺中应用广泛。有研究人员选用 SAC305、Sn42Bi57Ag1、Sn63Pb37 这三种不同类型的焊料,用于焊接已被氧化的芯片,并选用专门为 SAC305 焊料研制开发的助焊剂来去除氧化层。图 2 展示出助剂用量与焊接空洞之间的关联,从中可清晰看到焊接后的空洞率测量数值。从图 2 中可知,针对 SAC305 开发的助焊剂,随着其用量的逐步增加,对于降低高温焊料产生的空洞问题有显著帮助;但对于低温焊料而言,却产生了相反效果。所以,只有选用与焊料相匹配的助焊剂,才能切实有效地减少空洞的产生。

图2:助焊剂用量对焊接空洞的影响

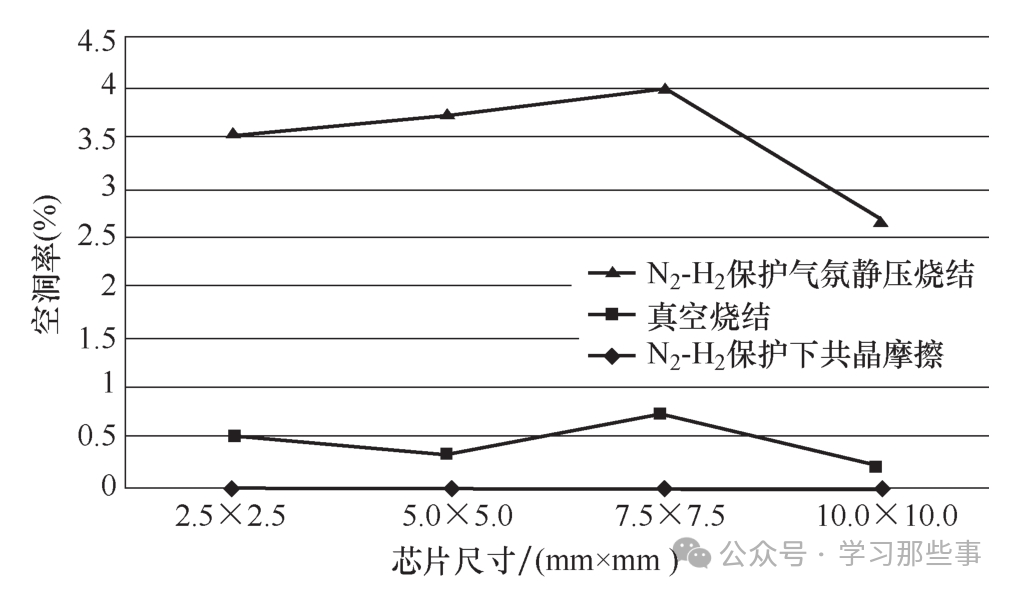

4.焊接工艺与空洞率

图3呈现的是焊接空洞随焊接方式和芯片尺寸的变化趋势。从中能够清晰地观察到 Au - Si 共晶摩擦焊、Au - Sn 焊料真空烧结以及 Au - Sn 焊料保护气氛下静压烧结这三种焊接方式,对空洞率产生的影响。同时,还可以了解到芯片焊接面积增大后,焊接层中空洞率以及单个最大空洞尺寸的变化走向。

研究结果表明,对这三种焊接方式进行比较,空洞率由低到高依次为:Au - Si 共晶摩擦焊<Au - Sn 真空烧结<Au - Sn 保护气氛静压烧结,其中共晶摩擦焊接的空洞率最低。值得注意的是,对于不同尺寸的芯片,这三种工艺方案均呈现出相同的趋势。此外,随着芯片面积的增大,单个最大空洞的面积也呈现出增大的态势。

图3:焊接空洞随焊接方式和芯片尺寸的变化趋势

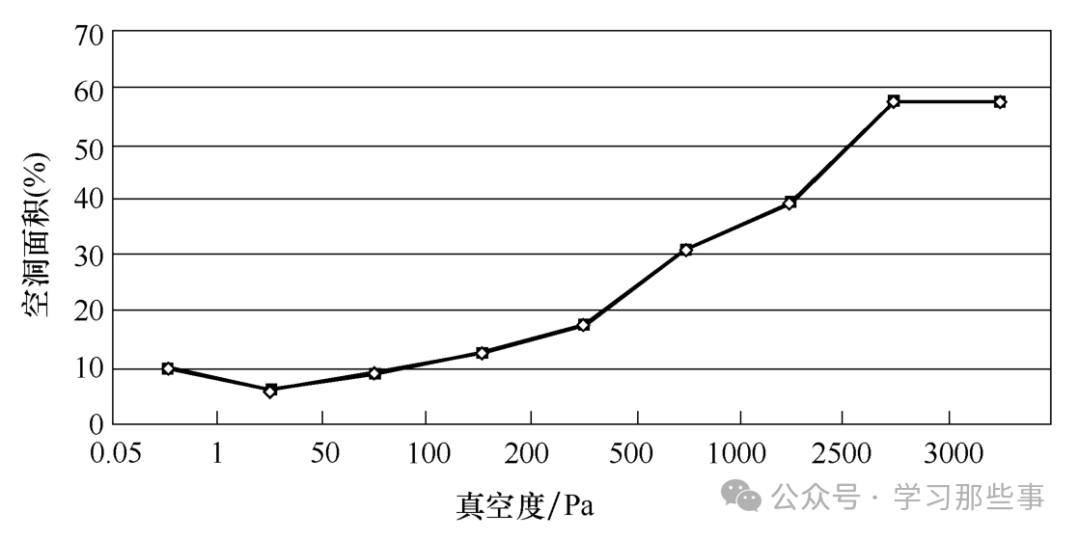

5.真空度与焊接空洞

真空度和保护气氛是影响共晶焊接质量的关键因素。有研究人员针对烧结过程中抽真空的真空度对焊接空洞的影响展开了专项研究。图4展示了真空度与焊接空洞率的关系。从图中可以发现,随着真空度的升高,共晶焊的空洞面积呈递减趋势,当真空度达到 1Pa 时,其空洞面积接近最小,之后随着真空度继续升高,空洞面积趋于平稳状态。经试验确定,共晶焊接的真空度至少要达到 1Pa。

图4:真空度与空洞率的关系

原文始发于微信公众号(学习那些事):芯片焊接失效模式与焊接空洞