随着科技的不断进步, 人工智能、物联网、汽车电子等新兴领域市场快速发展,带动了全球封装测试产业的持续增长;集成电路封装是半导体芯片制造的后道工序,是实现芯片功能、保障器件系统正常运行的关键环节之一。

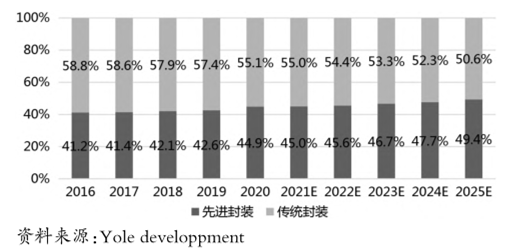

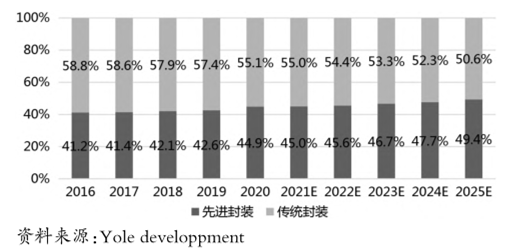

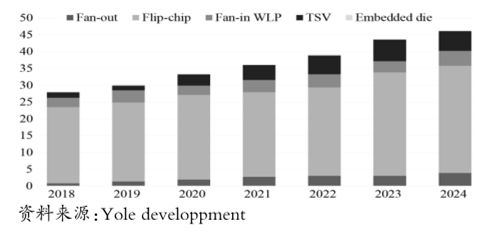

全球半导体封装测试市场未来将会在传统工艺保持较大比重的同时,继续向着小型化、集成化、低功耗方向发展,而附加值更高的先进封装将得到越来越多的应用,据市场研究机构 Yole Developpement 的预测,全球先进封装市场将在 2019-2025 年实现 6.6%的复合增长率,封装测试业市场有望持续向好。

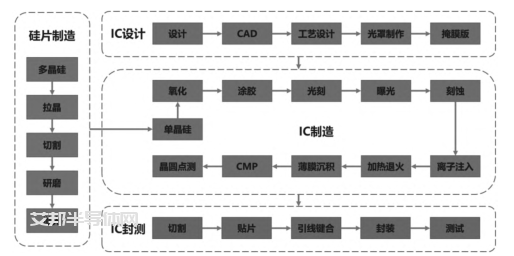

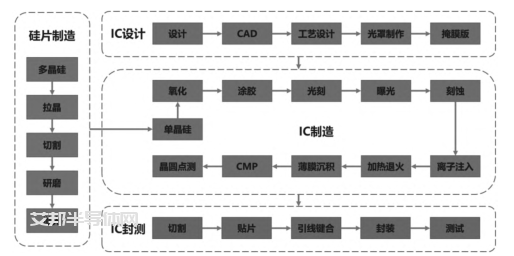

集成电路工艺流程

01 第一阶段是 80 年代之前的元件插装,特点是用针脚引出电极连通电信号,主要包括直插型封装(DIP)等技术;

02第二阶段是 80 年代中期的表面贴装,特点是用更细更短板的引线代替针脚,直接贴装至印刷电路板(PCB),主要包括小外形封装(SOP)等封装技术;

03第三阶段是90 年代的面积阵列封装,特点是用体积更小的焊球点代替引线,通过芯片倒扣的方式进行倒装,提升封装密度,主要包括球栅阵列封装(BGA)、芯片尺寸封装(CSP)、倒装芯片(Flip Chip)等封装技术;

04第四阶段是 2000 年以来的先进封装,特点是采用堆叠、异质整合(指将不同类型、功能的芯片整合在同一封装体内)等技术,主要包括晶圆级封装(WLP)、硅通孔(TSV)、2.5D 封装、3D 封装、系统级封装(SiP)等封装技术。应该看到,先进封装以“更高效率、更低成本、更好性能”为主要目标,以“小型化、轻薄化、窄间距、高集成度”为主要特征,能够提高设计、加工效率,减少设计成本,是未来封装技术发展的主要方向。

01晶圆级封装在更小的封装面积下容纳更多的电极引脚数量,满足“窄间距、高密度”的封装要求;

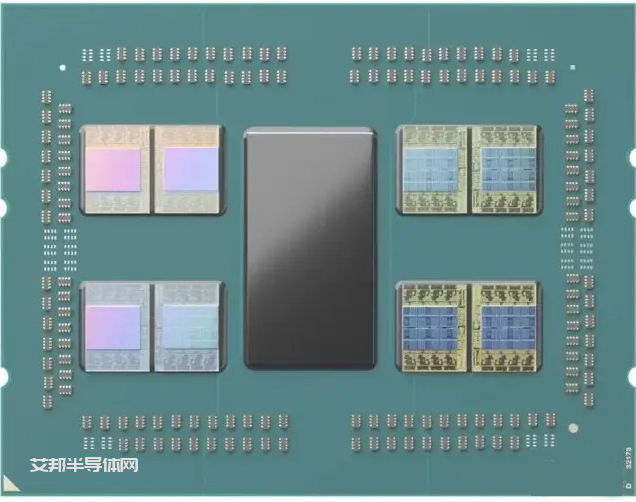

02系统级封装通过封装整合多个独立功能的芯片于一体,实现体积微缩,提升芯片系统整体多功能性和设计灵活性。特别是近年来 Chiplet 技术受到广泛关注,利用先进封装技术将多个异构芯片的裸片整合集成为特定功能的系统芯片,是先进封装技术发展的又一突破,有望推动异质整合成为未来芯片设计的主流。

近年来,随着市场需求增加,全球半导体封装规模明显增长,据市场研究机构 Yole developpment 的数据,2021 年全球封装市场规模约达 777 亿美元,2025年有望将达到 850 亿美元。

在此发展过程中,先进封装价值得到日益显现,并成为全球竞逐的焦点:随着国际代工模式的兴起,封装行业迎来了良好的发展机遇,2021 年全球先进封装市场占比达到整体集成电路封装服务的 45%,年营业收入约为 350 亿美元。

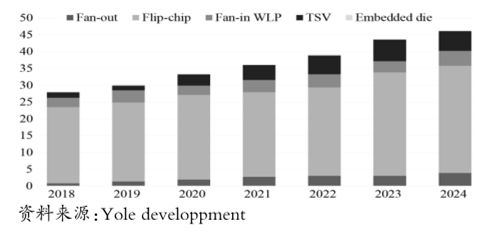

倒装芯片技术市场比重将长期维持较高份额,包括晶圆级封装技术(包括Fan-out技术)、硅通孔、系统级封装等封装技术未来增长空间广阔。

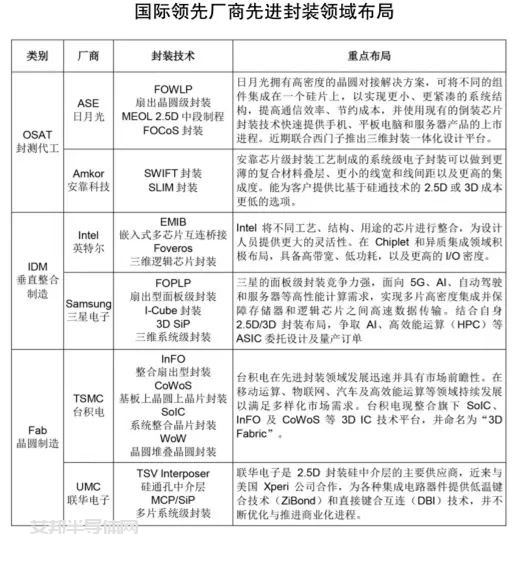

纵观全球封装市场,亚太地区已经成为全球集成电路封装测试业的产能集聚地,并吸引了半导体整体产能的转移。随着全球封装业的资源协同,先进封装业转向技术输出,从目前全球半导体行业的趋势来看,发展先进封装势在必行。

摩尔定律自从 7nm 工艺节点以后发展速度放缓,故封装行业价值受到更多的重视。先进封装的发展趋于多功能化和系统化,异质整合(HI)的不断发展,晶圆级封装、系统级封装等技术逐步成为行业关注的焦点。异质整合可将不同工艺节点的裸 Die(晶粒)通过 2.5D/3D 堆叠技术封装在一起,成为芯片封装的新趋势;尤其是,近年来具备模块化、定制化的优势的 Chiplet 模式得以兴起,推动了晶圆级封装技术的发展,使得设计、制造与封装成本大大降低;在5G 的高速发展过程中,针对终端设备小型化的趋势,减缓信号传输中的衰减问题,带来了天线与射频前端模块一体化集成的 AiP(封装天线)技术,有助于推动系统级封装的发展。

未来,封装的发展方向可能不再局限于以往单独代工环节,而是与设计、制造、材料设备相结合的一体化解决方案,集成电路前后道工艺融合发展趋势日益明显。

主要驱动力表现在:一是随着先进封装技术的不断发展,特别是晶圆级封装产业规模的不断形成,与芯片设计、制造业的协同发展显得更加重要。二是晶圆级封装的出现模糊了晶圆厂和封装厂之间的界限。

Chiplet 通常是通过高级封装集成,以及基于标准化接口使用。它在引领先进封装技术发展方面,一是可能带给从上游 IC 设计、EDA 工具、制造、先进封装等各个产业链环节颠覆式的改变。二是Chiplet 或可催生封装行业的“IP 核”,进而将半导体 IP 核扩展至全链条,并进行深度封装架构与标准化接口设计。

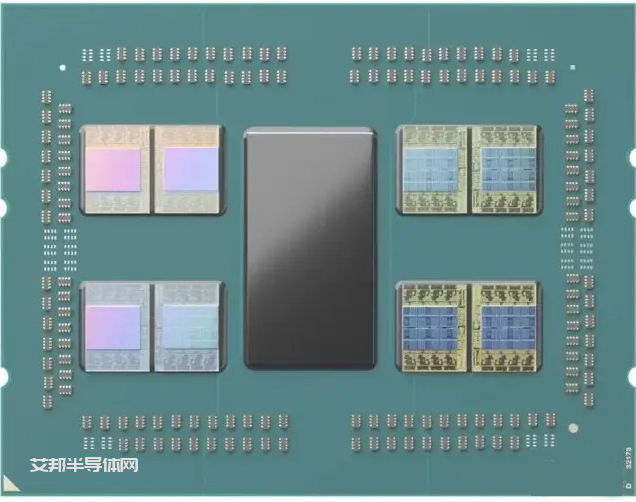

随着半导体工艺尺寸进一步缩小,集成电路制造面临的挑战日益增大,摩尔定律日趋放缓,所以Chiplet概念应运而生,Chiplet就是通过工艺的改进来解决“摩尔定律”失效的一种方法,Chiplet走向了和传统的片上系统(SOC)完全不同的道路,类似于搭建乐高积木,通过一组小芯片混搭成“类乐高”的组件。Chiplet技术是SoC集成发展到一定程度之后的一种新的芯片设计方式,它通过将SoC分成较小的裸片(Die),再将这些模块化的小芯片(裸片)互联起来,采用新型封装技术,将不同功能不同工艺制造的小芯片封装在一起,成为一个异构集成芯片。

后摩尔时代,单片同质集成向三维多片异构封装集成“改道”是重要趋势,缘由在于:因为三维多片异构封装可以提供更高的带宽、更低的功率、更低的成本和更灵活的形状因子 。实现多片异构的方式有多种,如在 2.5D 封装中,所有晶片朝下,依靠Interposer (硅中介层)做 TSV;而 3D 封装更为复杂,是依靠在硅晶片上直接做 TSV,目前仍依靠 SiP 在硅片和中介层做 TSV 硅通孔,未来的发展趋势是整颗 IC 都应用 3D 封装技术。

就 Chiplet 而言,多片异构所需的互联技术引起了更大的关注,不但带来了新的总线技术(如Intel 的 AIB 技术和 AMD 的 Infinity Fabric 技术),还对封装过程中的信号传输保障提出了更高的要求。例如,在 SoC 中的 SerDes (串行 / 解串)技术和 NoC(片上网络)技术在 Chiplet 应用中将扩展至三维,并得到高频应用。未来,IC×AI×HI (集成电路加乘人工智能与异质整合)是全球半导体技术重要发展方向,先进封装将是实现异质整合、不可或缺的关键技术。

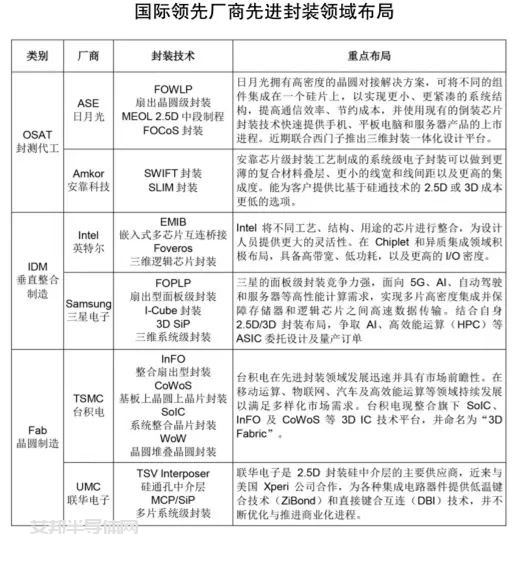

先进封装测试领域已成为全球半导体行业竞逐的关键,Chiplet 技术、异质整合等产业模式的兴起和发展已向我们描绘了未来封装领域的发展蓝图。半导体前道和后道工序加速融合,先进封装成为行业关注焦点,晶圆代工厂、IDM 厂商涉足先进封装业务,并将重塑半导体行业竞争格局。技术创新将成为驱动半导体技术向前发展的关键。

未来,借由先进封装技术,集成电路有望通过异质异构系统集成提升密度和性能、实现功耗降低、集成更多功能。在数字化、低碳环保、消费电子轻量化等趋势的推动下,先进封装正在迎来广阔的发展空间。封装行业的发展涉及半导体产业链的方方面面,在封装行业不断发展的过程中,营造良好的产业发展生态,构建健康的产业发展体系至关重要。

原文始发于微信公众号(无锡昌鼎电子有限公司):先进封装|推动半导体产业发展新格局