点击上方导电高研院| 关注我们

CEIA电子智造的朋友们大家晚上好,我是来自奥肯思公司的李扬,这么多年以来,我一直醉心于半导体先进封装的技术研究,今天要讲的题目是先进封装的设计和验证,Design and Verification,此外,接下来我将在天空沙龙开设专题课程,详细讲述半导体先进封装的相关工艺和前世今生,期待各位的关注。

今天要讲的议题分为9个部分,首先了解一下先进封装技术,再介绍一下主流的先进封装技术,重点在2.5D和3D先进封装的设计方法,以及2.5D和3D的设计实例,最后了解一下先进封装的仿真方法、先进封装的电气验证、先进封装的物理验证,最后给出总结。

我们首先看一下,关于先进封装技术的概览。

什么是先进封装?先进封装就是采用先进的设计思路和先进的集成工艺、对芯片进行封装及重构,并且能够有效提高系统功能密度的封装。我们注意看,这里面有几个关键词,一是先进的设计思路,第二就是先进的集成工艺,第三是封装及重构,还要能够有效地提高系统的功能密度。

为什么要强调这几个关键词?大家知道,封装以前只是配角,是芯片制造过程中一个不太起眼的步骤,但到了先进封装阶段后,它的重要性好像突然就提高了,为什么会有这样的转变?其中非常重要的一点就是,它是在封装级别对系统的功能进行了重构,实际上就是在封装级别功能有所改变,通过先进封装技术后,因为多个芯片集成在一起,功能就会发生变化,实际上就形成了一个系统,这对产品功能来说是非常重要的。

我之前就曾经说过,先进封装是一个相对的概念,可能过了几年,我们现在称之为先进的技术就不再先进了。现阶段,先进封装主要指的是倒装焊(Flip chip)、晶圆级封装、2.5D封装和3D封装,这些技术分别具备各自的特征,比如说倒装焊还有Bump、RDL,晶圆封装的特征是Wafer和RDL,2.5D是RDL+TSL,3D封装的主要特征就是TSV。

倒装焊这种技术实际上出现的时间比较久了,先进性不如其他几个。另外就是晶圆级封装,大多数是单芯片的,比如说Fan out或者Fan in都是单芯片的,这样复杂性就不是很高。所以先进封装的难点在于2.5D和3D,今天重点分享 2.5D和3D封装的设计和验证,因为相对而言,2.5D和3D的难度更高。

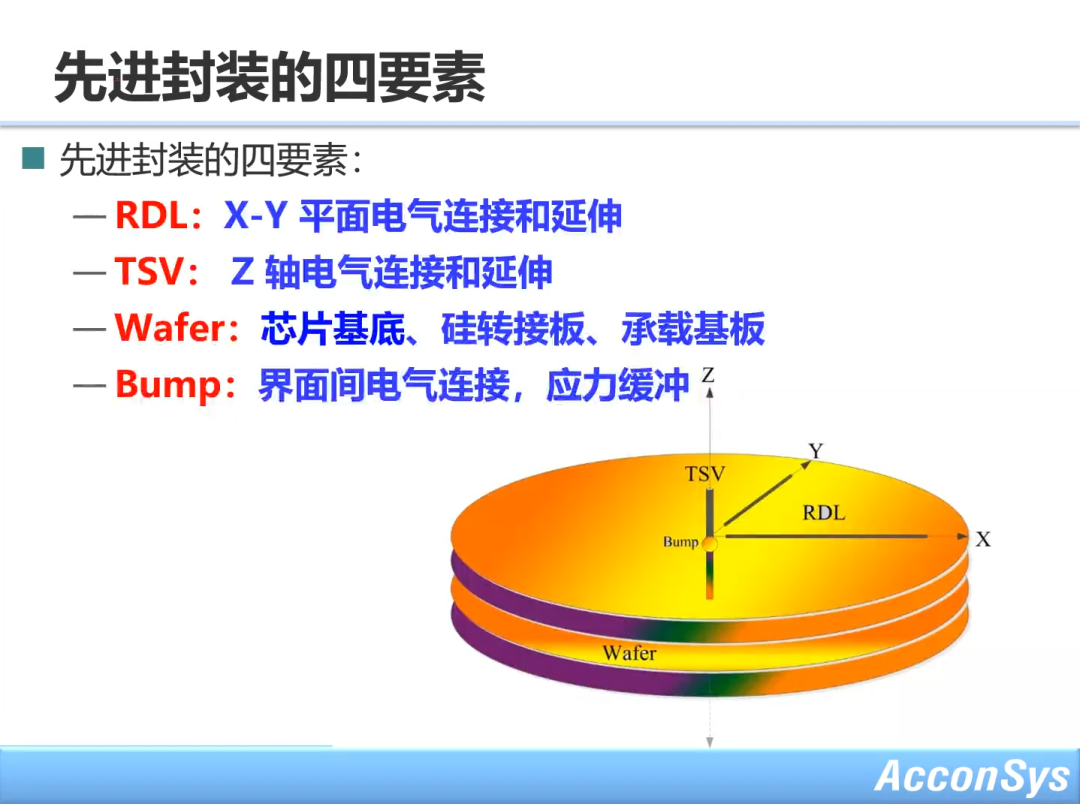

这里我们了解一下先进封装的四要素,我总结了,就是RDL、TSV、Wafer、Bump,主要是对X-Y平面进行电气连接和延伸。TSV主要是对Z轴进行电气连接和延伸,Wafer是芯片基底,也可以作为硅转接板,在晶圆级封装里面承载的基板,Bump是界面间的电气连接,起着电气连接和应力缓冲的作用。如上图,就分别表明了Bump、RDL、TSV、Wafer所处的位置,现在我看到很多文章也在引用它,所以业界还是比较认可这种四要素的提法。

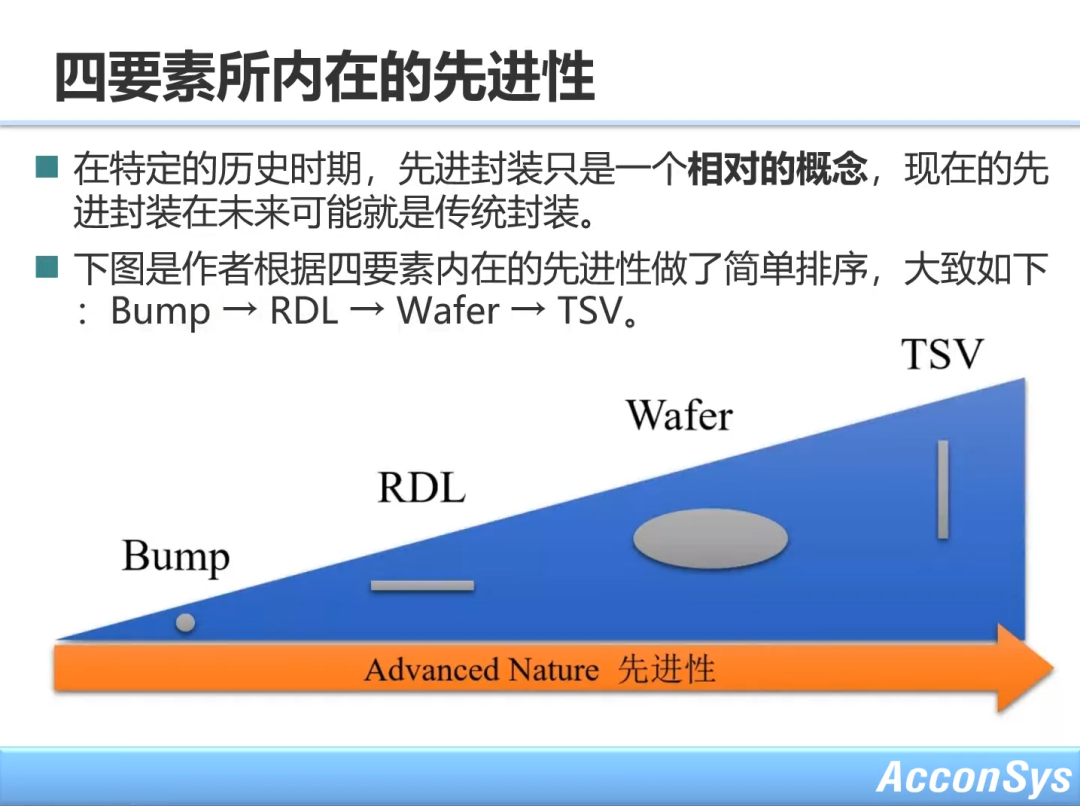

我刚刚也说过,先进封装是相对的概念,现在的先进封装在未来可能就是普通封装或者传统封装,我这里对先进性进行简单的排序,Bump出现得比较早,排在先进性低的位置,出现得越晚,表明先进性越高。

比如Bump,现在它就不是很先进,在未来,它可能会逐渐消失,但是RDL、Wafer和TSV这三个要素是不会消失的,这三者起到延伸和承载的作用,而Bump主要是起到的缓冲作用,在界面之间,所以它可能会消失。

这里我列举了先进封装四要素的发展趋势,其中Bump会越来越小直至消失,被混合键合等技术所取代,Hybrid Bonding。而RDL会越来越小,但不会消失,可能会变得越来越细,起着X-Y平面的连接和延伸的作用,RDL以后就可能会小到微米以下。TSV也会越来越细小,但不会消失,因为它起着Z轴连接和延伸的作用,只要有延伸的作用就不会消失,因为在空间上有延伸,是不会消失的,TSV未来在每平方毫米(比芝麻粒还要小的空间)可以多达百万量级,就是一平方毫米连接的TSV可能达到100万个,非常惊人。Wafer会变得越来越大,直到其物理极限。现在看到的Wafer从最初的6英寸、8英寸、12英寸、18英寸,目前来说主流的还是12英寸,当然,下一步可能会开发18英寸的Wafer。

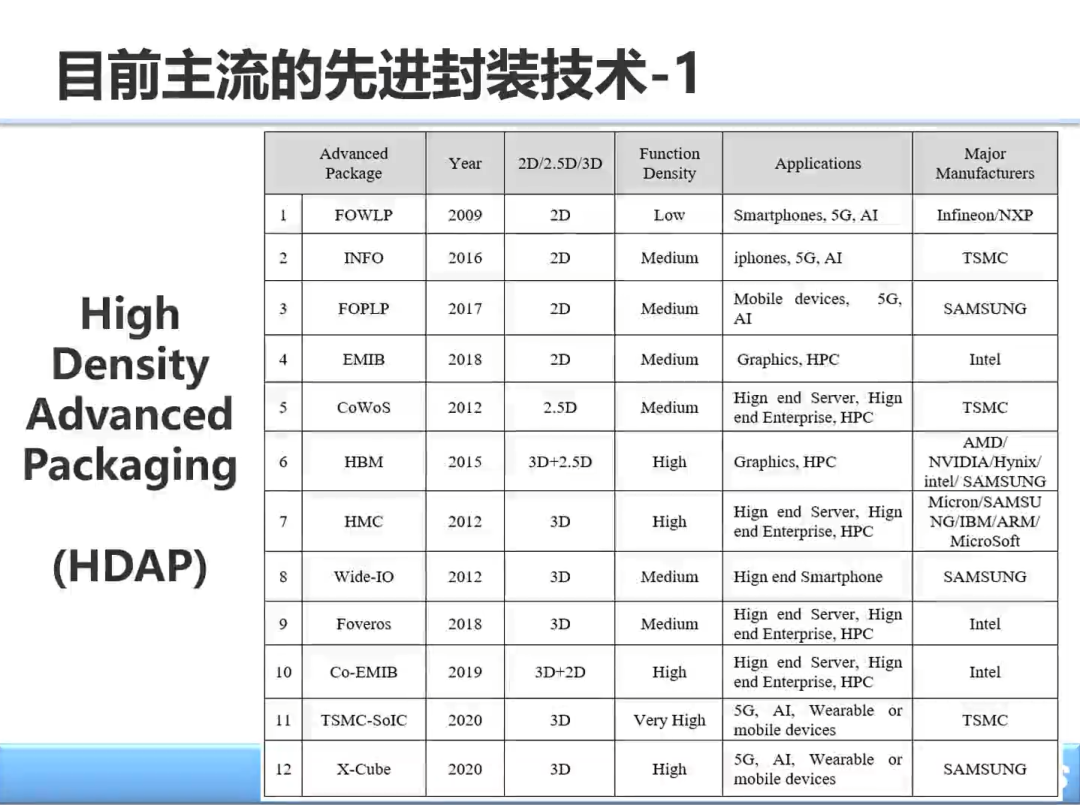

接下来我为大家总结12种主流的先进封装技术。

在这个表里面,大家可以看到是,Fan out Wafer Level Package是09年出现的,INFO是16年,Panel Level Package、CoWoS是12年,所以CoWoS实际上技术难度要比INFO要大,但是CoWoS出现的时间实际上比INFO要早,都是台积电提出来的。HBM、HMC、Wide-IO、Foveros、Co-EMIB、TSMC-SoIC是密度非常高的一组,TSMC-SoIC和X-Cube都是2020年提出来的,分有2D、2.5D,有2.5D+3D的,也有2D+3D的,工作密度有低、高、极高,特别SoIC非常高,应用的领域从智能手机、5G、AI到高性能计算等,都有。

有趣的是,这些技术主要集中在比较著名的集成电子厂商内,TSMC(台积电)、三星、Intel、AMD、英伟达等,在先进封装领域,封装厂商反而好像没有集成电子厂商这么激进和活跃。

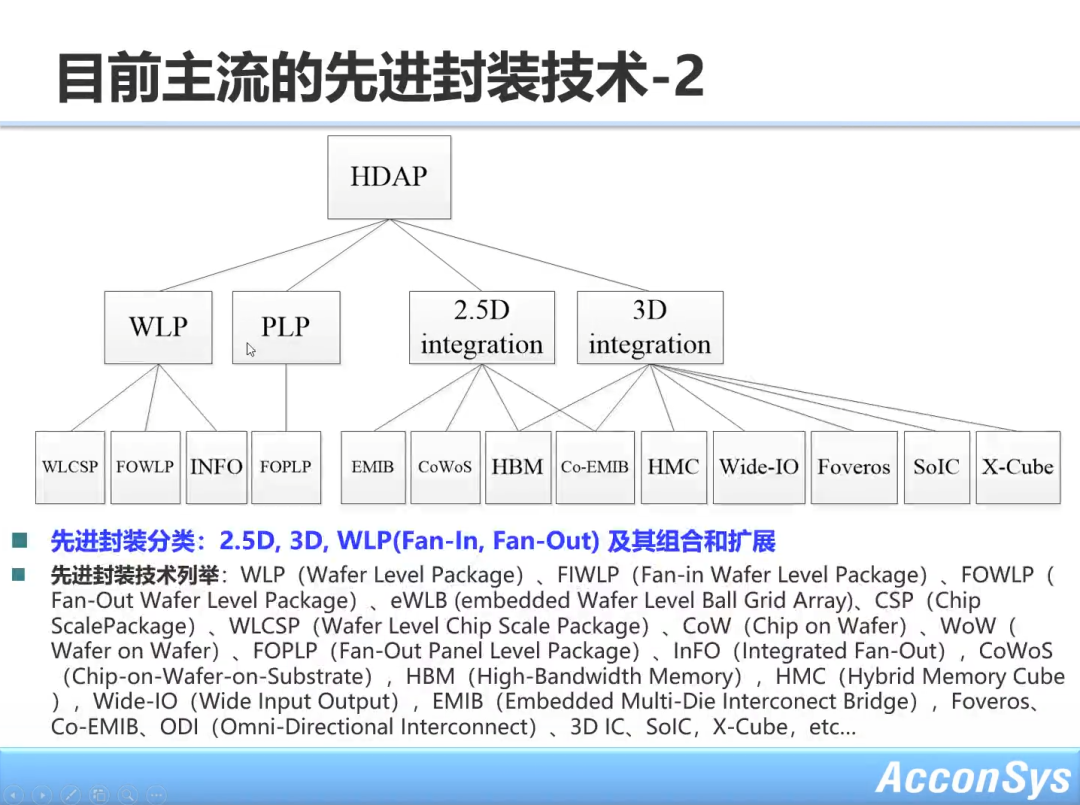

由于先进封装的种类很多,我对这12种进行归类,Wafer Level Package和Panel Level Package属于同一类,只是加工的承载体不一样。然后就是2.5D集成和3D集成,有一些比如说Co-EMIB和HBM,就属于既有2.5D又有3D,大致归类实际上就分为三类:2.5D、3D以及WLP(Fan-In,Fan-out)及其组合和扩展,细分起来种类非常多,每个厂家又有自己的命名,扩展起来有几十种名称,这个了解一下就行。

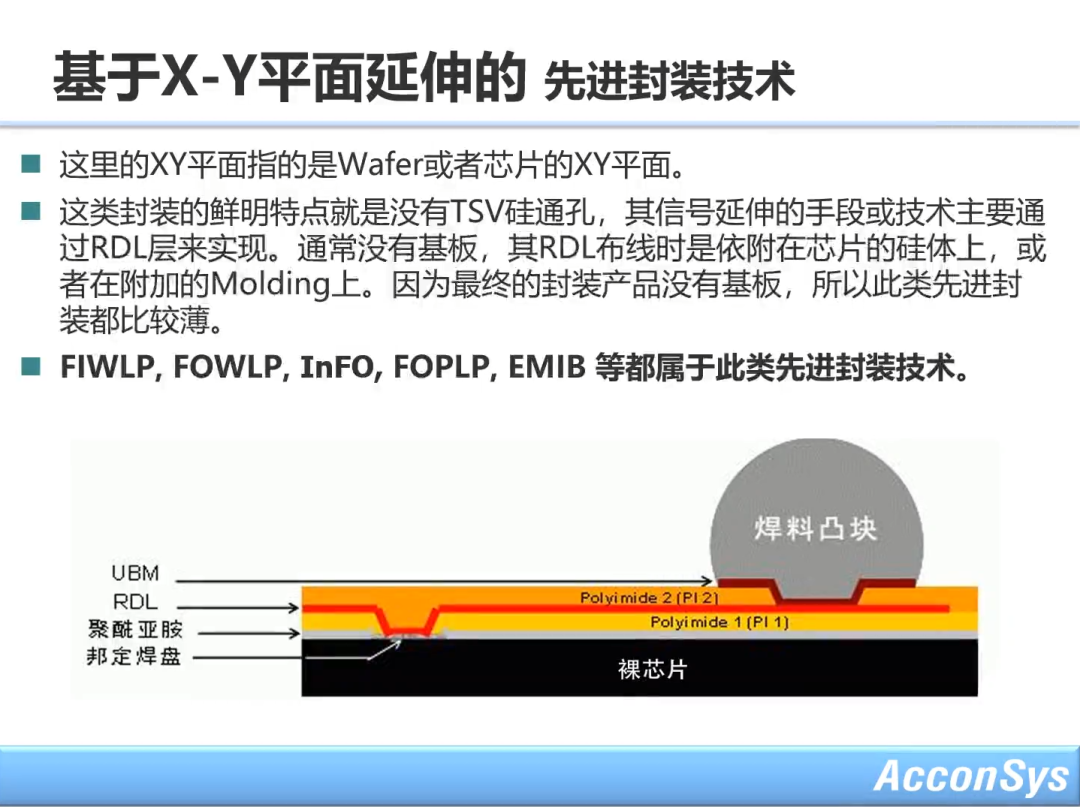

基于X-Y平面延伸的先进封装技术是没有硅通孔的,而是在芯片或者Wafer的X-Y平面上,它信号延伸的手段主要是通过RDL层来实现,通常没有基板,其RDL是布线时依附在芯片体或是晶圆体上,或者是附着在Molding上,因为没有基板,所以封装都比较薄。

Fan out Wafer Level Package、Fan in Wafer Level Package、INFO、Fan out Panel Level Package、EMIB都属于此类先进封装技术,X-Y平面延伸。

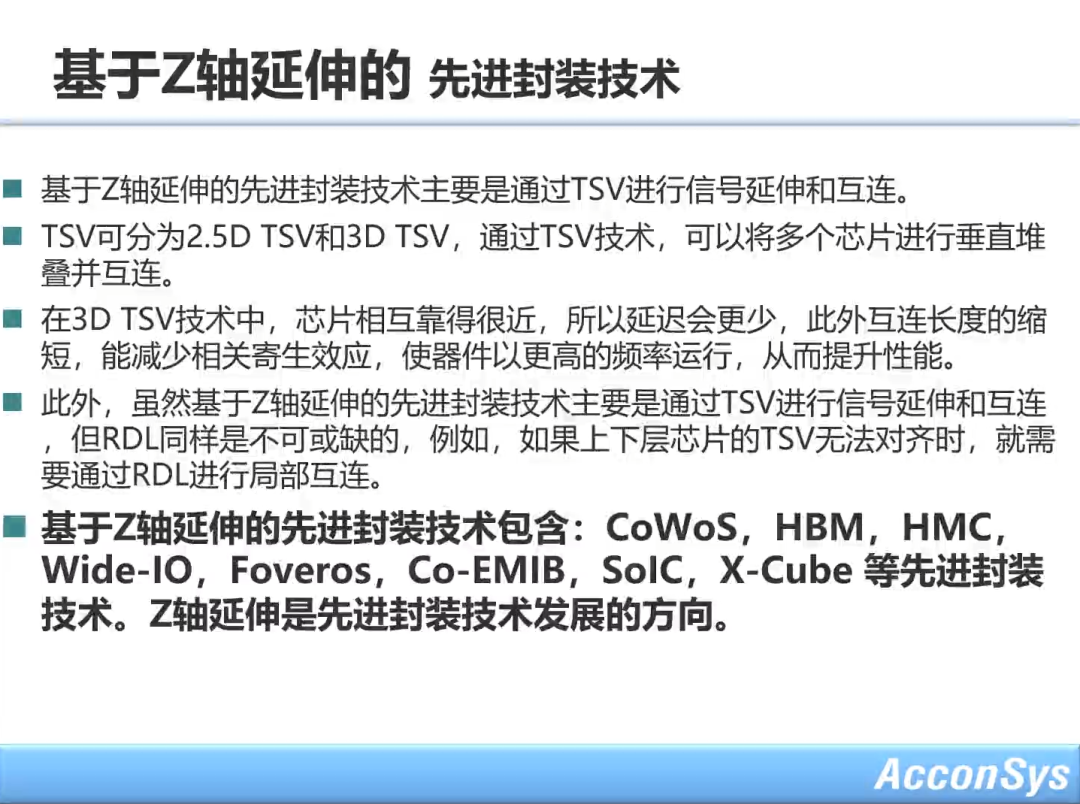

基于Z轴延伸的先进封装技术,主要通过TSV进行信号的延伸,TSV把它分为2.5D/3D TSV,通过TSV技术可以将多个芯片进行垂直堆叠并互联,在3D TSV中,芯片相互之间靠得非常近,所以延迟会很少。

此外,互联长度的缩短也能减少一些寄生效应,使芯片以更高的频率运行,从而提高性能。所以在很多对比上,可以看到采用3D TSV先进封装技术的芯片,功耗更低,性能更好。

另外一点,即使是3D TSV延伸也需要RDL,因为RDL如果上下层对不齐的时候,RDL就可以定义位置的X-Y平面的平移对齐,基于Z轴延伸的先进封装技术包含CoWos、HBM、HMC、Wide-IO、Foveros、Co-EMIB、SolC、X-Cube 等先进封装技术。Z轴延伸是先进封装技术发展的方向。

以后大家的发展目标就是往Z轴方向去延伸,因为X-Y平面的延伸面积会越来越大,但Z轴空间是非常大的,是未来先进封装技术的发展方向。

下面看2.5D和3D先进封装的设计方法。首先要了解设计方法,才能够进行设计。

先看2.5D的特点,2.5D设计中的特点就是有中介层上有RDL或者是RDL+TSV设计,还有基板上也有布线,所以特点就是项目中包含多个版图设计,版图就包含Interposer还有Substrate。其中又分为两类,一类就是中介层中有TSV的2.5D设计,另外就是中介层中无TSV的2.5D集成。这两种都有中介层,但把它分为两类,都叫2.5D集成。

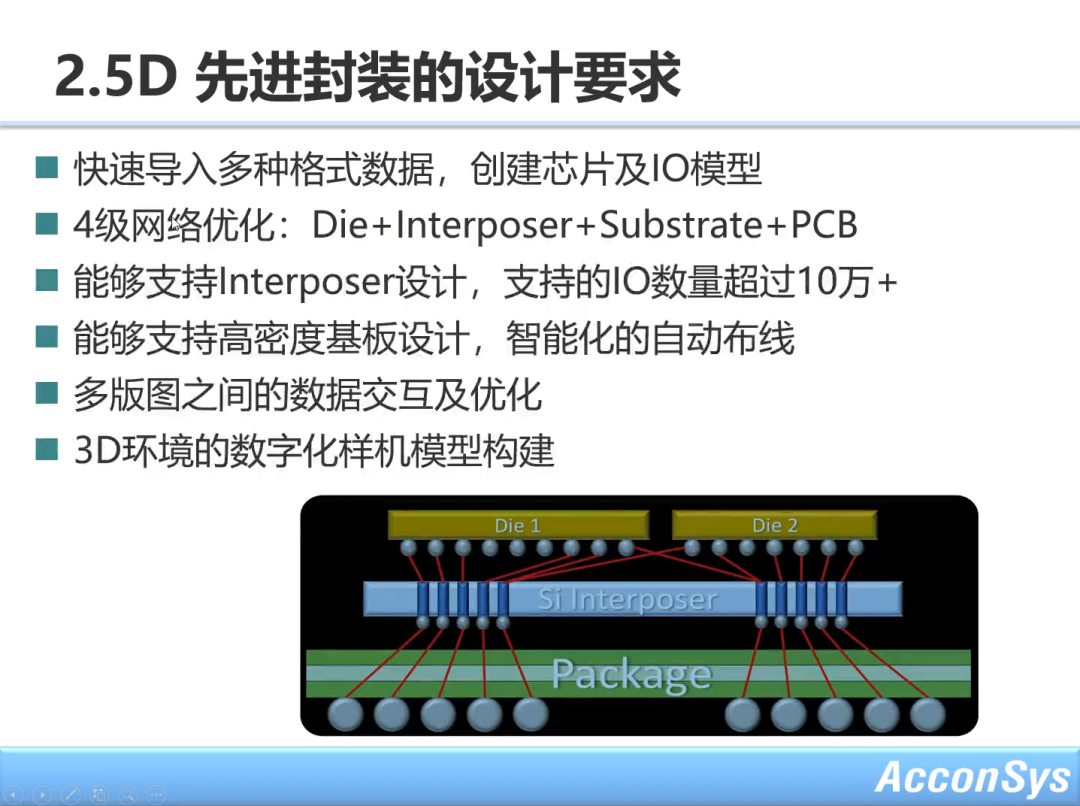

与2.5D相关的设计要求,首先要接触多种格式数据,创建芯片及IO模型,多级网络优化,比如说芯片Interposer+Substrate到PCB,叫4级网络优化,能够支持Interposer的设计,支持IO数量超过10万家,支持高密度基板设计,智能化的自动布线,多版图之间的数据交互和优化,3D环境的数字化的样机建模,这是对环境的要求,就是典型的2.5D中间有个Interposer,底下是基板,上面是芯片。

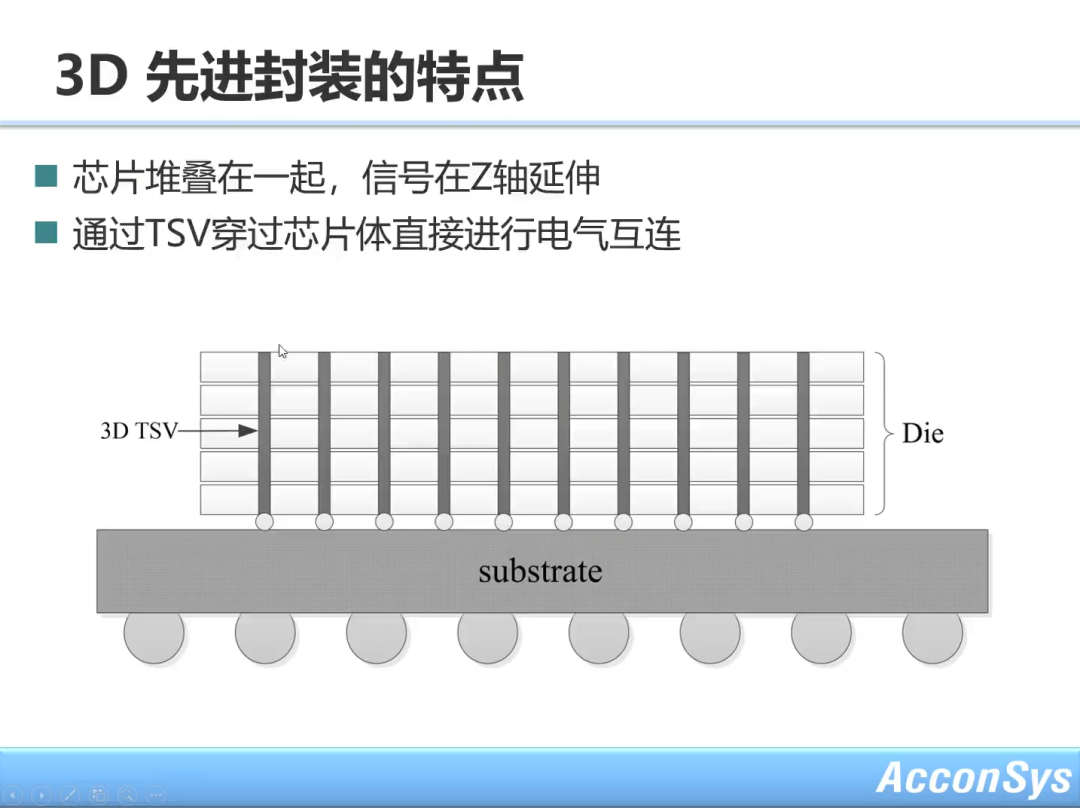

3D先进封装的特点,3D先进封装的特点就是芯片堆叠在一起,信号在Z轴延伸,通过TSV穿过芯片体,直接进行电气互联,TSV把芯片穿透,直接就进行电气互联,这是3D TSV。

关于3D TSV的设计要求,软件怎么识别这些TSV?知道它们能够把电气进行连接,软件能够自动识别相同网络的芯片引脚上下层的电气连接,如果错位以后,软件就能判断出来是断开,对准以后软件就能互联上,是非常重要一点,因为3D就是上下层堆在一起。实际上有很多的芯片,比如上面这些芯片,它实际上基板是脱离开的,这就是3D线性工程的设计要求。

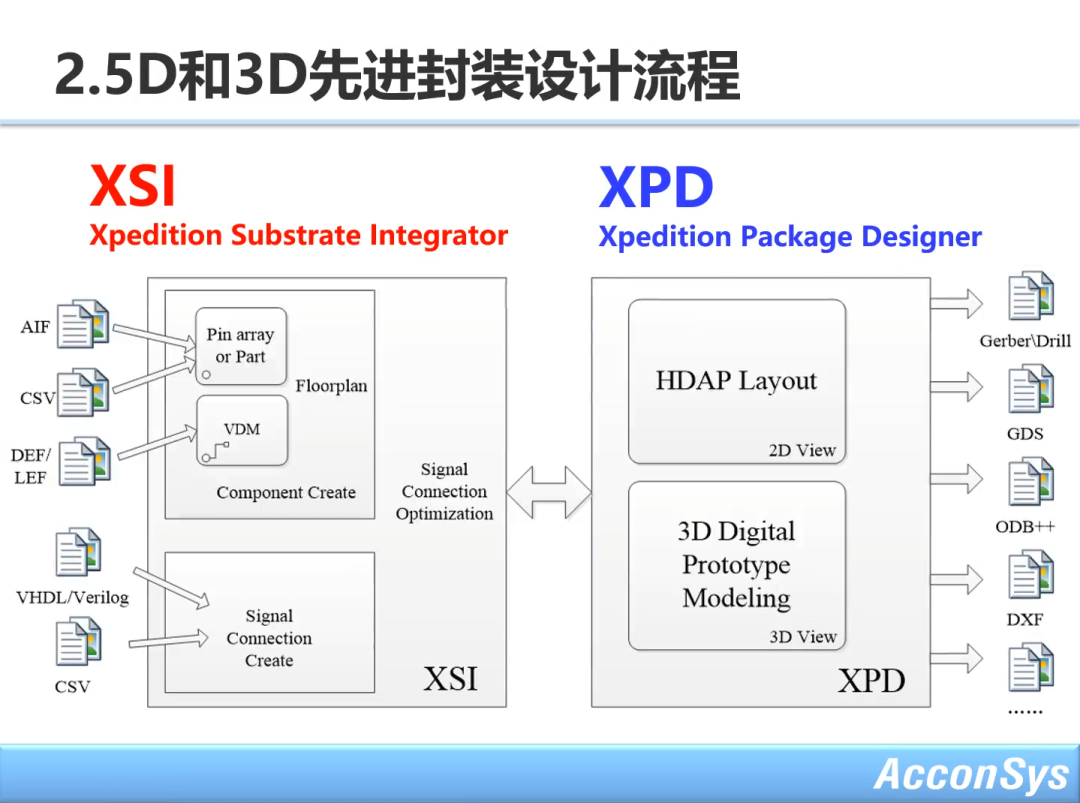

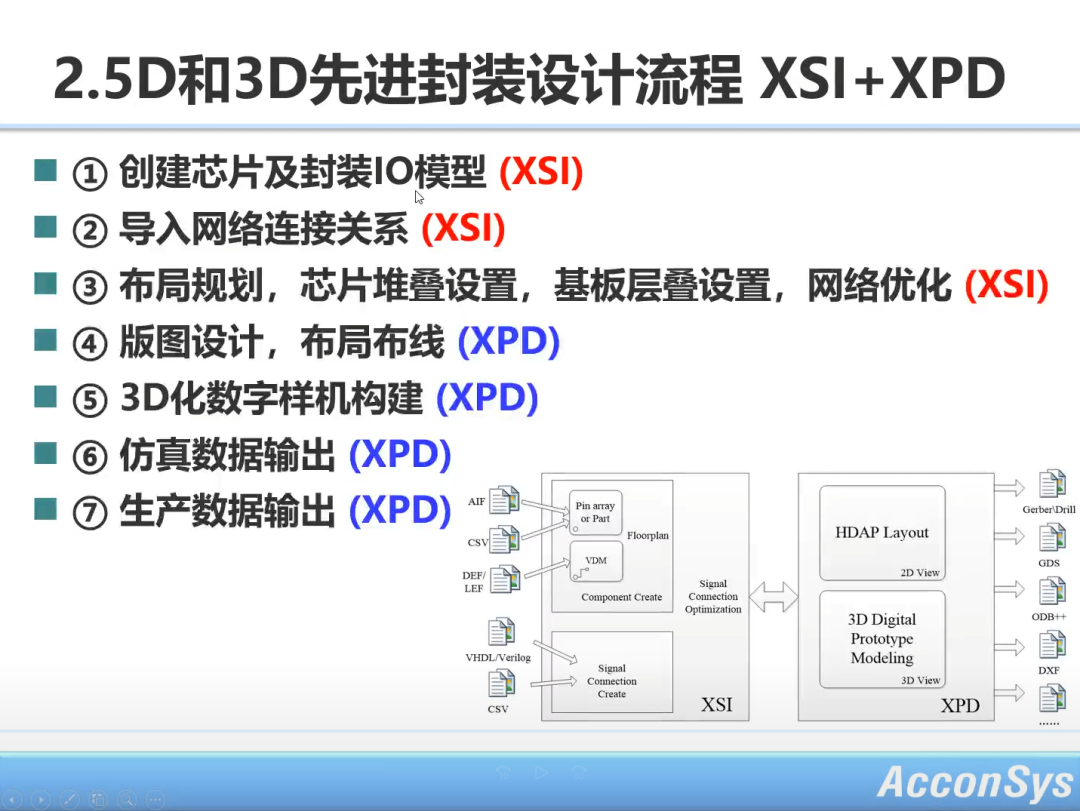

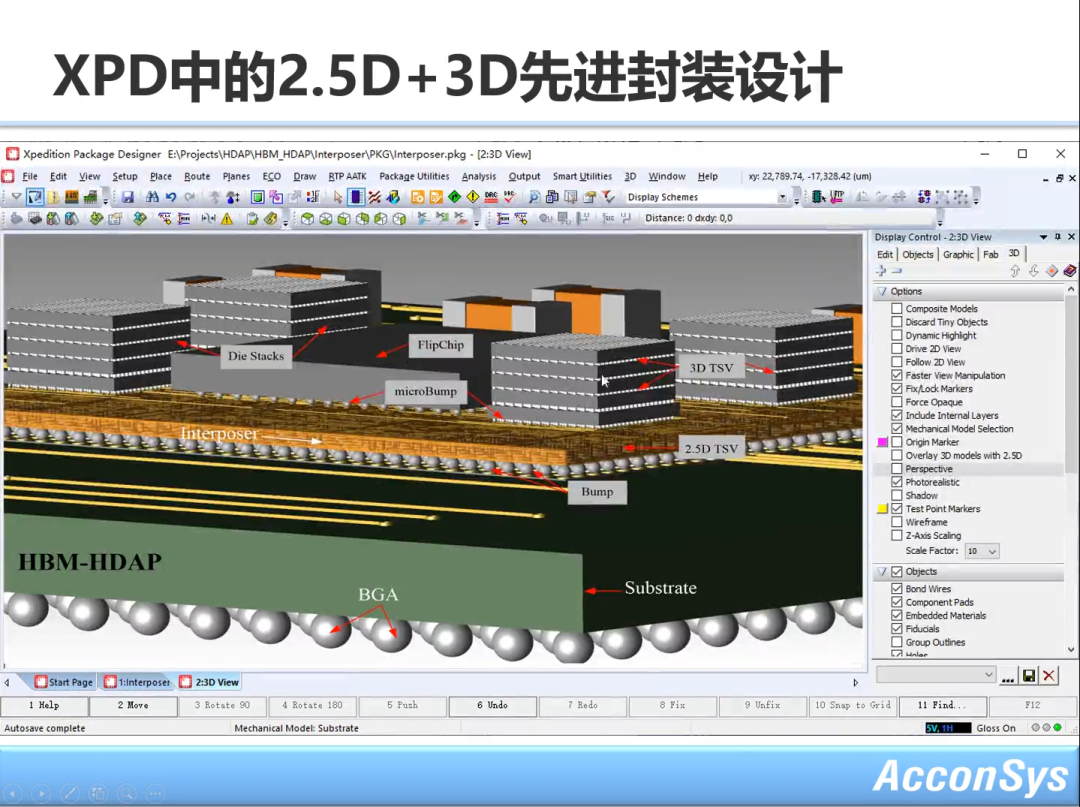

接下来给大家推荐设计工具,设计是离不开EDA的,尤其是在电路的设计这里,先进封装一样,2.5D和3D先进封装,设计流程里面推荐一套工具就是XSI和XPD,XSI叫Xpedition Substrate Integrator,XPD叫Xpedition Package Designer。工具它有创建元器件库的功能,能读入AIF、CSV、DEF/LEF的设计数据,能够读入 VHDL/Verilog的数据,能够创建网表、创建器件到XPD里面进行布局、布线、进行3D数字化样机的建模,再就是设计流程。

设计流程,这里分为7步,第1步是创建芯片及封装的IO模型、第2步是导入网络连接关系,第3步是布局规划、芯片堆叠设置、基板层叠设置、网络优化在XSI里面,第4步是版图设计、布局布线,第5步是3D化数字样机建模,第6步是仿真数据输出,第7步是生产数据的输出,在XPD里面。

下面通过实例来讲述2.5D和3D先进封装的设计。

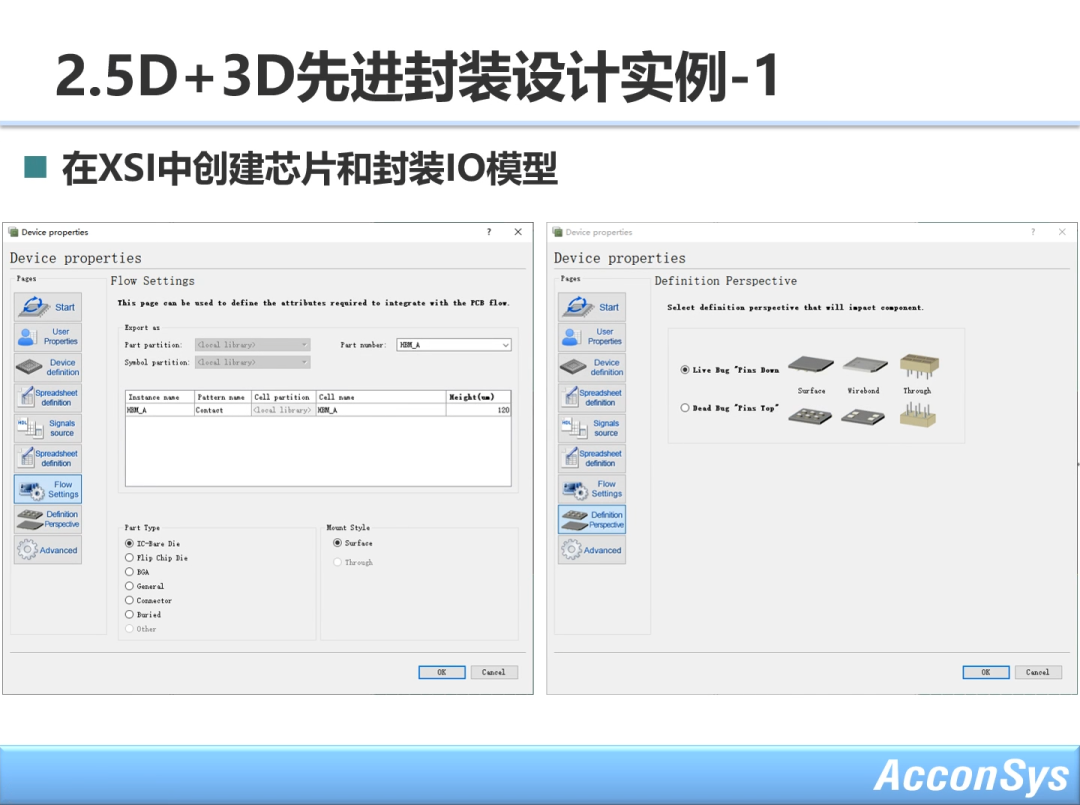

刚才讲在进行2.5D和3D先进封装设计的时候,需要两个工具XSI/XPD。接下来我来做简单的流程解释,首先在XSI里面要创建芯片和封装的模型,这里是Device property的向导,通过向导,可以导入一些数据,创建芯片的模型以及封装的模型。

这里可以看到,我们可以选择不同类型的芯片,有bare die、flip chip、BGA、Buried,芯片引脚的朝向也可以定义是朝上的还是朝下的,关于通过的话,今天不具体展开讲,通过向导是流程化的,从开始一直到完成,都是一步步的去选择就可以,所以用起来也是非常容易。

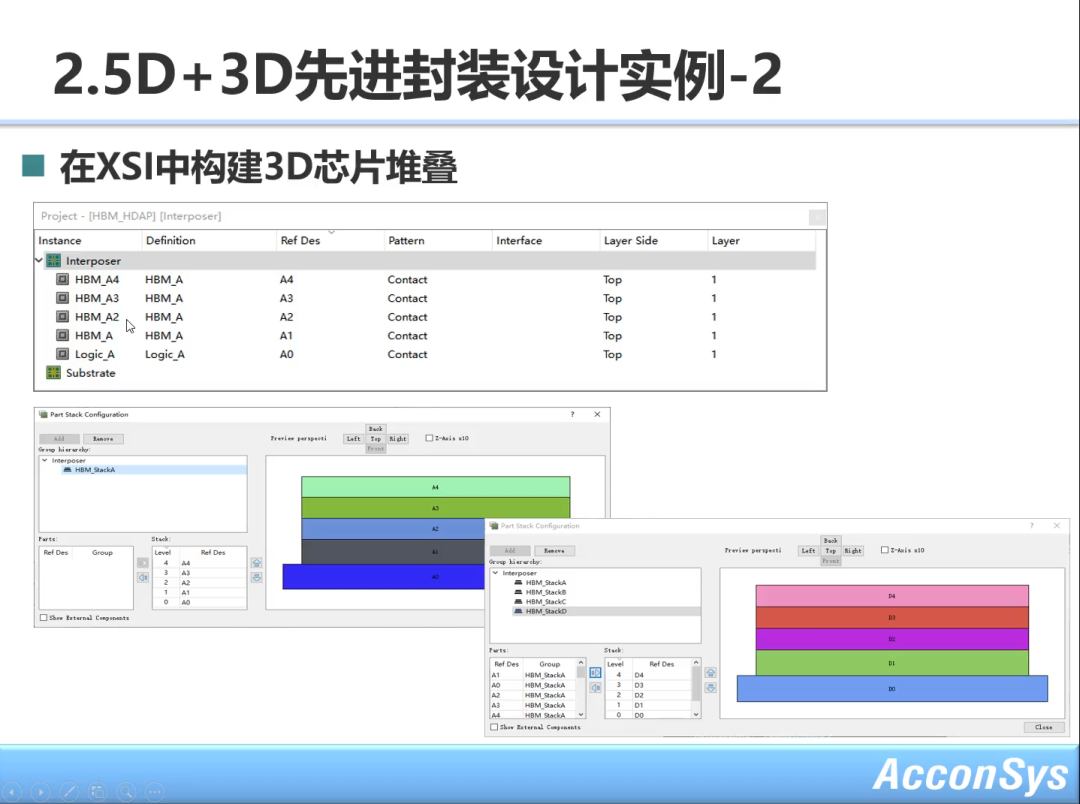

3D封装一定有芯片的堆叠,HBM 里面可以看,有几个芯片堆叠,叫 Stack A,里面有A0、A1、A2、A3、A4这5个芯片,堆在一起,其中要设置芯片所处的位置,不同的层从0~4总共是5层,这是Stack A。实际上在 HBM里有4个Stack,就是Stack A、Stack B、Stack C、Stack D,每个里面都是五颗芯片,上面是四颗DRAM芯片,底下是一颗逻辑芯片,这样四个堆叠实际上就是20颗芯片堆叠在一起,是3D的先进封装,又因为它用到硅转接板,又包含2.5D在里面,所以把它叫3D+2.5D或2.5D+3D的先进封装。所以这个实例是既有2.5D又有3D的例子。

2.5D就体现在Interposer上。刚才讲的4个堆叠,每个堆叠5颗芯片,总共20颗芯片,整个堆叠就放在一个硅转接板,大的球是硅转接板上的Bump,它位于背面,这个就是 HBM的一个堆叠,总共四个堆叠,把四个堆叠放在四个位置,比如说ABCD这样4个位置,就是一个20颗芯片放在一起,中间还会有一个芯片,大家看,这个芯片通常是GPU芯片放在中间,位于Interposer的上表面,而Bump是为Interposer的下表面,我们是通过顶视图可以看它,Interposer会被放置在Substrate上。

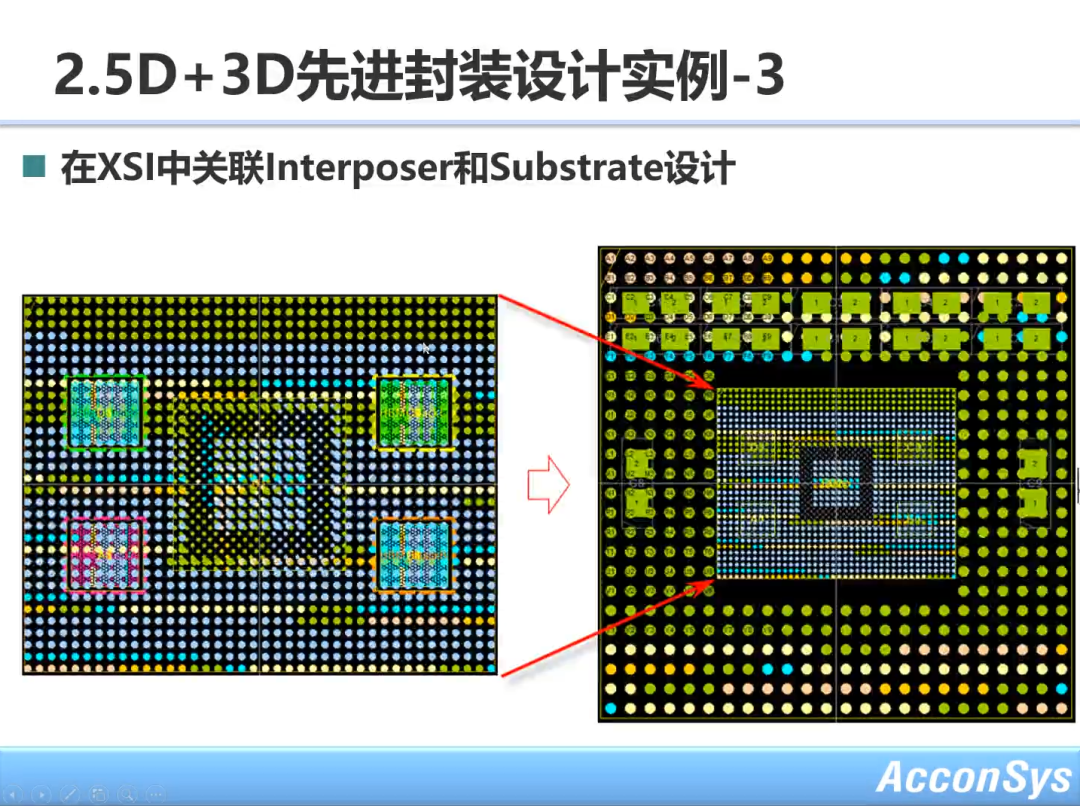

大家看到这个是Interposer,中间的 GPU还有这四个堆叠,它是一个整体放在大的Substrate,这是BGA的Substrate,这个Interposer放在Substrate上以后Substrate的可能还配置了一些电容,同样放在Substrate上,这就是整个设计的结构。在XSI里面,可以让Interposer和Substrate上关联起来,在Interposer上进行器件的布局,并让它们两个关联起来,就相当于我们说在XSI 5A可以看到就是说层次化的概念,就是Substrate上面有Interposer,Interposer上面又有芯片,芯片又有堆叠,就这样一个概念。

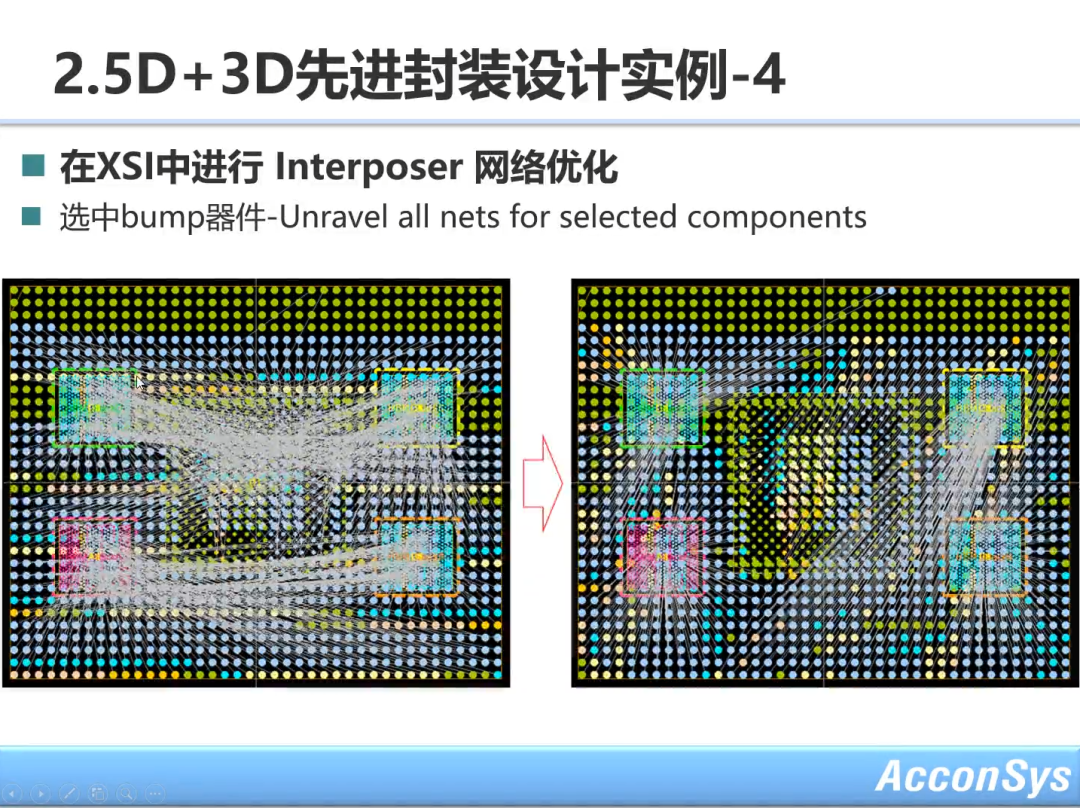

这个叫网络优化,大家看到我在定义网络了以后,一般在我们设计的时候这个芯片的引脚它定义好了对吧,但是Interposer上面的 Bump的引脚还是没有定义的,可以去灵活去定义,定义的原则就是让交叉最少,互联最短,同时电源和地又有合理的分配,这就是我们定义的原则。

首先就是进行网络的优化,如图是网络优化前后的比较,网络优化以后明显的交叉就比较少、很顺。把引脚都分散在周围,当然有一块看到还不是很完美,这就需要进行详细的优化。从右边图可以看出来,交叉就更少,互联也变得短。对 Bump的引脚的定义进行一些变换,找到合适的位置去连接这些网络。这个就是对Interposer的一个网络优化。

对Interposer进行网络优化好以后,这个Interposer是要放在Substrate上的,所以还要对Substrate进行网络优化,在Substrate进行网络优化以后Interposer的引脚定义基本上已经不变了,而主要是变这个BGA的定义。

大家看到这是左边没有优化之前的,右边是进行优化以后的,大家看到它的交叉变得很少,基本上是没有交叉,但是是不是最近?有时候你需要进行更详细的优化,局部的详细优化,整体的优化首先把交叉给去掉,大家看到基本上都是很顺,没有交叉,就Substrate,刚才我提到优化,要进行多级优化,从Interposer的网络优化到Substrate的优化,到 PCB网络的优化,这就是三级。再加上芯片的网络优化就是四级网络优化,这款软件能够支持多级网络优化。

网络优化完以后要定义版图的模板,首先在XSI给 Interposer选择一个模板,选择的3+2的硅基板模板,3+2表明是上面是三层,底下是两层,3+2,中间是硅通孔,这是3+2的硅基板模板。

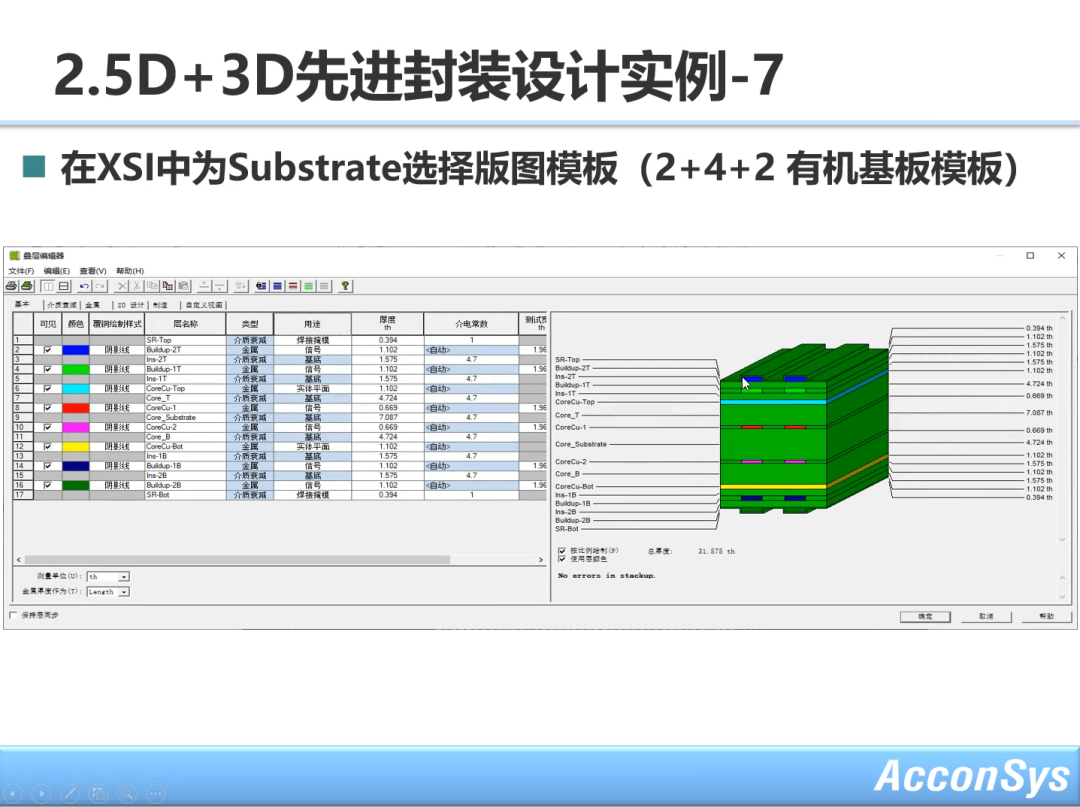

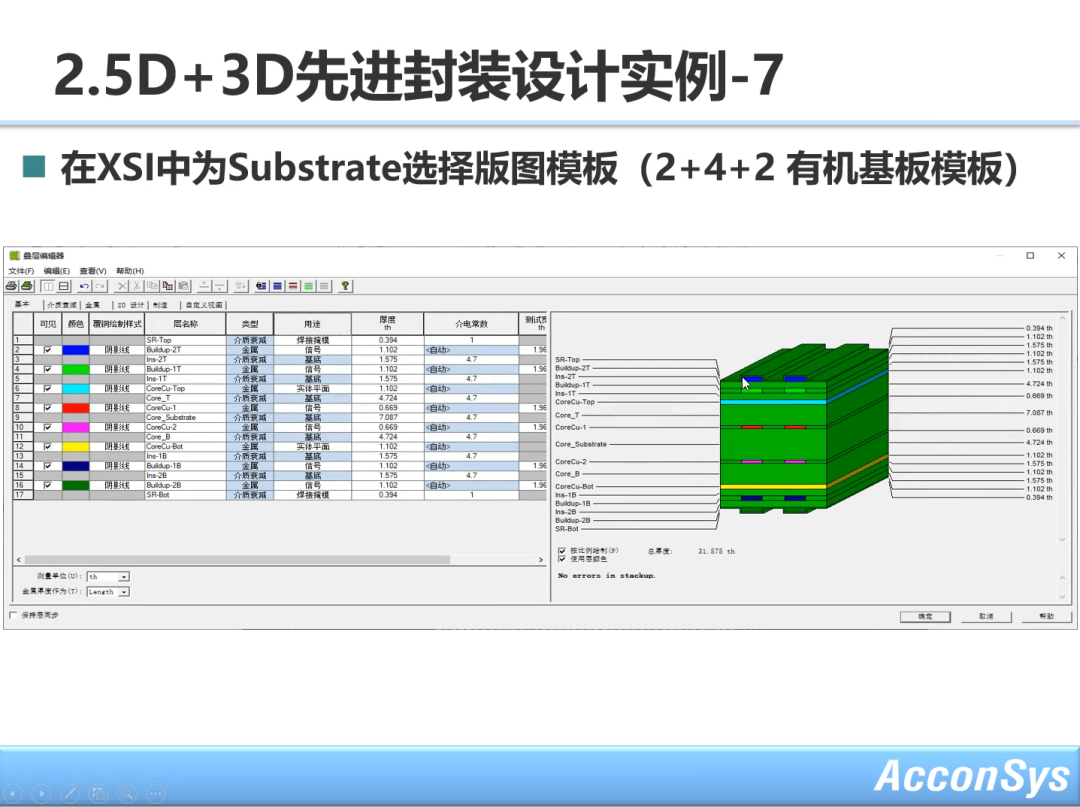

同时还要给Substrate选择模板, Substrate它用的是2+4+2的有机基板模板,4是承压层,2是Built up层,这是两种不同的工艺,一是基层法,一是层压法,这就是八层的有机基板。

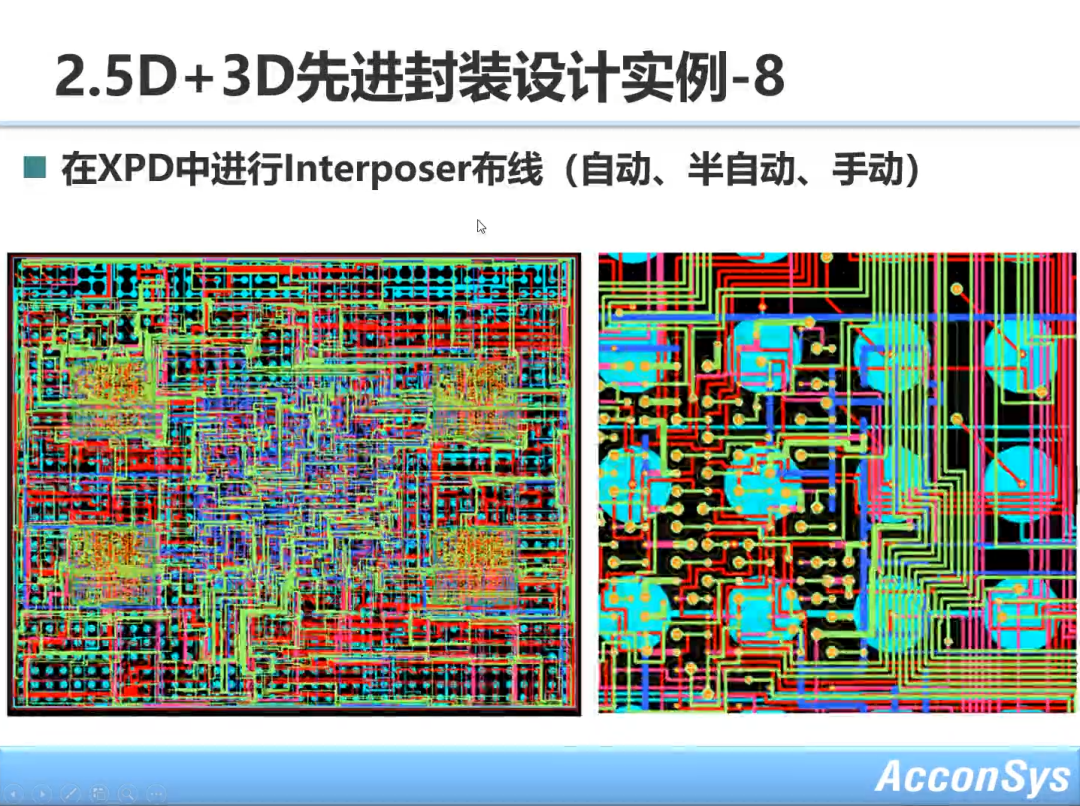

定义好后,就可以把设计导入到XPD里面,在XPD里面进行Interposer的布线,其中对应的Interposer可实现自动布线或者半自动布线或者手动布线,这是Interposer里面的布线,这个Interposer布线呢,我这里面设置的是纯90度布线,就说没有45度拐角,都是横平竖直的,看起来有点像芯片里面的线路,在硅材料上就是横平竖直的,处理更容易一些,这个大家看到,这是局部的图,就是在Interposer的布线。

当然目前来说设计并没有完成100%布线,因为我是后来采用全自动布线,如果再加上手动布线,再加上网络优化比较好,肯定是可以达到100%的,因为实际设计就是需要100%。

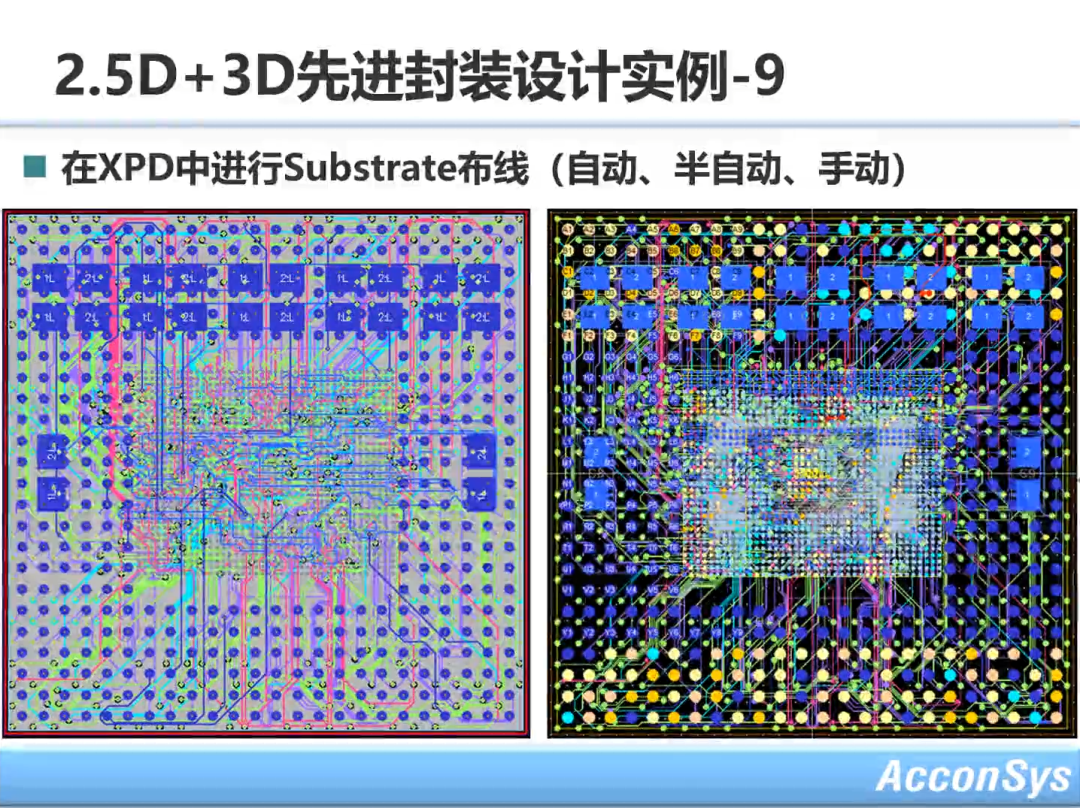

Interposer布线完以后还要进行Substrate的布线,大家看到在版图设计这是一个项目,实际上是两个版图。在版图设计里面就要把它分开设计,Substrate和Interposer设计实际上是分开设计的,但是在网络关系在XSI里面又是有关联的。

大家看到这是Substrate的布线,右图是把Substrate上的布线导入到XSI里面的, XPD实际上是一个Layout设计工具,设计完成以后可以把设计数据导入到XSI里面预览,而且有一点XSI里面可以看到层次化的概念,既可以看到 Substrate的布线,也可以看到你的Interposer的布线,实际上这是两个板子,两个设计,但是它在XSI里面都可以请同时进行预览,有层次化的关系,这是非常方便的。

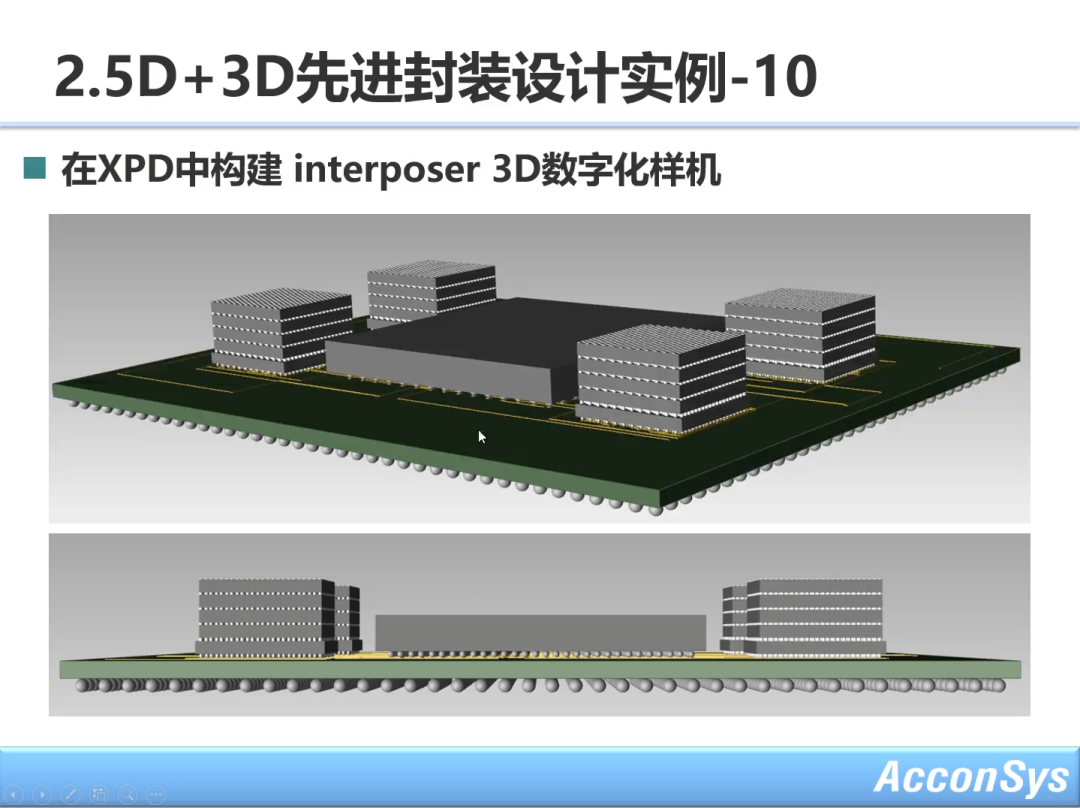

除此以外,还要构建就是3D数字化样机,这时候把3D打开以后,数字化样机构建以后,可以看到这才知道原来封装是这样子的,这个就是一个Interposer,这个就是一个堆叠芯片堆叠,四个芯片堆叠,总共20个芯片,每个里面是5个芯片,中间是个GPU倒装焊,然后就放在Interposer上,Interposer上面有Bump,像上面都是Micro Bump,Interposer Bump要放在BGA上,现在构建的是Interposer的3D数字化样机,然后又把 Interposer又给它放在Substrate。

上图是Interposer的剖面图,为了看清内部的结构。下面图就是完整的图,是Interposer放在Substrate上,上面是4个芯片堆叠和1个芯片,整个叫数字化样机,就是Interposer+Substrate的一个2.5D+3D的先进封装的设计实例。

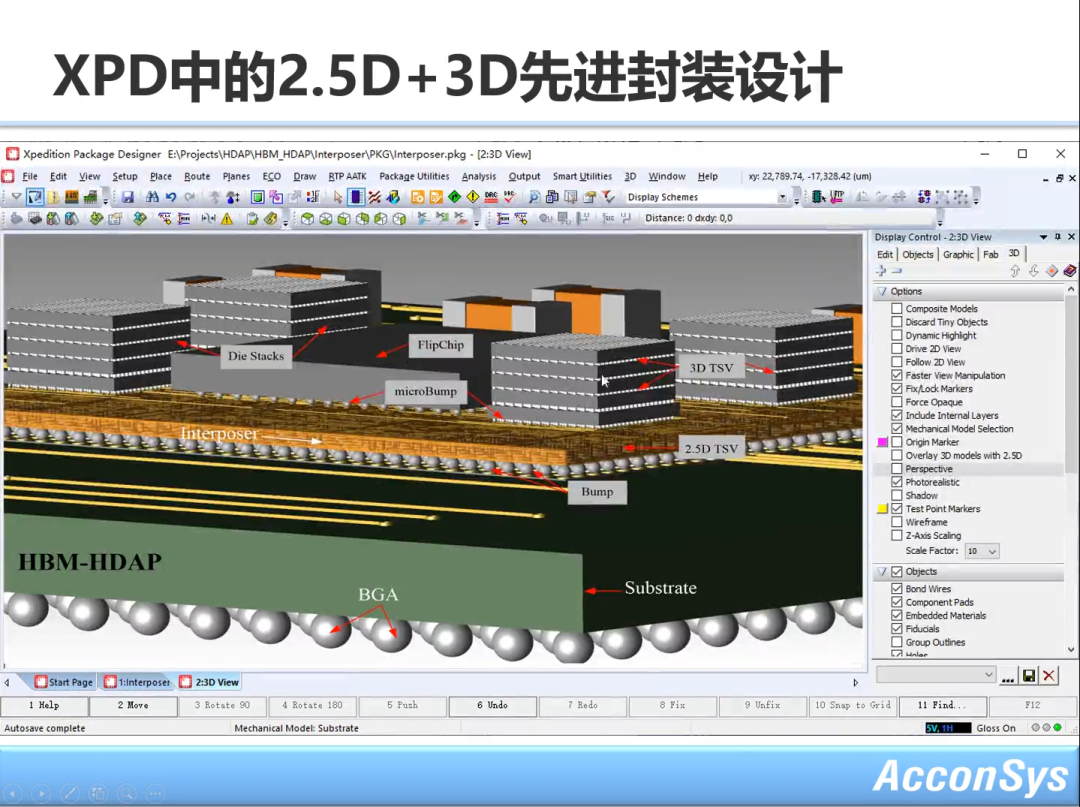

这个就是在XPD里面,大家看到Substrate Bump,Interposer上的2.5D TSV也可以看得很清楚,然后Interposer上RDL也看得很清楚,Micro Bump,倒装焊,还有每个上面的3D TSV,3D TSV实际在芯片内部看不到,但可以看到Bump中间的,Bump上下方都是3D TSV把芯片互联起来,大家看到0402的电容跟芯片比起来它已经显得很大。这就是整体的图,这样就完成了设计。这个设计中间的电气互联关系在 DRC检查的时候都能够检测出来,如果错位了或者没有连上,都会给你报错。所以从设计到检查都是通过EDA工具来协助完成的。

好,接下来给大家分享先进封装的仿真方法。

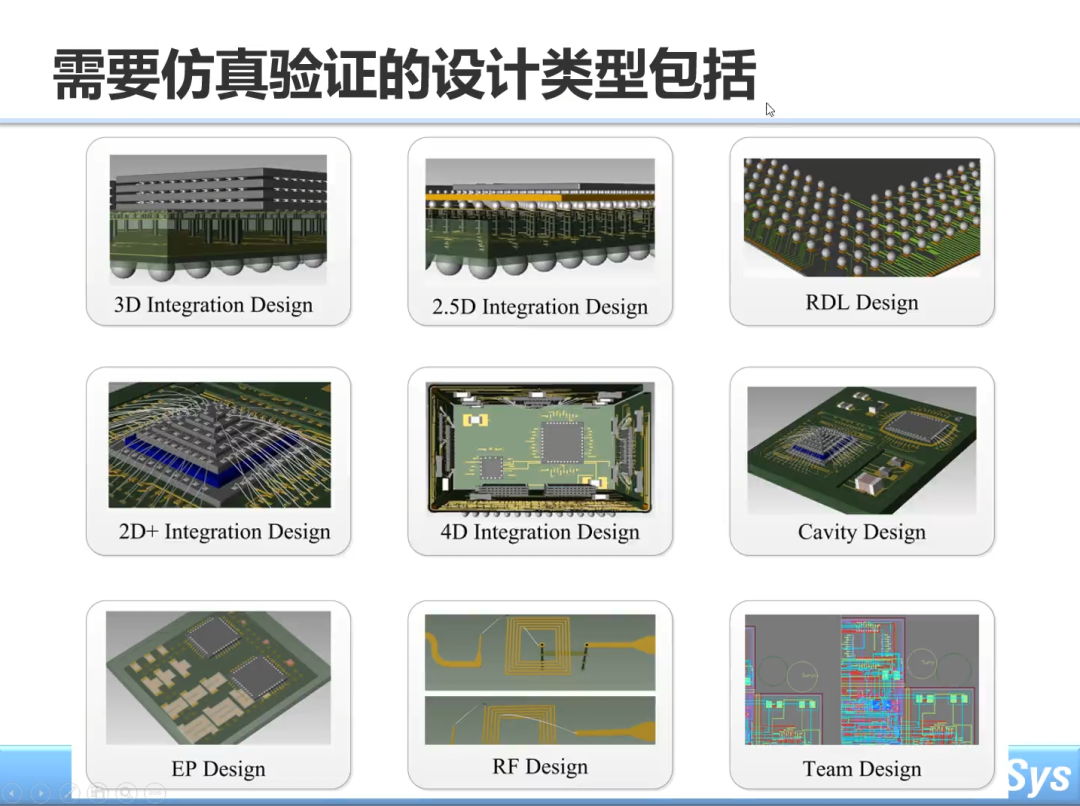

大家看到先进封装类型还是很多的,看到分类,这个就是3D集成,2.5D集成。3D芯片直接互联,2.5D就是中间有Interposer,还有RDL的设计,比如说 Fan out,还有2D plus的,与3D有区分,是通过芯片堆叠,通过键合线互联,把叫2D+。

大家可以看我写的一篇文章,就是关于电子集成技术全面解析,怎么去分类,还有4D集成,实际上是多个基板进行折叠形成的,像小盒子一样,还有腔体设计,基板上挖腔体,还有EP就是埋入式的无源器件,主要是电阻电容埋到基板里面去,还有射频电路设计,最后这个是多人协同设计,它实际上不是一种设计类型,是一种设计方法,所以看到这些设计类型都是不太一样的,仿真的时候实际上也会有一些区别。

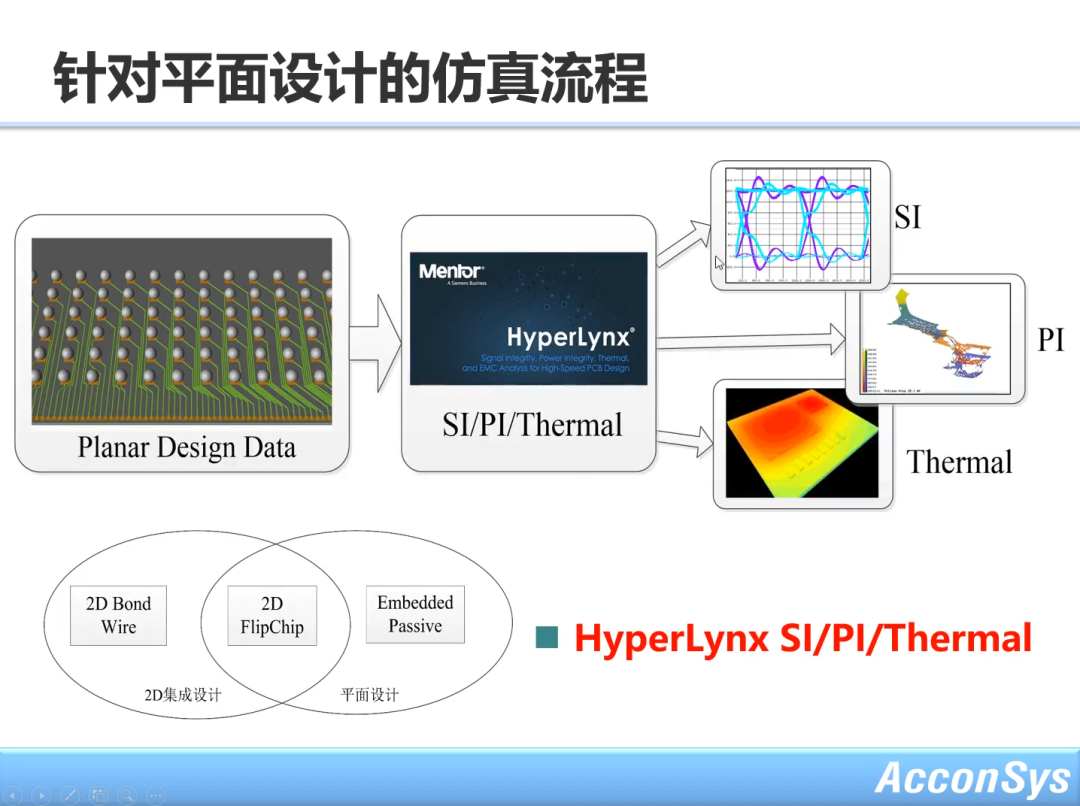

我们把它分为两类,一类就是平面设计,一类就是非平面设计。平面设计主要就指的是,没有空间的概念,主要是芯片有堆叠,还有有键合线这类的都是非平面的。所以平面设计,可以直接像这种平面设计,直接可以读入到HyperLynx里面的SI/PI/Thermal里面进行仿真,看到这个电压PI的仿真,看到压降、电流密度、热仿真,这个里面包含,主要是平面设计,平面设计包含2D的 Embedded passive,2D的Flip chip主要是这样两类,2D集成和平面设计还不完全一样,2D集成包含2D的Bond wire和2D的Flip chip,所以平面设计是不能处理Bond wire的,Bond wire实际上,虽然我们把它没有堆叠的Bond Wire叫2D的Bond Wire,它实际上是有空间的键合线的弧线,是平面设计的工具无法处理的。

针对非平面设计,就是这些3D、4D、2.5D、2D plus、Cavity、2D bond wire design。这些设计实际上都牵扯到一些三维的元素,需要读入到advanced solver里面进行解析,去得到RLGC的参数, s参数z参数,所以得到这些以后再进行仿真,所以就是说,首先第一步要通过这种解析工具把这些三维的元素解析出来,要用到HyperLynx advanced solver。

把得到的这些参数,可以放在二维仿真工具里,比如HyperLynx SI里面,这是互联器件模型,放在一起就可以得到演示图,这是仿真有两个流程,针对平面设计和针对非平面设计。

另外还有就是第三方的软件接口,第三方软件就是除了EDA自己的工具外,它还可以输出ODB++/GDSII各种各样的数据接口,满足各种仿真生态需求。这其中就包括的Cadence的Sigrity的power DC和power SI它可以和输出的设计数据进行结合,在Sigrity里面进行仿真。Sigrity里面明确说是支持这些数据的,包括Mentor Graphics等这些数据,第三方软件也有比较好的数据接口。

下面讲先进封装的电气验证。

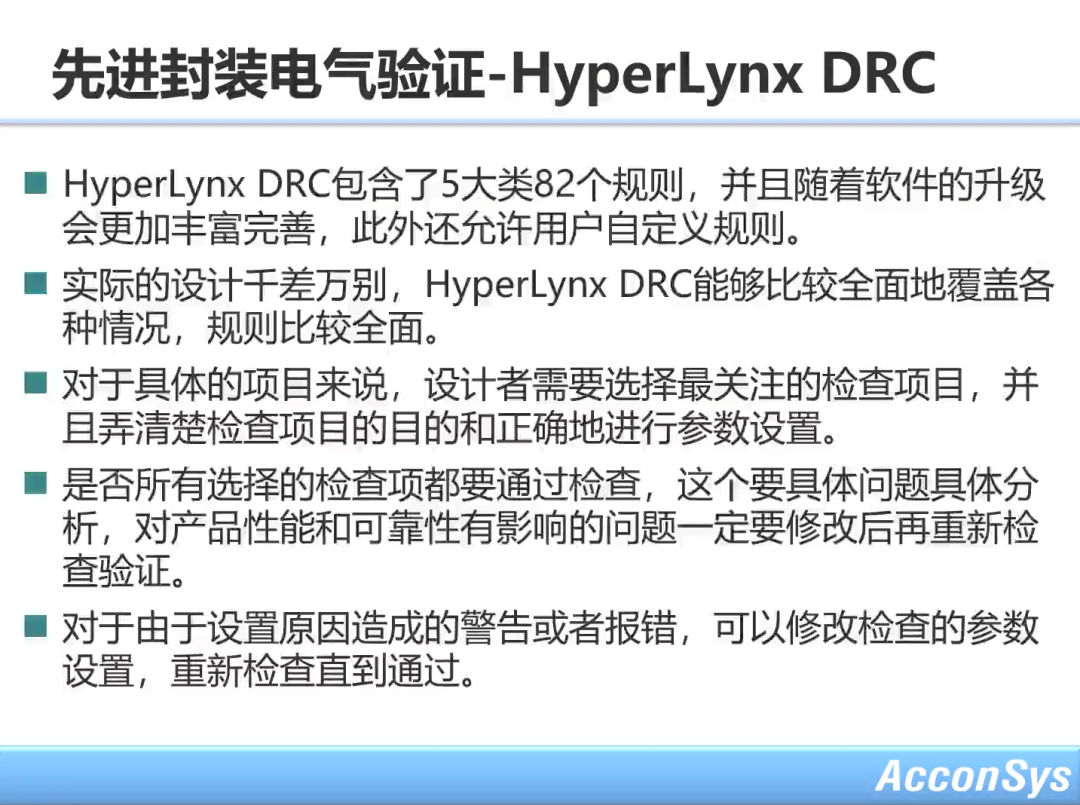

电气验证主要是针对HyperLynx DRC这个工具,HyperLynx DRC目前对先进封装支持的还是比较好的,专门对先进封装开发了一些规则,它可以支持3D设计、4D设计、2.5D、2D plus、Cavity以及2D的Bond wire design,里面内嵌了有82项规则,规则不是固定的数值,是在不断的增加,现在实际上已经超过82项。

目前分为这几大类,规则分为Analog、EMI、PI、SI、Safety。随着不断的发展,规则会越来越丰富,种类也会越来越丰富。HyperLynx DRC它使用起来也非常的方便,把设计数据给它导进去,跑规则,就可以给出报告。

规则就以咱们现在讲的版本里面内嵌的82条规则,5大类82条规则来分,它比如信号完整性规则就包含43条,电源完整性的规则包含10条,电磁兼容性的规则有18条,模拟电路规则有3条,以及安全规则有8条,有非常丰富的规则,而且这些规则是在不断地增加,它是一个动态的过程。大家看到每一张规则都有图示,这样便于大家去理解规则。

比如右上图是器件块分割平面,有Victim night,有干扰的县和被干扰的线,这个是高速线跨平面分割,下面是硅孔,有很多种规则的类型,每个规则都会给你讲述规则的道理,把这些规则学完以后,实际上的知识上会丰富很多,这些是需要注意的,也适合大家去进行知识的丰富。

HyperLynx DRC包含5大类82个规则,随着软件升级还会更加完善。这里面还有用户自定义规则,比如说其中没有包含的规则,我想自己定义可以吗?当然可以,它可以支持自定义规则,还可以自己去开发,所以覆盖是比较全面的,但是还给留出用户自定义的接口。

另外有一点是需要大家注意,并不是说我拿到设计,把82个规则打开全部检查一遍,这时候你会发现有些东西可能不是你关注的,或者和你想象的不一样,它会检查出来一些就是你认为不可能发生的问题,所以就是需要根据这些设计进行合理的进行选择,不应该每次都把它全选,有些规则跟你根本不相关,这样会检测出来一些想象不到的问题,这时候可能那些问题不一定就很准确,所以就要进行合理的分析、合理的选择、合理的修改参数,进行检查和验证。如果是设计原因造成的警告和报错,重新修改参数检查通过或者有些实际上是可以忽略的。

所以有时候为什么第二次怎么检查出那么多问题,实际上没有那么多问题,这实际上就是对规则的取舍,不是说每次都要把这80多条规则全部选上,在实际使用中需要注意,它确实能够改善设计质量、能够提高设计质量,这是能够帮助提高设计电气,所以叫它电气验证,电气的环节给它验证,提高的产品设计的质量。

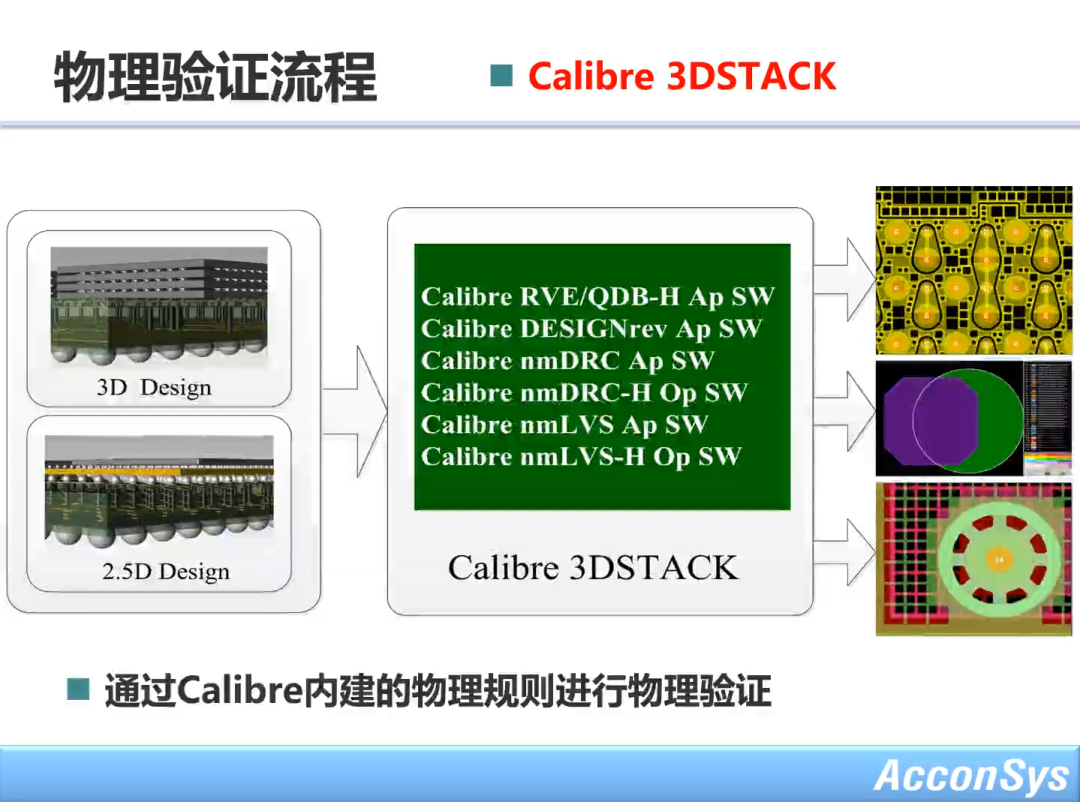

除了电气验证,还有叫物理验证,以前封装级别实际上并不强调物理验证,到先进封装级别,为什么突然又去强调物理验证呢?因为先进封装在很多地方跟芯片有相似性,用到硅基板,在芯片上面要做动作,对其打孔、做RDL,这都是芯片工艺上的要做的事情,所以就把芯片上的一些物理验证的规则和要求,也转移到先进封装里,这就是先进封装的物理验证。

它会用到什么规则,它会用到什么工具,其中有个叫Calibre 3D STACK,Calibre大家可能了解过,它实际上是芯片验证工具,而是在验证领域里面是它一直处于龙头老大的地位,就是Calibre它是很强势的,所有的封测厂,Tsmc、中芯国际,没有Calibre做过验证,他都不接你的单子,所以说Calibre是业界的标准。

现在Calibre 3D STACK是怎么针对3D封装进行验证的,我给大家解释一下。

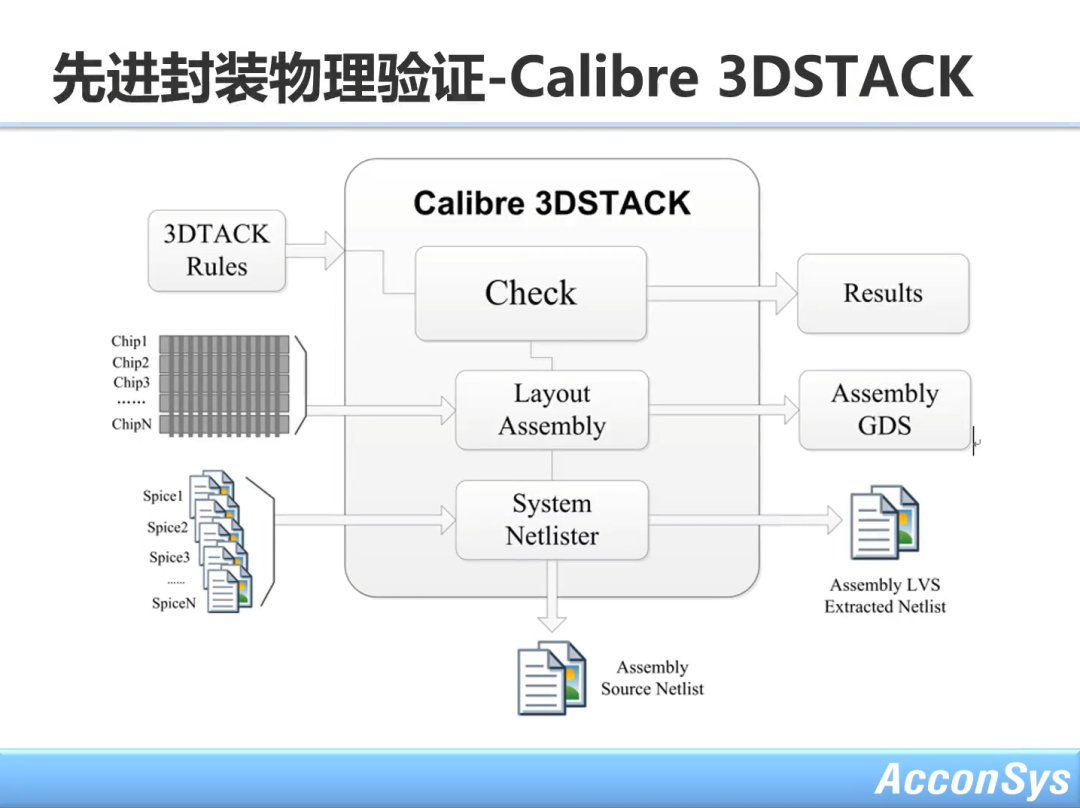

首先3D STACK的rules,把 chip的信息读进去,还有 spice的网表也读进来,读进来之后进行检查,进行layout的装配,还可以输出系统的网表,检查有检查的结果,装配有装配后的GDS,还有 LVS,,原理和版图的对比,就是Calibre 3D STACK工作框图。

Calibre 3D STACK包含这些模块,这个是Calibre的RVE/Desire review,nmDrc-h还有Lvs Ap和Lvs-H,这是6个模块是必须的,这是Calibre 3D STACK,基本的一个环境是需要配置的。它能够支持3D设计,芯片上下堆叠的设计,还有2.5D设计都是可以支持的,所以这就是今天讲的就是2.5D和3D的设计和验证,Calibre 3D STACK主要是针对2.5D和3D,可以检查特殊的布线,上下层的对准关系以及特殊的一些相对来说是工艺规则,通过Calibre 3D STACK内建过滤规则进行物理验证。

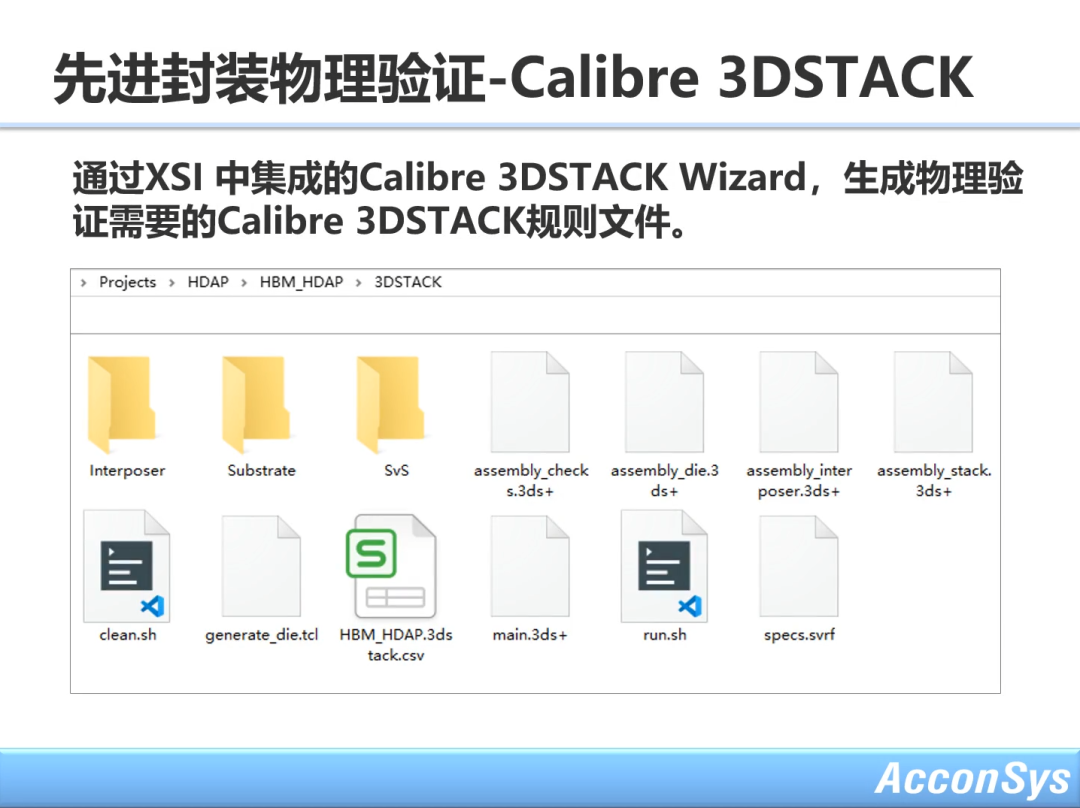

首先怎么验证?在 XSI里面集成了Calibre 3D STACK的Wizard,这个Wizard把它打开以后,可以生成物理验证需要的Calibre 3D STACK规则文件,Wizard用起来也有一步一步的告诉你怎么去做,你可以点一键生成,就会生成相应的文件。设计只要没有问题,生成的文件应该也没有问题,这些文件就是Calibre 3D STACK检查时需要的规则文件,这些规则文件要输出到Calibre里面去。

另外就是除了规则文件以外,还要输出就是设计里面的GDS文件,刚才这些在XPD里面,然后再输出GDS格式的文件,并读取到Calibre中,这是Calibre界面,把GDS读进来,读进来之后再加上刚才那些规则文件就可以进行检查。

检查主要分为两大块,就是检查项是否全部通过,下图一,大家的检查有很多检查项,检查项通过,它就给你打个勾,没有通过会打个叉,这时候看到检查通过就没有问题。

然后这边还有就是检查报告,当时给出检查报告,检查报告是correct,出小笑脸,Clibre 3D STACK的系统报告是,那就说明没有问题,这两个一个是检查全部通过,一个是检查报告正确,这就说明在看Calibre 3D STACK里面我检查基本上是没有问题。

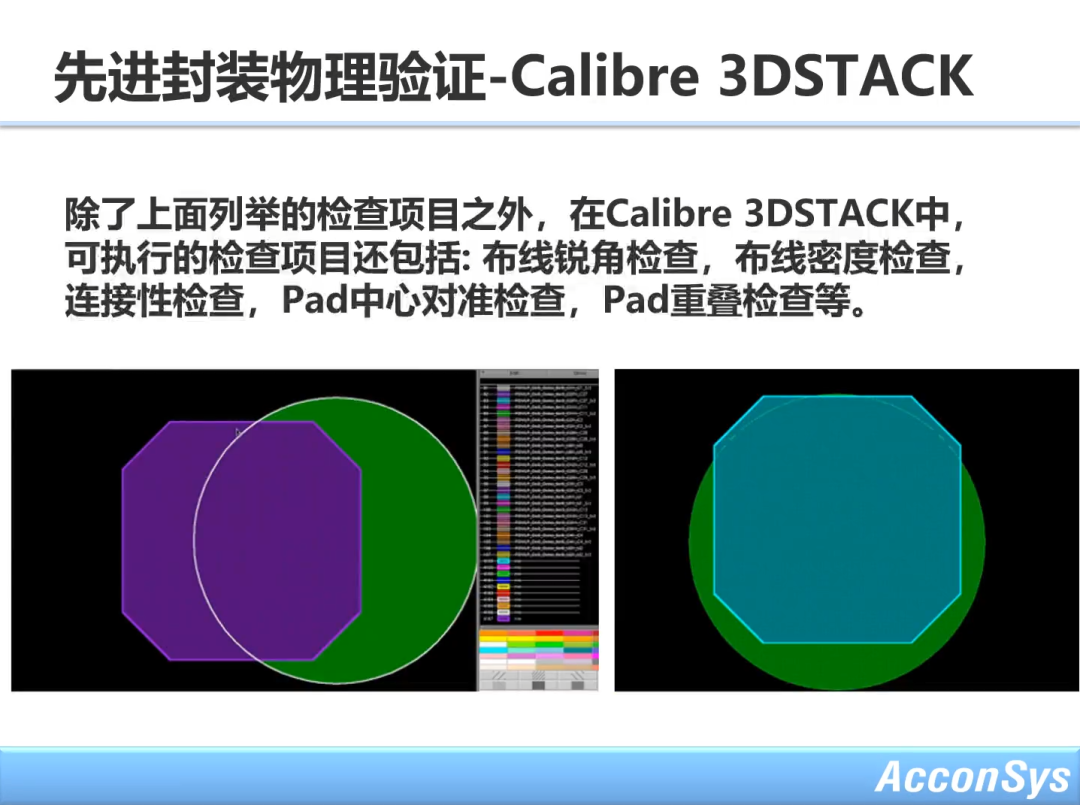

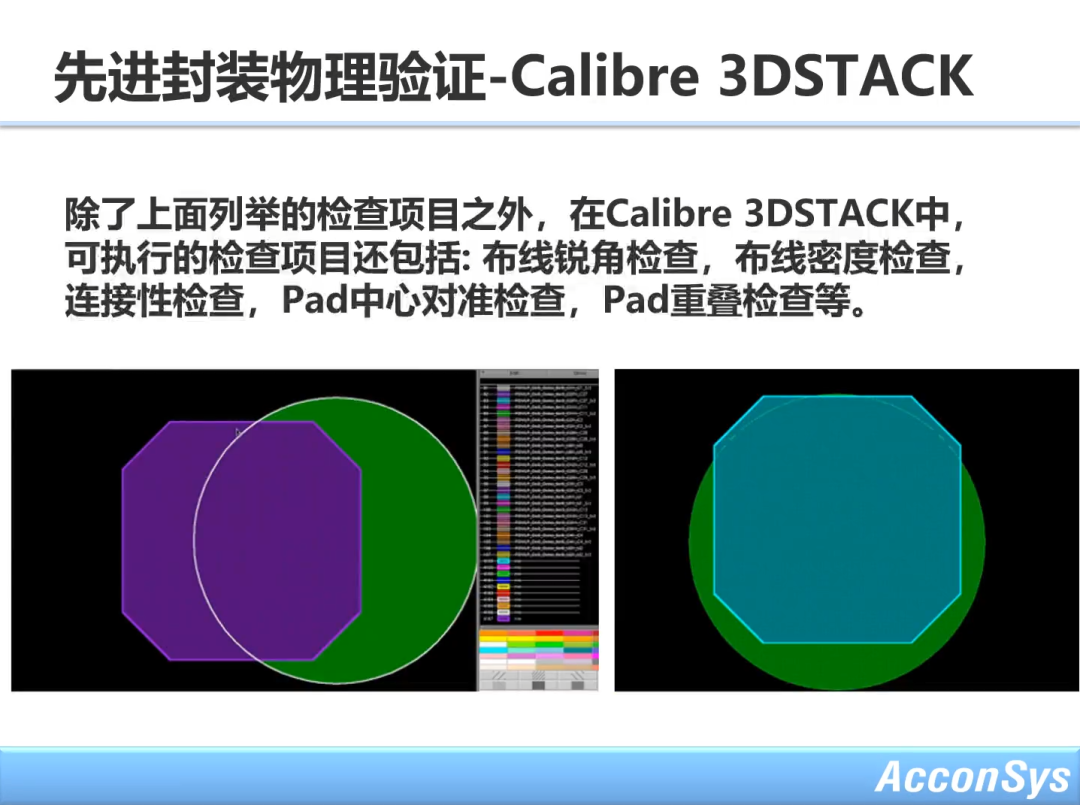

此外还有一些系列的检查,比如Calibre 3D STACK里面,可以检查的像还包括布线锐角检查、布线密度检查、连接性检查,PAD中心对准检查、PAD重叠检查,大家看到这个就是 PAD的中心对准,PAD重叠,因为存在上下层关系,如果你中心没有对准,有些时候电气连接可能就会有问题,所以它就会给你报出来,中心没有对准,这就是中心对准检查和重叠性检查。

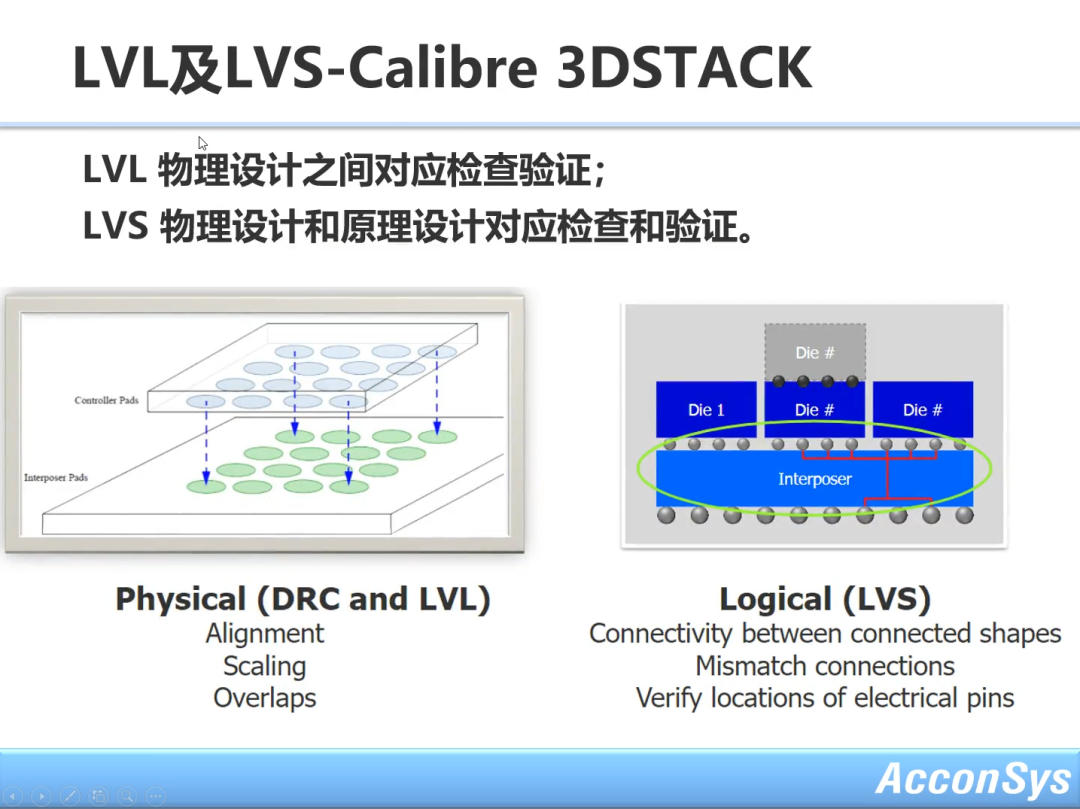

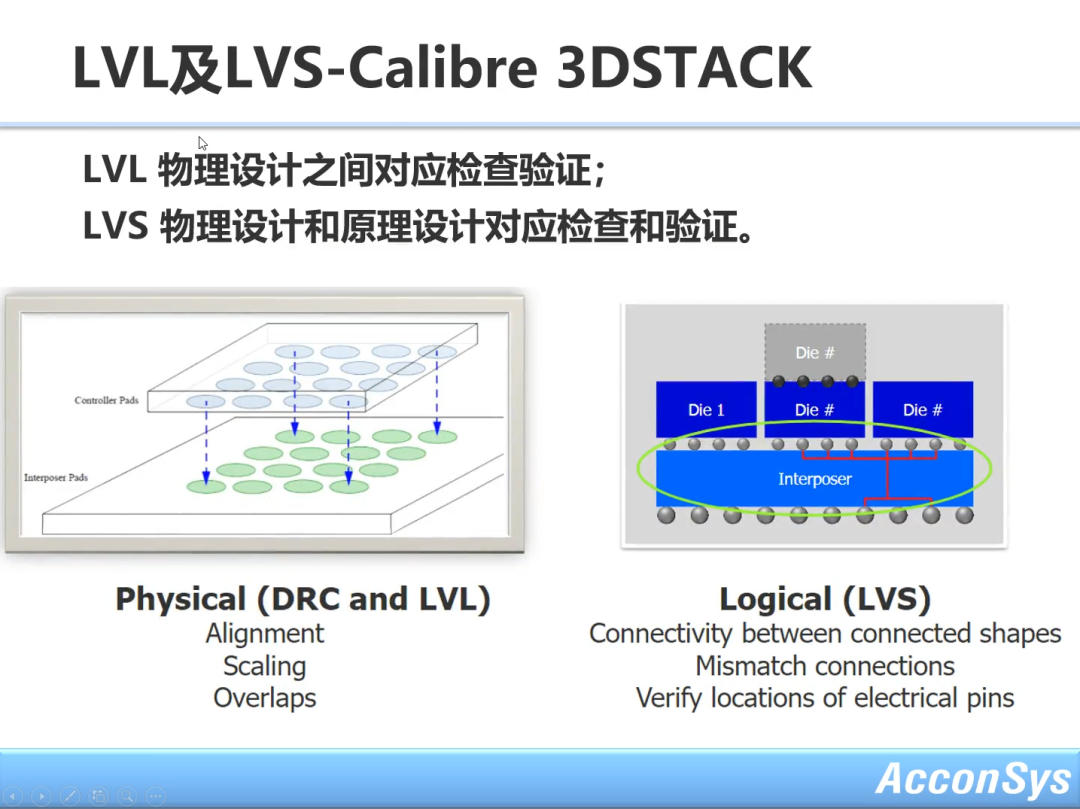

此外看到LVL和LVS的检查,LVL就指的是layout,layout为什么会有LVL是因为上下层的对准,都是物理的physical的,DRC和LVL其中有alignment对准、尺度的缩放、重叠性检查。LVS就是逻辑检查,虽然逻辑上是这么连接的,实际上最后是不是这样连接,就要通过LVS来检查,连接性是不是和电气的这种定义是一致的。

我们就看到,通过LVS检查,检查电气定义和物理连接的一致性,这个就是在Calibre 3D STACK里面能够完成的物理验证,所以在生产之前通过物理验证以后,才能够放心的去投产,如果没有通过这样的物理验证,可能在投产过程中或者是产品出来后可能会有各种各样的问题。

下面我给大家做一下总结。

前面讲了先进封装技术的概览,其中主要是讲先进封装的定义,提到几个关键词,分为几种类别,四类,实际上主要是三类,Wafer Level Package、2.5D和3D。另外还有先进封装的四要素,是我首先提出来的,大家慢慢也认可四要素,就是Bump、RDL、TSV和Wafer这四要素。

接下来讲了12种先进封装的技术及其特点,目前来说这12种先进封装技术比较流行、是比较主流的,不同企业对名称叫法也不一样,但是主要就分为这些大类。它也有各自的特点,有2D、2.5D、2.5D+3D、3D。然后讲了2.5D和3D的特点和设计要求。举个实例,就是2.5D和3D的设计的实例,通过XSI和XPD进行设计。

设计完成以后,我们对仿真方法进行了讲述,主要是针对平面设计和非平面设计,两种不同的仿真方法,仿真方法讲完了以后讲电气验证,基于HyperLynx DRC的电气验证,然后基于Calibre的物理验证。

今天的分享就到这里,关于先进封装和SIP,我写了几本书,感兴趣的读者也可以去看一下,另外我即将在CEIA电子智造的天空沙龙上开设专题课程,详细讲述半导体先进封装的相关工艺和前世今生,期待大家的关注,谢谢。

请赐点赞、转发、评论、关注

希望通过本文的交流

只是我们彼此成就的开始

因为人生所有的修炼

都只为在更高的地方遇见你

点个“在看”吧

原文始发于微信公众号(导电高研院):大咖说 | 李扬老师:先进封装的设计和验证