先进封装Chiplet 技术介绍(视频)

Hello everyone, welcome to semi content. I got a request to talk about chimney, so today's topic is chimney. Let's talk about it. Chimney is a semiconductor technology to use multiple small dyes to achieve target function, which is supposed to be done by one dice dye. Its goal is to reduce product development time and cost by integrating multiple smaller dyes in a package. A chimney is not a package type and it is part of a packaging architecture. With chimney, dice could be integrated into an existing package type, such as 2.5 d, 3 d, fan out, multi chain modules.

大家好,欢迎来到半导体内容。我接到一个讲讲关于Chiplet的请求,所以今天的话题是Chiplet。我们来谈谈吧。Chiplet是一种半导体技术,使用多种小芯粒来实现目标功能,将原本应该由一个芯粒来完成的任务,分为多种较小的芯粒集成在一起来实现。从而,减少产品开发时间和成本。Chiplet不是指封装类型,它是封装架构的一部分。通过chiplet,多种芯粒可以集成到现有的封装类型中,例如2.5D、3D、扇出及多芯片模块。

微信识别二维码观看视频

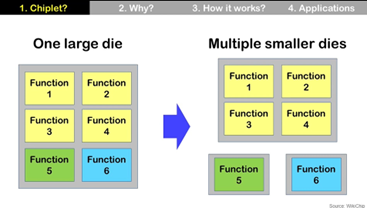

Imagine we have one large die and it has CPU, GPU and other functional blocks all in one die as soc system chip. But it is very expensive and there are many challenges to make these clients die. Fortunately, we can have all these functions by multiple smaller dyes. And economically it is more reasonable. But we need to add interface block to each die, so total die area will be more than one dodge die. That is a brief concept of chimney. So chimney is a good solution for large expensive dye, which is typically for high performance computing, rather than for a small die in smartphone. A silicone note of semiconductor advanced like 45nm,16nm and even 7nm.

想象一下,我们有一个大芯片,它有CPU,GPU,RAM及其它功能块都在一个芯片中作为SOC系统芯片。但这是非常昂贵的,并且有许多挑战使这些产品很难量产。幸运的是,我们可以通过多种较小的芯粒来实现所有这些功能,而且这样在成本上更合理。但是由于我们需要在每个芯粒上添加接口模块,所以总的所有芯粒总面积将超过全部集成在一个芯片上。这是chiplet的一个简单概念。因此,Chiplet是大型系统集成芯片的良好解决方案,通常用于高性能计算,而不是智能手机中的小芯片。一种使用先进的半导体制程如45nm、16nm甚至7nm。

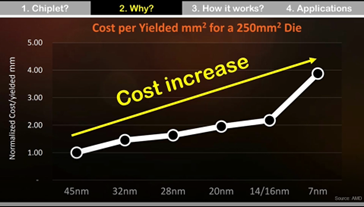

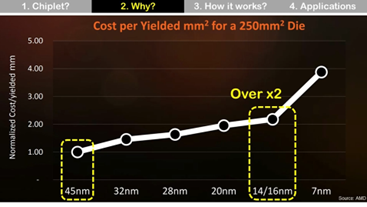

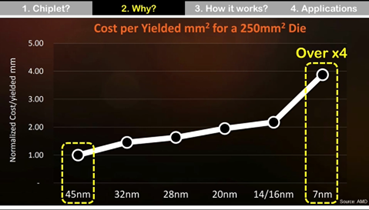

Cost for large dice continues to increase. Cost for a 16mm dye with 250mm² size is more than 2 times expensive than 45nm die with same die size. And 7nm die is more than 4 times expensive than 45nm die. Now we're talking about 5nm and even 3nm. Then cost revenue increased continuously. That means fabricating large soc dies with advanced silicone node is losing its economical benefit. That is why the industry has started to use chimney again.

随着大芯粒的成本继续增加。针对一个250mm²尺寸的芯粒,14或16纳米制程的成本是相同尺寸的45纳米芯片的2倍以上。而7纳米芯片比45纳米芯片贵4倍以上。而到我们最近谈论的5纳米甚至3纳米,成本更将不断增加。这意味着使用先进制程制造大型SoC芯片正在失去其经济效益。这就是为什么这个行业又开始使用chiplet了。

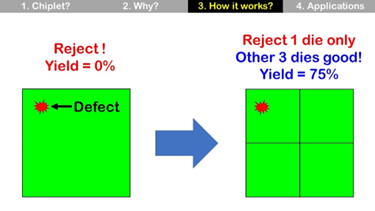

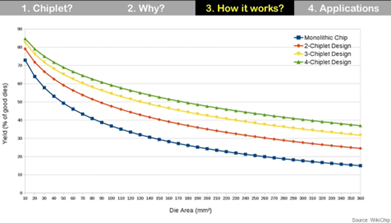

Chimney is to break down a large expensive single die into multiple smaller dyes. How it works? This is simple comparison between one dies die and 4 small dies. If there is a defect at the upper left of the die, then it is risen. One die liseth out of one die. So eld is 0. If we have 4 small dies and there is same defect at the exact same location. Then only one die is risen out of 4 dice and eld is 75%. That means we still can save 30 dice. It is more obvious for belly lies die. It also works for a dialogue at the vapor edge. At the left we have dialogues at the wafer ads for large diet. At the right we also have a dye loss, but smaller dye has higher yield than last dye. This is dialed comparison between one die versus chimney with 2,3 and 4 dies. For a 360mm² one die we'll have 15% ill but a full chimney design each 99 k millimeters will have 37 yield more than doubles. Even though the total die area of 4 chimney design is more than 10 than one die, the significant yield improvement of chimney is good enough to justify a chimney solution.

Chiplet是将大型的单一芯粒分解成多个较小的芯粒。它是如何工作的?这是一个大芯粒和4个小芯粒之间的简单比较。如果在芯粒的左上角有缺陷,则整个芯粒就无法使用,所以良率是0。如果我们有4个小芯粒,并且在完全相同的位置存在相同的缺陷。然后4个芯粒只有一个不能使用,良率为75%。这意味着我们仍然可以节省3个芯粒。它也适用于边缘DIE。在左边,我们有大量无法使用的边缘DIE。在右边,我们也有相类似的损失,但较小的芯粒比较大的芯粒具有更高的良率。这是一个芯粒与chiplet 的有2,3或4个芯粒之间的比较。对于360mm²的一个芯粒,我们仅有15%的良率。但针对4个芯粒的chiplet 设计,良率将是前者的一倍以上。即使4个芯粒的chiplet 设计的总面积比一个大芯粒多出10%,Chiplet的设计明显提高了良率和合理性。

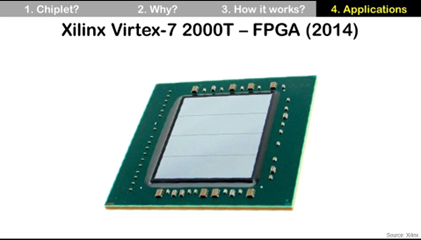

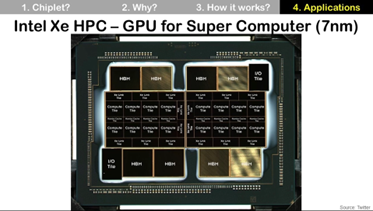

Back in 2014 fpga company gidings made vertex 72000 t and it used 4 smaller chimney dyes rather than one. Dodge fpga. This is AMD epic second generation package and it is a CPU for server using 7nm silicone note technology. Its package size is 58.5mm by 75 point 4mm. Yes, it is big. There are 8 CPUs using 7nm silicon technology and one iodi using 14nm silicon technology at the center. This is Intel xe hpc and it is a GPU using 7nm silicon technology for a supercomputer. Now Intel is using this only in the lab. It has 47 components and include 2 base tiles using Intel's 10nm sofa pin technology. 16 computer tiles using t s m c. Seven nanometer technology.

早在2014年,赛灵思生产的72000,它使用了4个较小的芯粒,而不是1个大芯片。这是AMD史诗级般的第二代封装,它是使用7nm的服务器CPU。其封装尺寸为58.5mm乘75.4mm,它非常大。中心有8个使用7nm技术的CPU和一个I/O 芯片使用14nm技术。这是英特尔XE HPC,它里面的GPU使用7nm技术,现在英特尔只在实验室中使用它。它有47个组件,包括2个基础芯片使用英特尔10nm技术。16个计算核心使用TSMC的7纳米技术。

A lambo cache tile using intel's ten nanometer enhanced super pin process. 11 MIB links made by Intel. 2 x link Io tile made by a foundry. 8 HBM memory stacks produced by a dealer manufacturer. It ought to be impossible to build a single chip with these 47 components. Even though chimney has lots of benefit, it also has some challenges. We need to think about die to die interconnection, code design by chip designer and package designer. Easily required tests for small dies will be different from one large dies, etc. Thanks for watching and have a nice day. Bye bye.

11个缓冲使用英特尔十纳米技术,2 个I/O芯粒由代工厂代工。8个HBM存储器堆栈由存储厂加工。没有chiplet技术,是不可能将47个芯粒的功能一次性在单个芯片上加工完成的。尽管chiplet有很多好处,但它也有一些挑战。我们需要思考芯片到芯片的互连,芯片设计师和封装设计师的协同,多个小芯粒的测试也将非常不同于一个大芯粒的测试等。

微信识别二维码观看视频