1 SiP项目成功的三要素

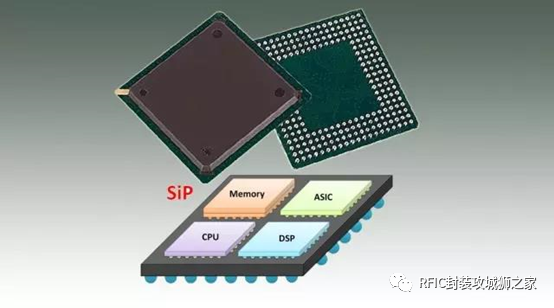

做SiP项目的人,都希望项目能够一次成功,取得同行和领导的认可,从而争取更多的项目和经费支持。那怎么才能使项目一次成功呢?这就需要我们把握好SiP项目成功的三要素,那就是:裸芯片、设计仿真、生产制造。

1.1 裸芯片

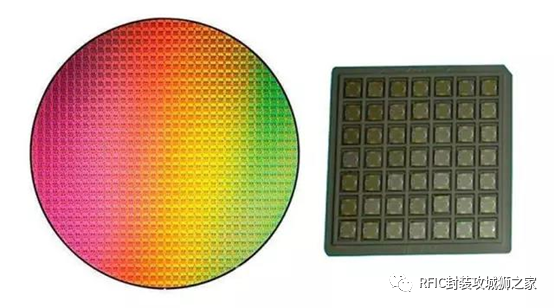

裸芯片(die,bare die,bare chip),通常是指半导体元器件制造完成,封装之前的产品形式。裸芯片通常是以晶圆形式(wafer form)或单颗芯片(die form)的形式存在,封装后成为半导体元件、集成电路、或更复杂电路例如系统级封装SiP的组成部分。

在国内,由于国外芯片禁运等原因,很多国外芯片难以购买,对于裸芯片更是如此。经常一款SiP项目中需要的部分裸芯片无法购买到,这时该项目就难以继续。根据以往的经验,通常的解决方法有以下四种:

-

采用国产芯片代替,目前国产芯片也是遍地开花,通常国际上比较著名的芯片厂商的产品在国内都可以找到对应的替代品,虽然在性能和容量等方面还无法达到国际同类产品的水准,但很大程度上已经能满足SiP项目的需要了。

-

采用同类芯片代替,例如AD,DA、运放类裸芯片,很多功能相近,可以通用,满足设计指标的前提下,可以用可购买到的同类芯片替代。

-

更改设计方案,对设计方案进行合理的裁剪,例如一个完整的计算机系统并不一定要完全在一个SiP中实现,可以分成例如系统主控SiP,数据处理SiP,接口管理SiP等,这样就比较容易首先实现某一部分功能的SiP了。

-

实在找不到裸芯片但还必须在项目中用的芯片,可以采用小封装例如CSP,QFN等代替,这个需要提前和生产厂家沟通工艺兼容性问题。

以上四种方法在实际项目中都有应用,也取得了良好的效果,用户最终都做出了满意的SiP产品,实现了应有的功能。

1.2 设计仿真

目前,SiP设计软件有两个厂家提供,Mentor和Cadence,SiP仿真软件则有Mentor、AnSys、Cadence、ADS等多家。每家软件都有各自的特点和优势,这里我们不准备详述各个软件的功能比较,后面的的文章,我会专门对各家软件进行描述并对其功能进行比较。

-

针对设计软件,主要需要考虑其功能时是否对键合线(Wire Bonding)、芯片堆叠(Die Stacks)、腔体(Cavity)、倒装焊(Flip Chip)及重分布层(RDL)、埋入式无源元件(Embedded Passive)、参数化射频电路(RF)、多版图项目管理、多人实时协同设计、3D实时DRC等最新的SiP技术能有较好的支持。

-

针对仿真软件,主要需要考虑能否方便地将设计数据导入,并能够正确识别各设计元素;是否具备SI、PI、EMI、热、电磁场等仿真功能,仿真精度、仿真速度能否满足项目要求等。

另外,除了软件本身的功能外,还需要重点了解各个厂家对技术支持的重视程度和技术支持人员的经验水平等因素,因为很多用户初次接触SiP项目,软件厂家技术人员的经验水平对项目成功起到重要甚至决定性的作用。

1.3 生产制造

一款SiP设计完成后,必须选择合理并且靠谱的生产厂家,才能够保证项目的最终成功。

一般情况下,塑料封装、陶瓷封装、金属封装的生产工艺完全不同,其设计规则定义也会差别很大,所以要根据项目情况提前考虑选择不同类型的生产厂家。

在项目设计的过程中就需要提前和相关厂家取得联系,获取厂家的工艺能力和生产制造要求,并以此为依据定义设计规则,这样设计出的产品才能满足生产制造的要求,即所谓的可制造性设计DFM(design for manufacture)。

厂家往往为了争取更多项目,常常也会将其极限的生产能力报给用户,这时候我们就需要合理的考核其常规生产能力和极限生产能力,尽量在其常规生产能力范围内进行设计,这样就避免了成品率过低或者价格过高的问题。

另外,还需要了解厂家是否完全具备【基板+封装+测试】的能力,还是只具备其中某一种能力,其它需要通过外协来完成,此时需要和厂家协商好如何保证产品质量和进度,避免由于生产环节周期过长而造成的项目延误。

2 如何选择SiP产品工艺和材料

对于一个新的SiP产品或者项目,设计师首先需要了解的就是采用什么样的工艺和材料来实现SiP产品,不同的选择会带来哪些不同,成本、周期有多大的区别?

SiP系统级封装产品按工艺或材料通常主要分为:塑料封装SiP、陶瓷封装SiP和金属封装SiP三种类型,参看图1。

图1 三种不同工艺材料的SiP封装类型

每种类型的 SiP产品都有其特点和优势,需要设计师根据项目的用途、项目周期、项目经费情况进行合理选择。

2.1 塑料封装SiP

塑料封装SiP通常称为塑封SiP,主要应用于商业级产品,具有低成本优势,但在芯片散热、稳定性、气密性方面相对较差。其特点主要总结如下:

-

密封性稍差,无法阻挡湿气和腐蚀性气体对芯片的腐蚀;

-

不容易拆解,模封灌胶后,几乎无法打开,否则损坏芯片;

-

散热性能较差,因为有机基板和模封胶的传热系数低;

-

工作温度范围小,一般温度范围为0℃~+70℃,工业级的是-40℃~+85℃;

-

生产周期短,一般生产周期2~3个月;

-

价格便宜,成本低廉,一次打样需要人民币10万元左右;

-

适合大批生产,在商业领域得到广泛的应用。

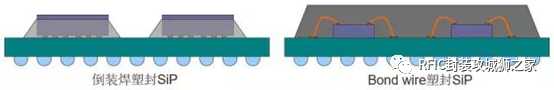

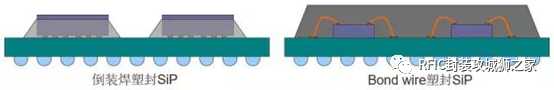

塑料封装SiP一般采用有机基板对芯片进行互联和承载,然后通过模封灌胶的方式对芯片进行加固和密封,其结构如图2所示。

图2 塑封SiP的结构

2.2 陶瓷封装SiP

陶瓷封装SiP多用于工业级产品、军品以及航空航天、军工等领域,其散热优良,气密性好、可靠性高。同时,陶瓷具有可拆解的优势,便于故障查找和问题“归零”。其特点主要总结如下:

-

密封性好,可以做到气密性,阻挡湿气和腐蚀性气体;

-

散热性能好,陶瓷基板外壳的热传导系数比较大,利于芯片散热;

-

对极限温度的抵抗性好,陶瓷封装工作温度可达到军品要求-55℃~+150℃;

-

容易拆解,便于问题分析,陶瓷封装体内部芯片都处于真空裸露状态;

-

体积小,适合大规模复杂芯片,主要相对与金属封装而言;

-

生产周期长,一般生产周期6~8个月;

-

价格高,一次打样需要人民币40~100万元左右;

-

适合军品和航空航天应用,目前在全球军工和航空航天领域应用普遍。

陶瓷封装SiP一般采用HTCC陶瓷基板对芯片进行互联和承载,其外壳和基板通常为一体,结构多采用腔体结构,用可伐合金焊接密封,其结构如图3所示。

图3 陶瓷封装SiP的结构

2.3 金属封装SiP

金属封装SiP和陶瓷封装SiP类似,多用于工业级产品、军品以及航空航天、军工等领域,其气密性好、可靠性高,散热优良。金属封装也可拆解,便于故障查找和问题“归零”。其特点主要总结如下:

-

金属封装密封性好,可以做到气密性,阻挡湿气和腐蚀性气体;

-

散热性能好,对极限温度的抵抗性好;

-

容易拆解,开盖后即可直接看到内部裸芯片;

-

体积较大,扇出引脚较少,不太适合复杂芯片;

-

通常用在MCM领域,射频微波,模拟SiP领域应用较多;

-

生产周期较长,一般生产周期4~6个月;

-

价格较高,一次打样需要人民币30~80万元左右;

-

适合军品和航空航天应用。

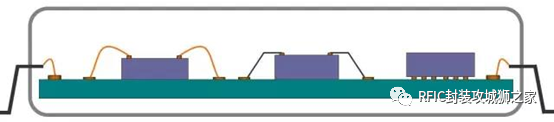

金属封装SiP一般采用LTCC、厚膜或者薄膜陶瓷基板对芯片进行互联和承载,其基板和外壳独立进行设计和加工,基板采用粘结法固定到金属外壳上,电气上采用Bond Wire和外部引脚连接,其结构如图4所示。

图4 金属封装SiP的结构

看了上面的描述,设计者结合项目的实际情况,就能确定选择什么样的工艺和材料来完成自己的SiP项目和产品了。

3 SiP基板选择——有机基板

SiP基板系列文章

在SiP系统级封装中,基板作为整个封装的载体,起着支撑和电气互联的作用,目前,常用的基板包括有机基板、陶瓷基板、硅基板等等,我们将逐一介绍,这篇文章,我们主要来讨论有机基板。

图4 基板

1

3.1 有机基板的材料

有机基板一般是由有机树脂和玻璃纤维布为主要材料制作而成,导体通常为铜箔。有机树脂通常包括:环氧树脂(FR4),BT树脂(双马来酰亚胺三嗪树脂),PPE树脂(聚苯醚树脂),PI树脂(聚酰亚胺树脂)等。

有机基板常用的铜箔厚度为17μm(半盎司),35μm(一盎司),70μm(两盎司)等多种。柔性有机基板铜箔厚度比较薄,5μm、9μm、12μm等规格的铜箔在柔性板上应用较多。铜箔厚度和载流量成正比关系,如果需要通过比较大的电流,则需要选择较厚的铜箔和较宽的布线。

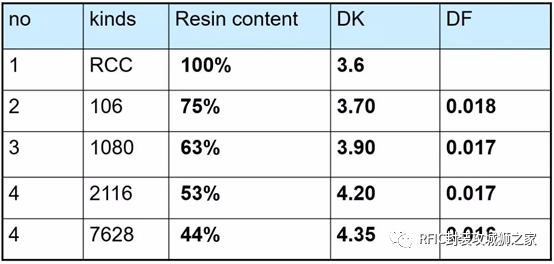

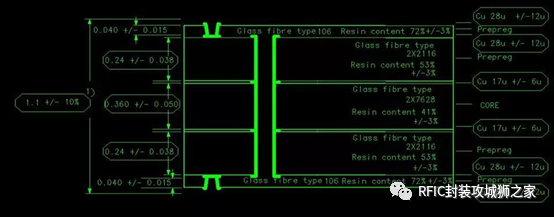

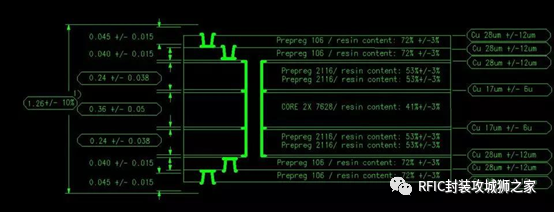

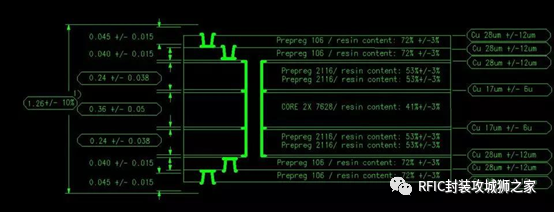

以FR4为例,介质材料根据树脂和玻璃纤维含量的不同,可分为106,1080、2116、7628等多种型号。一般型号数值越大,树脂含量越少,玻璃纤维含量增大,硬度增加,介电常数也越高。例如,106树脂含量75%,1080树脂含量63%,2116树脂含量53%,7628树脂含量44%。另外,还有一种RCC(Resin Coated Copper),树脂含量100%。树脂含量越多,材质越软,激光打孔效率高。

下图为不同型号的介质材料的树脂含量、介电常数DK及损耗因子DF

通常为了兼顾各方面的性能,SiP基板会采用多种型号的基材,一般表层用树脂含量较高的,例如RCC,106,1080,而内层则采用硬度较大的例如2116,7628,用于增强支撑强度,详见下面基板层叠结构实例图示。

2

3.2 有机基板的特点

-

有机基板有其自身的特点和优点,和陶瓷基板相比,有机基板不需要烧结,加工难度较底,并且可制作大型基板,同时具有成本优势,另外有机基板介电常数低,有利于高速信号的传输。

当然,有机基板也有自身的劣势,例如传热性能较差,传热系数通常只有0.2-1W/(m·K)之间,而氧化铝陶瓷材料可以达到18W/(m·K)左右,氮化铝更是可达到200W/(m·K)左右。 -

此外,有机基板的CTE也通常相对芯片比较大,这样就容易在热循环的时产生和IC的焊接处电气连接失效。

-

CTE(Coefficient of Thermal Expansion)是指热膨胀系数α ,理想的封装基材:α < 8×10-6/ºC,或者为8ppm/ºC,(ppm-parts per million,百万分之一)。

-

半导体芯片的主要成分是硅,而硅的膨胀系数只有2.5ppm/ºC,如果半导体芯片与基板的热膨胀系数相差过大,在温度变化时,它们之间产生较大的应力。因此,为了保证SiP或者封装基板微细电路的精度,适宜用低热膨胀系数的基板材料。

-

Tg玻化温度,是板材在高温受热下的玻璃化温度,一般Tg的板材为140度以上,高Tg一般大于170度,中等Tg约大于150度。Tg值越高,板材的耐温度性能越好 ,印制板的耐热性、耐潮湿性、耐化学性、耐稳定性等特征都会提高和改善。尤其在无铅制程中,高Tg应用比较多。目前,高耐热性基板的Tg通常可以达到200度以上。

3

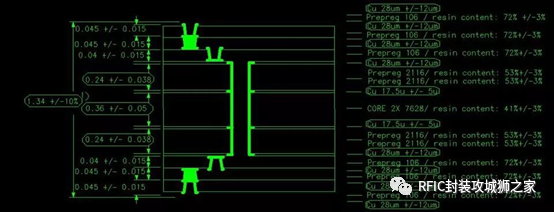

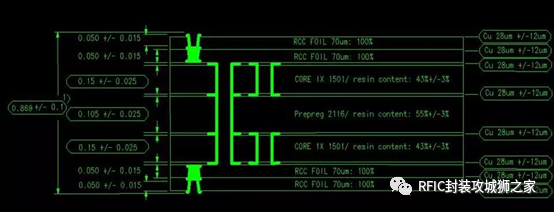

3.3 有机基板层叠结构

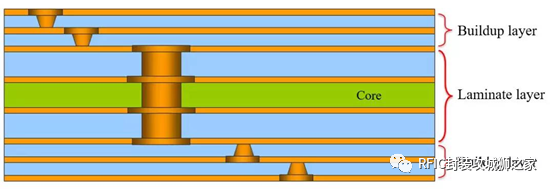

SiP或封装基板通常采用盲埋孔结构,这里我们用m+N+m代表,其中m代表Buildup层,采用积层法工艺进行制作,通常采用激光钻孔,每次只钻一层,层层往上累积成多层,因而被称为积层法,积层法英文为:Buildup。

N代表Laminate层,采用层压法工艺进行制作,通常采用机械钻孔,先将多层叠加在一起压合,然后统一钻孔,层压法英文为:Laminate。

-

下图为2+4+2的8层基板侧面示意图:

Buildup层的盲埋孔是可以叠加的,但一般不能与Laminate层的通孔叠加,这主要是由于生产工艺的限制。这个两类孔叠加容易出现断路。

下面几张图是有机基板层叠结构的实例(可放大查看每层所用的材料型号和铜箔的厚度)。

-

下图为6层基板,其层叠结构为1+4+1

-

下图为8层基板,其层叠结构为2+4+2

-

下图为8层基板,其层叠结构为1+1+4+1+1

-

下图为10层基板,其层叠结构为2+1+4+1+2

-

下图为8层基板,其层叠结构为2+4+2,机械孔又包含更复杂的多次打孔工艺

-

下图为10层基板,其层叠结构为3+4+3,机械孔层又包含更复杂的多次打孔工艺

3.4 有机基板的选用

有机基板主要应用于塑封器件,由于其具有成本上的优势,目前是应用最为广泛的SiP封装基板。

SiP或者封装设计者在选用有机基板时,要综合考虑成本和可靠性进行选择,主要考虑其热膨胀系数,玻化温度,吸湿性能等。从而选择FR4(环氧树脂),BT树脂(双马来酰亚胺三嗪树脂),PPE树脂(聚苯醚树脂)PI树脂(聚酰亚胺树脂 polyimide)等基板。

同时,需要设置合理的铜箔厚度和层叠结构,选用不同型号的基材,控制好介电常数DK和损耗因子DF,从而使SiP或封装的性能在成本优化的前提下达到最优。

4 陶封SiP为何多采用腔体结构

SiP系统级封装产品按工艺或材料通常分为:塑料封装SiP、陶瓷封装SiP和金属封装SiP几种类型和各自的特点。

其中陶瓷封装SiP也简称为陶封SiP,美国航空航天局NASA,欧洲太空局ESA采用的SiP基本上均为陶瓷封装SiP。目前,国内领先的航空航天和军工领域的研究所都开始研究和应用SiP技术,他们也不约而同地选择陶瓷封装作为首选的SiP产品封装。

陶封SiP密封性好,散热性能好,对极限温度的抵抗性好,容易拆解,便于问题分析,相对于金属封装体积小,适合大规模复杂芯片。有了这些优点,陶封SiP确实最适合在极限苛刻环境中应用的航空航天等军工领域。

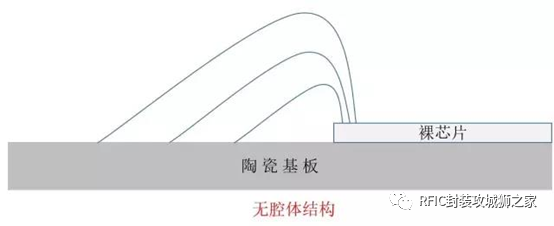

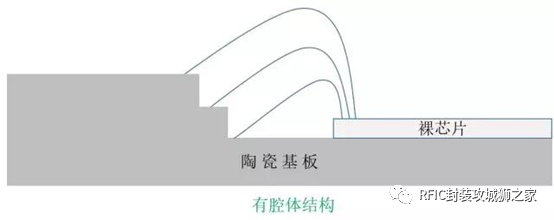

在陶封SiP设计中,有一个最明显的特征就是:陶封SiP中基本都采用了腔体结构。

4.1 什么是腔体?

在《SiP系统级封装设计与仿真》一书中,我这样写道:“腔体Cavity是在基板上开的一个孔槽,通常不会穿越所有的板层(在特殊情况下的通腔称之为Contour)。腔体可以是开放式的,也可以是密闭在内层空间的腔体,腔体可以是单级腔体也可以是多级腔体,所谓多级腔体就是在一个腔体的内部再挖腔体,逐级缩小,如同城市中的下沉广场一样。”

下图是城市中常见的下沉广场,底部区域供人们活动,台阶可以当看台或者坐下休息。

城市中常见的下沉广场

下图是陶封SiP中常见的腔体结构,底部区域安装芯片,多级腔体的台阶上可以放置键合指Bond Pad。两者唯一的区别就是下沉广场多为圆形,而陶封SiP中的腔体多为方形,当然也不排除有些项目中采用了圆形腔体。

陶封SiP中常用到的腔体结构

4.2 陶封SiP为何基本都会采用腔体?

搞明白了腔体的定义后,我们再来看看陶封SiP为何基本都会采用腔体?根据亲自参与的多个陶封SiP实际项目,我总结了一下,大致有以下三种原因:

-

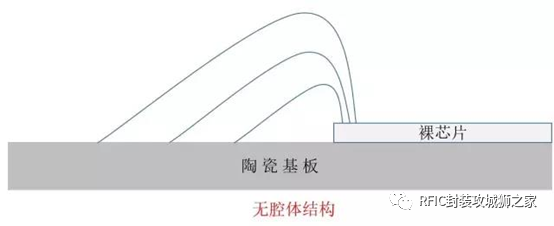

腔体结构有利于键合线的稳定性

对于复杂的芯片,常常要采用多层键合线,键合指的排列经常有3-4排,这样外层键合线就会很长,跨度很大,不利于键合线的稳定性,而腔体结构则能有效改善这种问题。从下面两张图就可以明显地看出腔体结构大大减小了键合线的长度,从而有效地提高了键合线的稳定性。

-

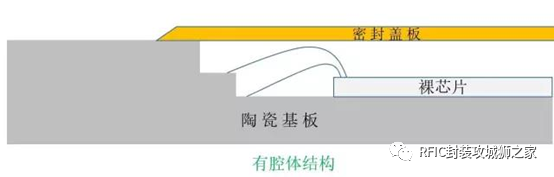

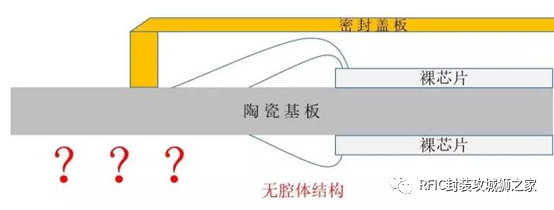

腔体结构有利于陶瓷封装的密封

采用腔体结构的陶瓷基板,芯片和键合线均位于腔体内部,只需要用密封盖板将SiP封装密封即可。如果无腔体结构,则需要专门焊接金属框架来抬高盖板的位置,这样就多了一道焊接工序,其焊缝的气密性也需要经过严格考核才能达到气密性要求。

-

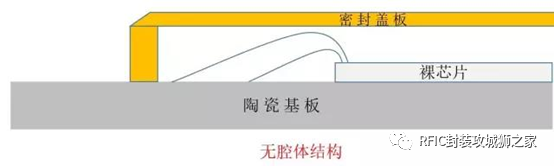

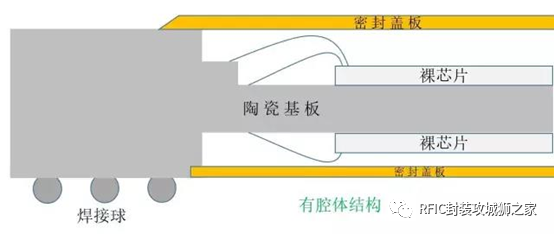

腔体结构有利双面安装元器件

现在的SiP复杂程度很高,需要安装的器件很多,在基板单面经常无法安装上所有器件,需要双面安装器件。这时候,腔体结构也就大有用武之地,通过腔体可以将一部分器件安装在SiP封装的底面,在封装底面外侧设计并植上焊接球,如下图所示。

如果没有腔体结构,就无法在背面安装器件,如下图所示:

如果将器件完全安装在顶面,不可避免要扩大封装的面积,和SiP小型化的概念是背道而驰的。

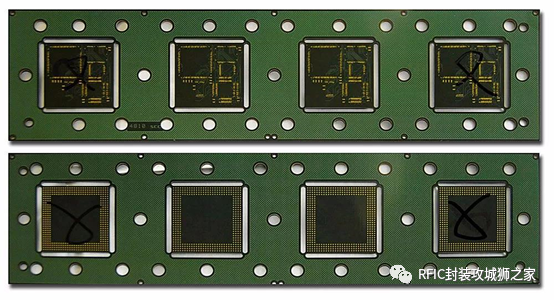

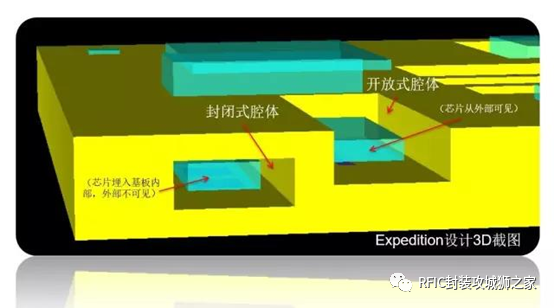

最后,我们来看一款实际的陶瓷封装SiP项目的Expedition设计截图:此项目为国内第一款采用双面腔体的陶封SiP项目,完全在一颗SiP中实现了航天计算机的所有功能,并达到军品级要求。该项目在世界上也处于领先地位,目前已经成功应用到多个航空、航天等重点工程中。

5 如何将元器件埋置在SiP基板内

将元器件埋置在基板内是一个非常有效地缩小SiP面积的方法,同时能有效减少基板表面的焊点,提高其可靠性,那如何将器件埋入到SiP基板内呢?

通俗来说有两种方法:

-

挖个坑埋进去;

-

压扁了嵌进去。

第一种方法用专业的术语来讲就是:通过腔体技术将分立元器件埋入基板。 第二种方法用专业的术语来讲就是:通过特殊材料制作电阻、电容等无源器件并嵌入到板层之间。

5.1 通过腔体的技术将分立元器件埋入基板

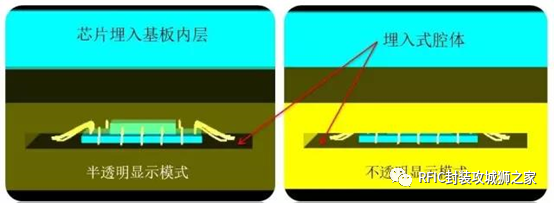

腔体主要是以开放式腔体为主,实际上还有一种腔体称为埋置腔体,也称为封闭式腔体,参看下图,这样分立器件就可以埋入基板内部了。

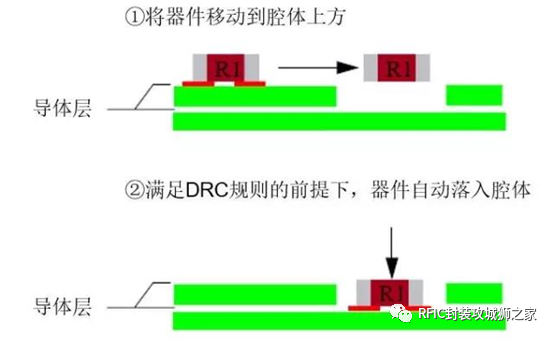

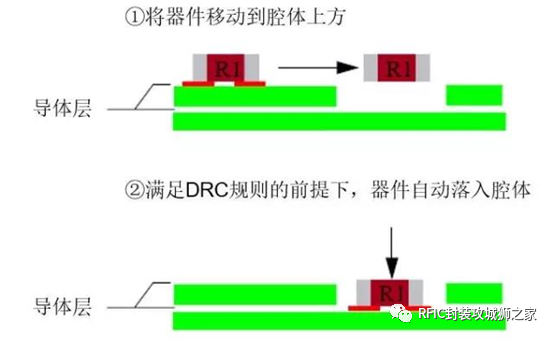

具体在设计中怎么实现呢?大致分为三步:

-

在基板上绘制正常的开放式腔体;

-

将元器件放置到腔体中,器件自动落入腔体;

-

将腔体属性更改为封闭式腔体。

设计方法看起来是不是很容易,这种技术适合所有的芯片类型,具体设计方法可参考《SiP系统级封装设计与仿真》一书第12章。

5.2 通过特殊材料制作电阻、电容等无源器件并嵌入到板层之间

这种技术目前应用也很广泛,主要是通过阻性、容性材料制作电阻或者电容,然后在基板层压的时候,嵌入到基板内部层之间或者直接制作在基板表面,这种方法制作的阻容基本没有高度,不会影响基板的厚度。

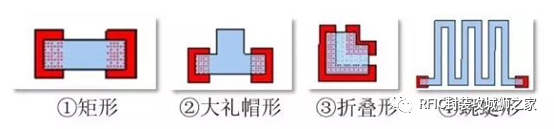

下图是4种常见的电阻形状,注意不同的阻值要选择合适的阻性材料,才能做出大小合适的埋入式电阻。

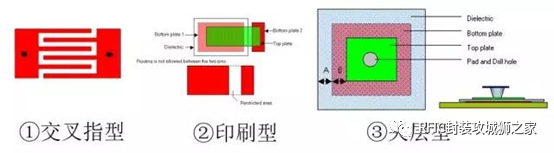

下图是3种常见的电容结构,同样要选择合适的材料,才能做出结构和大小都合适的埋入式电容。

目前在国内,平面式埋置电阻应用比较多,在SiP、MCM、厚膜、薄膜电路中应用普遍,一般制作在基板的表面层,这样方便后续的激光调整。平面式埋置电容应用相对较少,主要是工艺比较复杂,例如印刷型电容需要至少3层材料,而夹层型更为复杂,除了多层材料外,还需要通过过孔将相邻的层连接起来。

在设计工具方面,Mentor的工具对此功能支持的比较好,全部在菜单中即可完成电阻、电容的自动综合功能。

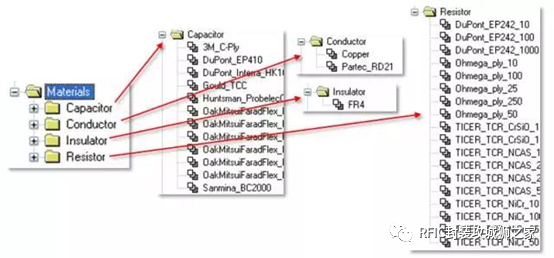

另外,采用第二种方法,需要对材料特性有比较详细的了解,下图列出了部分阻容材料,不同的材料有不同的特性,只有选择了合适的材料,才能做出最优的埋置电阻或电容。具体设计方法可参考《SiP系统级封装设计与仿真》一书第15章。

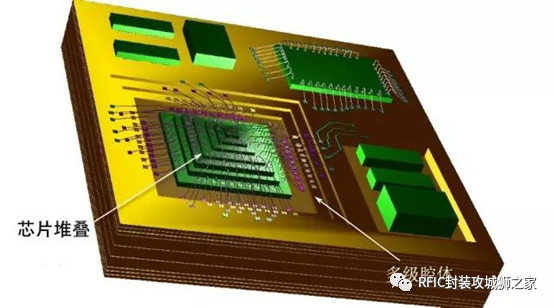

6 芯片堆叠技术在SiP中的应用

芯片堆叠技术在SiP中应用的非常普遍,通过芯片堆叠可以有效降低SiP基板的面积,缩小封装体积。

目前来看,芯片堆叠的主要形式有四种:金字塔型堆叠,悬臂型堆叠,并排型堆叠,硅通孔TSV型堆叠。

为什么芯片可以进行堆叠呢?这里面我们讲的主要是未经过封装的裸芯片。曾经有用户问我,封装好的芯片可不可以进行堆叠呢?一般来说是不可以的,因为封装好的芯片引脚在下表面直接焊接到基板上,而裸芯片的引脚一般在芯片上表面,通过键合的方式连接到基板。正是由于裸芯片引脚在上方,和基板的连接方式比较灵活,才有了芯片堆叠的可行性,参看下图。

6.1 金字塔型堆叠

金字塔型堆叠是指裸芯片按照至下向上从大到小的方式进行堆叠,形状像金字塔一样,故名金字塔型堆叠,这种堆叠对层数没有明确的限制,需要注意的是堆叠的高度会受封装体的厚度限制,以及要考虑到堆叠中芯片的散热问题。金字塔型堆叠参看下图。

6.2 悬臂型堆叠

悬臂型堆叠是指裸芯片大小相等,甚至上面的芯片更大的堆叠方式,通常需要在芯片之间插入介质,用于垫高上层芯片,便于下层的键合线出线。这种堆叠对层数也没有明确的限制,同样需要注意的是堆叠的高度会受封装体的厚度限制,以及要考虑到堆叠中芯片的散热问题。悬臂型堆叠参看下图。

6.3 并排型堆叠

并排堆叠是指在一颗大的裸芯片上方堆叠多个小的裸芯片,因为上方小的裸芯片内侧无法直接键合到SiP封装基板,所以通常在大的裸芯片上方插入一块硅转接板,小的裸芯片并排堆叠在硅转接板上,通过键合线连接到硅转接板,硅转接板上会进行布线,打孔,将信号连接到硅转接板边沿,然后再通过键合线连接到SiP封装基板。并排型堆叠参看下图。

6.4 硅通孔TSV型堆叠

硅通孔TSV型堆叠一般是指将相同的芯片通过硅通孔TSV进行电气连接,这种技术对工艺要求较高,需要对芯片内部的电路和结构有充分的了解,因为毕竟要在芯片上打孔,一不小心就会损坏内部电路。这种堆叠方式在存储领域应用比较广泛,通过同类存储芯片的堆叠提高存储容量。目前也有将不同类芯片通过TSV连接,这类芯片需要专门设计才可以进行堆叠。TSV型堆叠参看下图。

上面介绍的是SiP设计中四种最基本的芯片堆叠方式。

在实际应用的时候,这几种堆叠方式可以组合起来形成更为复杂的堆叠。另外,还有通过将键合芯片和倒装焊芯片进行堆叠,通过柔性电路折叠的方式对芯片进行堆叠,以及通过POP形式的堆叠等几种,这些芯片堆叠方式在SiP设计中也比较常见。

7 SiP设计仿真流程

SiP设计与仿真流程的主要内容如下图所示:

-

设计准备

设计准备的工作主要包括:① 各种资料的收集,裸芯片相关资料,管脚定义,物理尺寸,能否采购获取等。②封装类型的确定,是采用BGA封装还是其他封装形式;封装尺寸的确定;封装管脚间距、管脚数目的确定。③采用自定义管脚排列方式还是采用标准的封装,或者和别人曾经用过的封装管脚兼容,以便于后期的组装和测试。④封装工艺和材料的选择,根据其应用的领域选择塑封、陶瓷封装或者金属封装。

-

建库及库管理

建库及库管理主要包括原理图符号库、IC裸芯片库、BGA封装库、Part库以及仿真模型库等。

-

原理图设计

原理图设计包括原理图输入,射频原理图设计以及原理图协同设计等。

-

设计前仿真

设计前仿真可和原理图设计同步进行,通过“What if”分析,确定设计层叠结构、关键信号的网络拓扑结构、阻抗匹配,以及电源平面的分割、电容种类及型号选择等。对模拟电路或者数模混合电路,可进行电路的功能仿真。

-

工艺选择

工艺选择主要是为了确定SiP采用哪种工艺的封装形式,如Wire Bonding、FlipChip、TAB、TSV等。基板上是否要挖腔体,采用单面腔体还是基板顶层/底层双面腔体,以及腔体的深度等,同时也要考虑是否要做芯片堆叠Stacked Dies,基板的层数和需要采用的层叠结构等通常在这一步也要定下来。

-

进入版图设计环境

通过打包Package功能,以及前向标注等手段将原理图的连接关系、规则定义等传输到版图环境,同时自动调用中心库的相关 Cell放到版图设计环境中。

-

层叠设置

根据工艺的选择及设计的复杂程度进行层叠结构的设置,包括层数以及层叠结构的选择,是采用1+N+1、2+N+2、m+N+m或者ALIVH等层叠结构。

-

约束规则设置

主要包括网络分类,结构约束规则、间距约束规则、电气约束规则,高速网络约束、差分对约束等。

-

器件布局

主要确定裸芯片的摆放位置。如果芯片需要放置到腔体里,则需要确定腔体的深度以及是单级还是多级腔体,腔体形状的绘制等。

-

引线键合、布线和敷铜

主要确定键合线的键合方式,是单层键合线还是多层键合线,键合线的模型选择,电源环的设置;选择交互式手工布线或自动布线,电源平面层分割,射频电路设计,埋阻埋容的自动综合等。这一步工作量比较大。

-

版图设计检查

通过检查可发现版图设计中的DRC错误并进行修正,确保设计功能的正确性。

-

设计后仿真

设计后仿真可通过专用接口导出到仿真工具,进行信号完整性、电源完整性及电磁兼容方面的仿真和分析。

-

设计热分析

可通过专用接口导入热分析工具。通过热分析,可解决SiP工作中由于芯片功耗过大而发生的过热问题,确保产品的稳定性和可靠性。

-

后处理及生产文件

包括Gerber及钻孔文件的生成,BOM、DXF、IDF、GDSII、ODB++等格式的输出。

-

电子结构一体化设计

电子结构一体化主要包括电子和结构的协同。因为EDA工具主要完成的是SiP内部的东西,包括基板和芯片组装、键合等。而SiP的外壳等数据通常需要通过结构设计软件来确定,如陶瓷封装的金属框架、盖板、塑封的模封,金属封装的外壳等。

-

设计结束

所有上面的流程走完之后,SiP设计结束,即可进入生产阶段。

参 考 书 籍

目前,在国内,越来越多的电子设计工程师开始关注和学习SiP的技术,但由于目前关于SiP设计和仿真方面的综合书籍很缺乏,设计者往往无从下手,这在一定程度上也阻碍了SiP技术在国内的快速发展。Mentor Xpedition是一款专业的SiP设计工具,包括原理图设计、版图布线设计、电学分析及热分析等模块,可以实现芯片堆叠、基板堆叠、复杂腔体结设计,是一款真正意义上的3D设计工具。

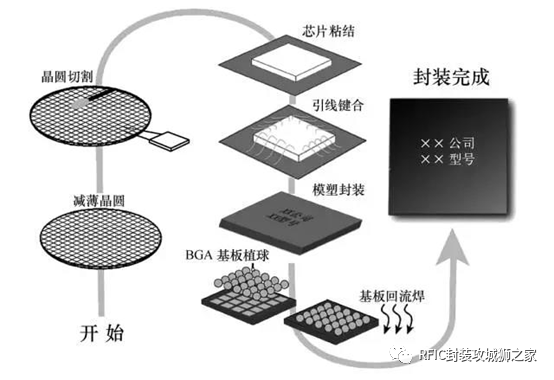

8 SiP 生产流程

SiP的封装形式多样,按照材料和工艺通常分为塑料封装、陶瓷封装和金属封装三大类,每类都会有多种类型的封装形式,例如,DIP、SOP、PLCC、QFP、QFN、BGA 等。

当前,随着引脚数量和密度的增加,BGA成为SiP最常采用的封装形式。

下面,我们就以BGA塑料封装的SiP生产流程作为介绍,基本上就可以代表SiP封装的基本生产流程,其它封装形式流程大同小异。当然,对于陶瓷封装和金属封装,其工艺流程还是有所区别,我们可以后续再讨论。

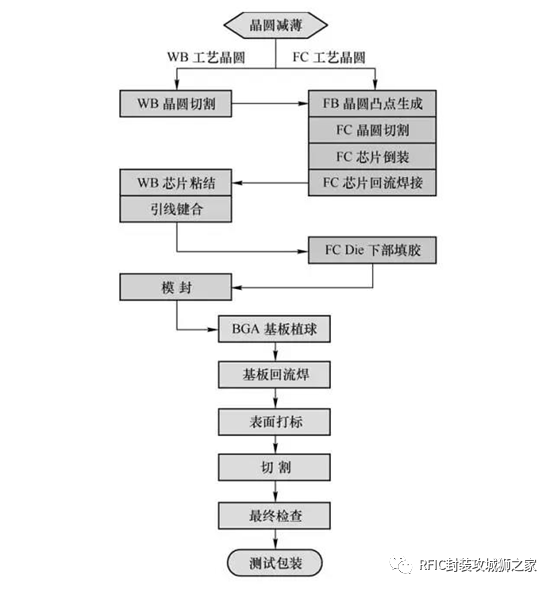

按照裸芯片和基板的连接方式,我们将BGA分为Wire Bonding BGA和FlipChip BGA。

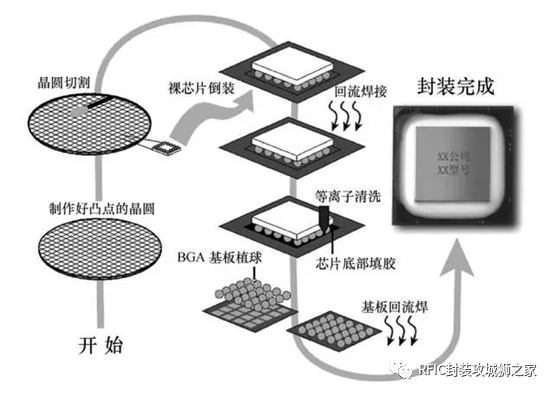

下图是Wire Bonding BGA(简称WB-BGA)的生产制造流程示意图。

Wire Bonding -BGA的流程包括:晶圆减薄→晶圆切割→芯片粘结→引线键合→模塑封装→BGA基板植球→基板回流焊→表面打标→切割分离→最终检查→测试包装。

Wire Bonding -BGA封装前,晶圆首先会做减薄处理,这样也更便于晶圆切割,同时也会减小封装后的厚度。芯片粘结是采用环氧粘结剂将IC芯片粘结在基板上。引线键合是采用纯金丝键合线将芯片管脚与基板上的Pad进行连接,接着采用模塑包封或液态胶灌封,以保护芯片、焊接线和焊盘。BGA基板植球是使用植球机或者筛网将焊料球放置在焊盘上,然后在回流焊炉内进行回流焊接,然后使用清洗剂对基板进行清洗,以去除残留在封装体上的焊料和纤维颗粒。然后是表面打标、切割分离,最终检查、测试和包装入库。

了解完Wire Bonding BGA的生产流程,我们再来看看FilpChip-BGA。

下图是FilpChip-BGA(简称FC-BGA)的生产制造流程示意图。

FilpChip-BGA的流程包括:晶圆减薄→晶圆凸点生成→晶圆切割→芯片倒装→回流焊接→裸芯片下部填胶→表面打标→BGA基板植球→基板回流焊→切割分离→最终检查→测试包装。

FilpChip-BGA封装前,晶圆同样会做减薄处理,然后在晶圆上制作凸点Bump。之后进行晶圆切割,再将芯片倒装焊接到基板上。焊接好后进行清洗,芯片底部填胶等操作,以固定芯片并克服由于芯片和基板CET不一致而导致的应力。BGA基板植球、回流焊接、清洗、打标、切割、测试、包装等流程与Wire Bonding-BGA基本一致。

通过两种工艺的对比,可以看出,两者的基本的流程是一致的,主要区别在于FlipChip倒装焊在切割晶圆片之前要生成芯片的凸点,然后进行芯片倒装、回流焊接等一系列流程。

FlipChip整个工艺流程需要两次回流焊,包括芯片回流焊和BGA基板回流焊。而Wire Bonding则需要芯片粘结、键合、模封等过程,整个工艺流程只需要一次回流焊。

对于SiP系统级封装,由于是多个芯片,就有可能会遇到混合工艺的情况,即在一颗SiP封装中既有WB芯片,也有FC芯片。目前,在实际应用中这种情况已经比较常见,在设计中经常会遇到,如所选的裸芯片中有支持WB工艺的芯片,也有支持FC工艺的芯片,就需要做混合工艺SiP的生产制造。

下图为混合工艺SiP 生产制造流程图。

原文始发于微信公众号(RFIC封装攻城狮之家):SiP项目成功的三要素