在一个晶圆上,通常有几百个至数千个芯片连在一起。它们之间留有80um至150um的间隙,此间隙被称之为划片街区(Saw Street)。将每一个具有独立电气性能的芯片分离出来的过程叫做划片或切割(Dicing Saw)。目前,机械式金刚石切割是划片工艺的主流技术。在这种切割方式下,金刚石刀片(Diamond Blade)以每分钟3万转到4万转的高转速切割晶圆的街区部分,同时,承载着晶圆的工作台以一定的速度沿刀片与晶圆接触点的切线方向呈直线运动,切割晶圆产生的硅屑被去离子水(DI water)冲走。依能够切割晶圆的尺寸 ,目前半导体界主流的划片机分8英寸和12英寸划片机两种。

因为硅材料的脆性,机械切割方式会对晶圆的正面和背面产生机械应力,结果在芯片的边缘产生正面崩角(FSC- Front Side Chipping)及背面崩角(BSC – Back Side Chipping)。

正面崩角和背面崩角会降低芯片的机械强度,初始的芯片边缘裂隙在后续的封装工艺中或在产品的使用中会进一步扩散,从而可能引起芯片断裂,导致电性失效。另外,如果崩角进入了用于保护芯片内部电路、防止划片损伤的密封环(Seal Ring)内部时,芯片的电气性能和可靠性都会受到影响。

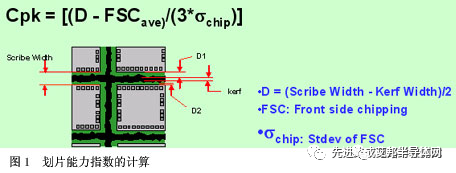

封装工艺设计规则限定崩角不能进入芯片边缘的密封圈。如果将崩角大小作为评核晶圆切割质量/能力的一个指标,则可用公式来计算晶圆切割能力指数(Cpk)(图1)。

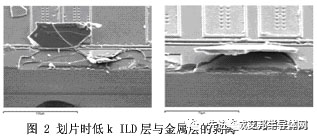

图1 D1、D2代表划片街区中保留完整的部分,FSC是指正面崩角的大小。依照封装工艺设计规则,D1、D2的最小值可以为0,允许崩角存在的区域宽度D为(街区宽度-刀痕宽度)/2, 为D1、D2的平均值, 为D1、D2的方差。依统计学原理,对于一个合格的划片工艺而言,其切割能力指数应大于1.5。 分层与剥离(Delamination & Peeling) 由于低k ILD层独特的材料特性,低k晶圆切割的失效模式除了崩角缺陷外,芯片边缘的金属层与ILD层的分层和剥离是另一个主要缺陷(图2)。

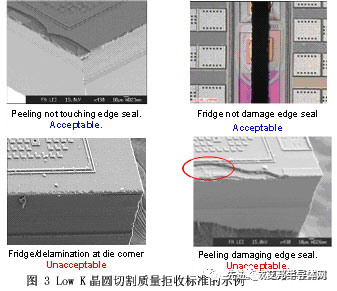

对于低k晶圆切割质量评估,除了正面崩角和背面崩角以外,根据实验数据和可靠性结果,规定了下述切割质量指标:

(1)铜密封环不允许出现断裂,分层或其他任何(在200倍显微镜下)可见的损伤。

(2)在划片街区上出现金属与ILD层的分层是允许的,只要这种分层能止步于铜密封环外。

(3)在芯片的顶角区域的金属/ILD层不允许出现分层或损伤,唯一的例外是有封装可靠性数据证明在某种特定的芯片设计/封装结构的组合下芯片的顶角区域的损伤可以接受。

划片工具和材料主要包括:划片刀(Dicing blade)、承载薄膜(Mounting tape), 划片参数主要包括:切割模式、切割参数(步进速度、刀片转速、切割深度等)。对于由不同的半导体工艺制作的晶圆需要进行划片工具的选择和参数的优化,以达到最佳的切割质量和最低的切割成本。

在晶圆的制造过程中,为了获得较高的成品率、较低的制造成本和稳定的工艺制程,每一步工艺都处于严格的监控下。因此,测试图案被设计出来并对其进行监测,以确保关键参数如电参数、制程精度如ILD层/金属层的淀积厚度、掩膜对准精度及金属线宽容差等满足设计要求。通常有3种方式来实现晶圆工艺制程监控:

( 1) 离线测试。 (2)测试芯片插入法。 (3)周边测试。

为了评核晶圆切割质量,在划片工序后用光学显微镜对晶圆进行检查是必不可少的。为获得对总体切割质量的了解,制定一个合理的抽样计划(包括取样位置和样本数)非常关键。传统的抽样计划中,被检查的芯片的选取是在靠近晶圆边缘的地方,在时钟指针1、3、5、6、7、9、11、12等8个方向上各拾取一个芯片进行芯片缺陷检查。这种检查方式对于成熟的非低k晶圆是合适的。然而,应用到低k晶圆时,它就不再能够提供一个关于切割质量的全面反映了。

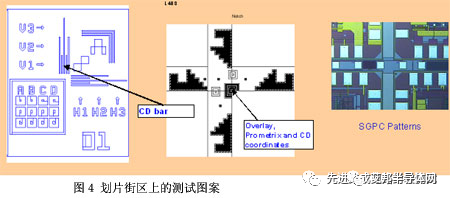

造成上述结果的主要原因是低k晶圆的切割缺陷较多,且不同于非低k晶圆切割的缺陷。应用传统的检查方法对于不同的晶圆,所得到的检查结果差别很大,而且不同的检查人员对同一片晶圆检查所得的结果也不相同。究其原因,一方面是因为不同的检查人员采用随机抽查的方法,很难获得对低k晶圆切割质量的全面评核,也很能难检测到最严重的情况。更主要的原因是因为该检查方法没有考虑到芯片上测试图案的结构和分布,而测

试图案的结构和分布是与晶圆的制造工艺、工艺控制方法密切相关的。

一个Reticle内能容纳的芯片的个数随着芯片尺寸及要求的光刻精度而不同。对于12英寸晶圆90nm技术、芯片尺寸为6x6mm2而言,一个Reticle可容纳20个芯片。这种测试方法比100%全检效率提高98%以上,而检查工作量只有全检的2%, 从而解决了划片检查的可操作性。

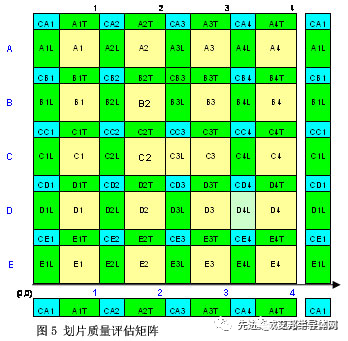

基于上述讨论,低k划片质量评估矩阵被设计出来(图5),它也可用于非低k晶圆的切割质量评估。

将一个Reticle从晶圆中取出,用英文字母A、B、C…来代表芯片在Reticle中所处的行号,而用数字1、2、3…代表芯片在Reticle中所处的列号,每一个芯片在一个Reticle中就可以被唯一地标示。如A1、B3等。在每一个芯片的四周有4条边和4个顶点,如果用A1T(A1 Top)代表A1芯片上方的街区,A1L(A1 Left) 代表A1芯片左边的街区,CA1(Corner A1)代表A1芯片左上方的街区交叉部分。这样,整个晶圆的切割质量就可以通过一个Reticle内XT、XL、CX(X代表芯片的坐标)的切割状况表达清楚。这个质量评估矩阵的另外一个优点是可以很方便地在晶圆上找到一个具有特定测试图案的芯片并观察其切割质量。也可离线对某个测试图案及其切割质量进行分析或改进。在此之前,需要经验和技巧来确定一个Reticle。

划片刀又称金刚石划片刀,包含三个主要元素:金刚石颗粒的大小、密度和粘结材料。金刚石颗粒在晶圆的切割过程中起着研磨剂的作用,通常是由CBN(Cubic Boron Nitride)合成而来。金刚石颗粒尺寸从2um到8um之间变化。为达到更好的切割质量,通常选用带棱角的金刚石颗粒。金刚石颗粒的密度代表着金刚石颗粒占金刚石刀片的体积比。通常划片刀片供应商都会提供不同的金刚石颗粒密度以适应不同的应用场合。金属镍被用作粘结剂,将金刚石颗粒粘结在一起。

划片刀的选择一般来说要兼顾切割质量、切割刀片寿命和生产成本。金刚石颗粒尺寸影响划片刀的寿命和切割质量。较大的金刚石颗粒度可以在相同的刀具转速下,磨去更多的硅材料,因而刀具的寿命可以得到延长。然而,它会降低切割质量(尤其是正面崩角和金属/ILD得分层)。所以,对金刚石颗粒大小的选择要兼顾切割质量和制造成本。

金刚石颗粒的密度对切割质量的控制也十分关键。对于相同的金刚石颗粒大小但具有不同密度的刀片,划片刀每一个旋转周期移去的硅材料是相同的,但是,平均到每一个金刚石颗粒移去的硅材料的量是不同的。

实验发现,高密度的金刚石颗粒可以延长划片刀的寿命,同时也可以减少晶圆背面崩角。而低密度的金刚石颗粒可以减少正面崩角。硬的粘结材料可以更好地“固定”金刚石颗粒,因而可以提高划片刀的寿命,而软的粘结材料能够加速金刚石颗粒的“自我锋利”(Self Sharpening)效应,令金刚石颗粒保持尖锐的棱角形状,因而可以减小晶圆的正面崩角或分层,但代价是划片刀寿命的缩短。刀锋的长度应根据晶圆的厚度,承载薄膜的厚度,最大允许的崩角的尺寸来进行定义,刀锋不能选得过长,因为长的刀锋会在切割时引起刀片的摆动,会导致较大的崩角。

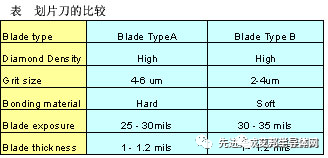

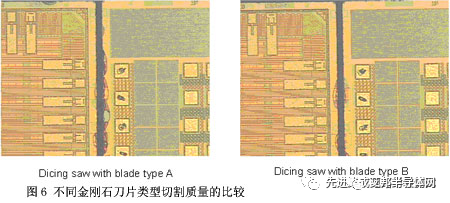

对于低k晶圆而言,金属层/ILD层的分层或剥离以及崩角相比生产成本更重要(在生产成本允许范围内)。基于实验,优选2-4um的金刚石颗粒、较低的金刚石密度和较软的粘结材料的划片刀作为进一步优化划片制程的基础。图6是不同类型的划片刀切割质量的比较。划片刀A具有较大的金刚石颗粒,较硬的粘结材料,而划片刀B具有较小的金刚石颗粒,较软的粘结材料(表),很明显,划片刀B的切割质量优于划片刀A。

承载薄膜(Mounting Tape)在开始划片前粘贴在晶圆的背面,用来在完成划片工艺后,将已相互分离的芯片仍然固定在薄膜上以便于自动粘片机(Die Bonder)完成粘片工序。薄膜的粘度对划片切割质量来说是一个重要特性。实验证明,较高的薄膜与硅片的粘结力可以有效地减低晶圆背面的崩角。

另一方面,在粘片工艺中,又希望薄膜与硅片之间的粘接力尽可能小,这样粘片工艺才可以获得一个稳健的工艺窗口,以避免顶起针(Ejector Pin)设置过高或拾片时间(Pick Up Time)设置过长造成潜在的芯片断裂及生产效率降低的问题。为了兼顾划片和粘片两个工序,紫外光敏薄膜(UV Tape)被选用作为晶圆的承载薄膜。UV薄膜的一个显著特点是它与硅片的粘接力在未经紫外光照射前非常高,可达16000mN/25mm,而在经过紫外光照射后粘结力显著下降,可至600mN/25mm。UV照射前后粘结力变化了25倍。UV薄膜的这种性质很好的兼容了划片和粘片对质量的控制。

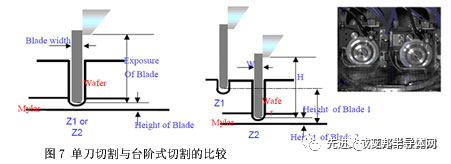

划片机一般提供两种切割模式,单刀切割(Single Cut)和台阶式切割(Step Cut),它们之间的区别如图7所示。实验证明,划片刀的设计不可能同时满足正面崩角、分层及背面崩角的质量控制的要求。这个结论对于晶圆厚度大于7 mil的低k晶圆尤为适用。为了减小正面金属层与ILD层的分层,薄划片刀会被优先采用,若晶圆较厚,则需选取刀锋较长的刀片。但须注意,具有较高刀锋/刀宽比的划片刀在切割时会产生摆动,反而会造成较大的正面分层及背面崩角。

台阶式切割使用两个划片刀,第一划片刀较厚,依程序切入晶圆内某一深度,第二划片刀较薄,它沿第一划片刀切割的中心位置切透整个晶圆并深入承载薄膜的1/3厚度。台阶式切割的优点在于:减小了划片刀在切割过程中对晶圆施加的压力;减少了必须使用较高的刀高/刀宽比的划片刀所带来的机械摆动和严重的崩角问题;提供了选择不同类型的划片刀的可能性来分别优化正面崩角/分层及背面崩角。

在划片机冷却水中添加某些化学添加剂,能够有效地降DI 水在晶圆/划片刀的表面张力,从而消除了晶圆切割产生的硅屑及金属颗粒在晶圆表面和划片刀表面的堆积, 清洁了芯片表面,并减少了芯片的背部崩角。这些硅屑和金属碎屑的堆积是造成芯片焊线区(Bonding Pad)的污染和晶圆背部崩角的一个主要原因。因此,当优化划片刀和划片参数无法消除芯片背部崩角时,可以考虑划片冷却水的添加剂。

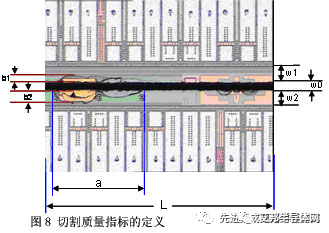

在确定了划片刀,承载薄膜及切割模式的设计与选择之后,下一步就是通过对划片工艺参数的优化来进一步减小,降低低k晶圆的划片缺陷。根据先前实验结果和对划片工艺参数的筛选,三个重要的工艺参数被选中进行工艺优化,包括划片刀转速、工作台步进速度和第一划片刀切割深度。低k切割工艺优化的难点之一是对于实验设计响应的确定上。曾经考虑过不同的指标,包括测量在垂直和平行于切割街区方向的金属/IL剥离的大小(a、b1、b2 见图8), 或测量剥离区域的长度占固定街区长度的百分比,但依照这些指标测量出来的数据在进行统计分析时发现即使对于同一组参数设定,也存在着较大的变异,因而不能用来进行低k切割工艺的优化。

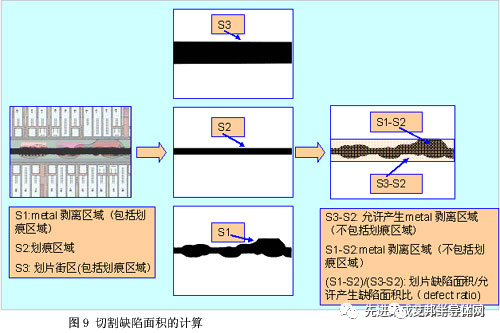

最后,通过比较发现计算存在切割缺陷的区域的面积(S1-S2)与固定区域的面积(S3-S2)的比值(S1-S2/S3-S2)能够较精确地反映不同的划片参数下的切割质量的差异。在图8中,允许划片产生缺陷的区域S是由W1、L 和W2、L所围成的图形,由于在划片后,街区中划片刀切过的部分由于承载薄膜的张力作用会产生变形,因此(w1+w0+w2)并不等于街区的宽度,所以W1、L 和W2、L 需要分别计算。而由b1、a 和b2、a所围成的划片缺陷区域(S1)不能够直接通过线性尺寸计算求得,通过利用Photoshop软件绘出降缺陷区域轮廓线,再利用像素填充、反显等方法将缺陷图形转换为二进制黑白图案,最后通过计算固定区域黑像素数量,来求得(S1-S2)/(S3-S2)百分比,从而得到实验设计的相应数据,缺陷区域的图形面积的确定方法如图9所示。

虽然经过工艺优化,金属层/ILD的分层与剥离被严格地控制在了铜密封环之外,然而分层/剥离现象并没有完全被消除。而且这种分层/剥离对其他半导体封装形式封装(如Flip Chip)的可靠性的影响仍需要相关的可靠性数据来验证。因此有必要继续研究彻底消除金属/ILD分层/剥离的解决方案。

首先,芯片设计/制造厂与封装厂的合作是必需的。实验发现,一些严重的金属ILD分层/剥离总是发生在几个包含特定的测试图案的街区上。而在一些不包含测试图案的街区,分层与剥离的缺陷几乎为0。这里得出一个启示,芯片厂可以对测试图案进行修改,使它可以抵抗在划片工艺中出现的分层/剥离。 例如,通过在划片街区的测试图案中增加了虚拟“L”形图案,严重的金属/ILD层的分层与剥离几乎被消除。

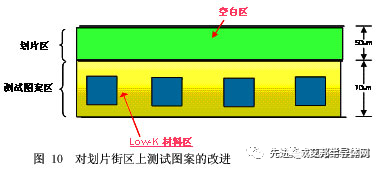

另外,在有限的街区宽度内(比如120um),如果能将测试图案限制在70um之内,并将其偏置于街区的一侧,那么,在街区的另一侧,就形成了一个宽为50um的“空白”区域。如果将这个50um宽的区域作为假想街区,则低k晶圆的划片就演变为一个窄街区(50um)非低k晶圆的划片问题(图10)。以目前划片机和划片工艺能力来说,这种切割方式是可行的。

另外, 对于芯片厂的工艺过程检测而言,并不是所有的测试图案都是必需的。测试图案以模块化(Mask Set)的形式存在。有时,某一种集成电路制造工艺的生产检测需要来自几个模块中的某些测试图案,光刻工程师在选取了所需测试图案所在的模块后,往往不会删除掉无用的测试图案。而这样做的后果是增大了低k晶圆划片工艺的复杂度,减小了划片工艺窗口。它表明,要保证低k半导体产品的经济规模生产及其可靠性,要求业界将前工序和后工序作为一个整体来考虑、优化,才会尽可能地避免“瓶颈”工序的出现。

业界目前也在试图寻找低k晶圆机械式划片的替代方法,激光切割就是其中的一种。严格地说,激光束不是“切割”低k层,而是依靠激光能量产生的高温融化金属层/ILD层。这样的激光切割对金属/ILD层产生的机械应力很小,因而不会产生金属/ILD层分层或剥离的问题,因为机械式划片机不再切割低k层。目前,激光划片机已开始应用在65纳米及以下的低k晶圆的划片制程中。然而,昂贵的设备成本仍然是制约激光划片机普及的一个主要原因。

本文简述了划片机的工作原理、划片工艺的主要缺陷以及传统的划片质量评估方法,在此基础上,提出了一种新的评估方法——晶圆切割质量评估矩阵,它能够全面、客观地分析和评核切割质量。本章还定义了评核切割质量的主要特性指标,对影响低k晶圆切割质量的主要因素展开讨论和优化设计,运用了实验设计方法对低k晶圆划片的工艺参数进行了工艺优化。同时,对与芯片厂进行合作进一步改进低k晶圆的切割质量进行了尝试和努力,提出了可行性方案。最后,对新型的非机械式划片机-激光划片机作了简要介绍。

来源:先进集成电路封装测试

作者:王志杰

原文始发于微信公众号(艾邦半导体网):封装工艺——晶圆划片工艺及优化

先进封装设备类似前道晶圆制造设备,供应商受益先进封测产业增长。随着先进封装的发展,Bumping(凸块)、Flip(倒装) 、TSV 和 RDL(重布线)等新的连接形式所需要用到的设备也越先进。以长球凸点为例,主要的工艺流程为预清洗、UBM、淀积、光刻、焊料 电镀、去胶、刻蚀、清洗、检测等,因此所需要的设备包括清洗机、PVD 设备、光刻机、 刻蚀机、电镀设备、清洗机等,材料需要包括光刻胶、显影剂、刻蚀液、清洗液等。为促进行业发展,互通有无,欢迎芯片设计、晶圆制造、装备、材料等产业链上下游加入艾邦半导体先进封装产业链交流群。

文章导航