光电共封装就是把交换芯片和光引擎(光模块)封装在一起。光引擎或光模块的主要功能是指输入的光纤信号转换为数字信号,同时将ASIC(专用集成电路)芯片输入的数字信号转化为光信号进行输出。光电共封的方式缩短了交换芯片和光引擎间的距离,使得电信号能够更快的在芯片和光模块之间传输,提高了效率,减少了尺寸,还降低了功耗,所以CPO的高效率、低功耗有可能会成为后续AI高算力下最好的解决方案,也是目前最有希望解决ChatGPT算力需求的一个方向。

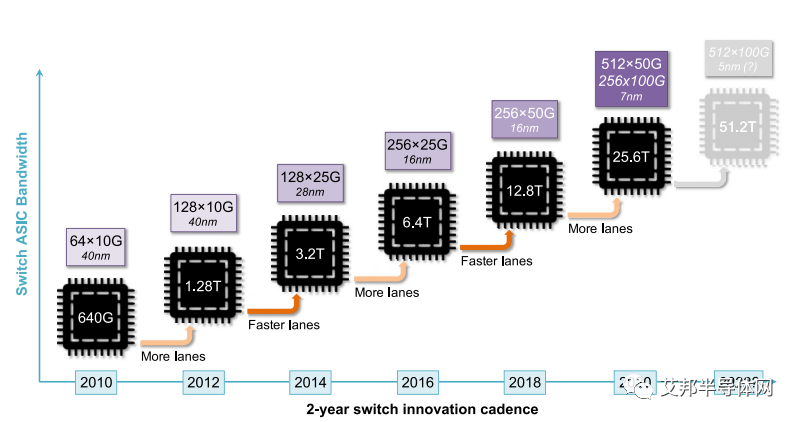

2019年微软和facebook就联合开发CPO技术,驱动CPO技术的主要原因就是数据中心架构正在快速增长,交换机设计也在不断发展,以支持更大的网络需求。将光纤与ASIC(专用集成电路)通过CPO技术连接可以缩短互连的长度,从而降低开关光电气I/O的功耗。主要技术包括电信号接口、光标准、光模块管理接口、可靠性要求等。如图1所示,大家的目标都是在短期内可以实现51.2Tbps的目标即每秒传输速度可达51.2T。

图1 交换机ASIC带宽演变

图1 交换机ASIC带宽演变

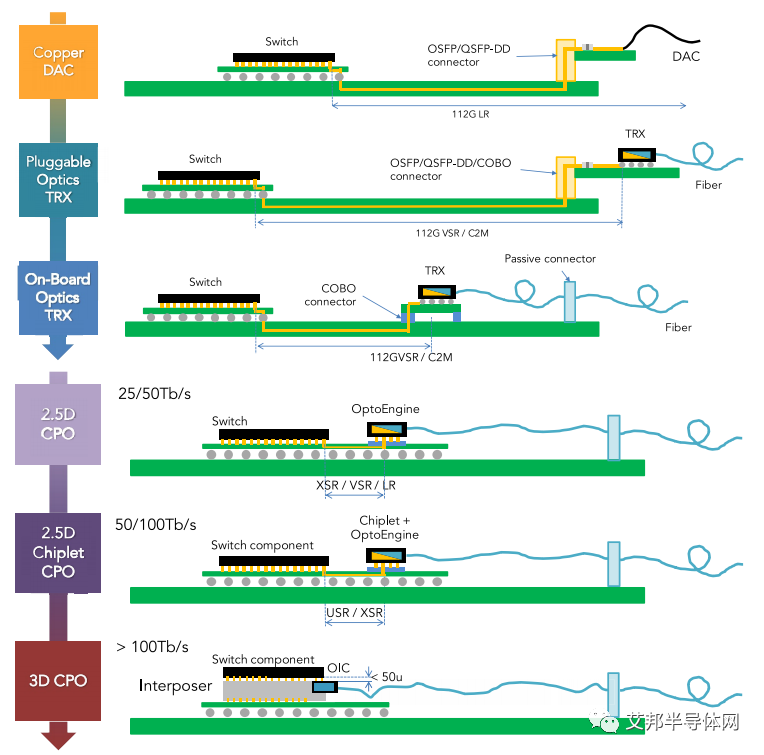

光电共封装的演进形式如图2所示。从最开始的将ASIC与铜缆通过主板连接(Copper DAC),然后引入光模块但是仍然插拔方式通过接口与主板再与ASIC相连(Pluggable Optics TRX),再到通过主板将将光电转换功能从面板搬到主板处理器或者关联电芯片之旁。这样因为节省空间而提高了密度,也减少高频信号的走线距离,从而降低功耗。再到载光学连接组件(On-Board Optics TRX)则是引入无源接头并不再采用可插拔式接头,进一步缩短连接长度。接着演进到2.5D CPO直接将光驱动与Switch ASIC封装在同一个基板上,进一步缩短线距,增加I/O 密度。最后通过3D封装的技术直接光学IC直接连接到中介层上,实现小于50um pitch的I/O间距的相连。

图2 光电共封装的封装形式及发展趋势

图2 光电共封装的封装形式及发展趋势

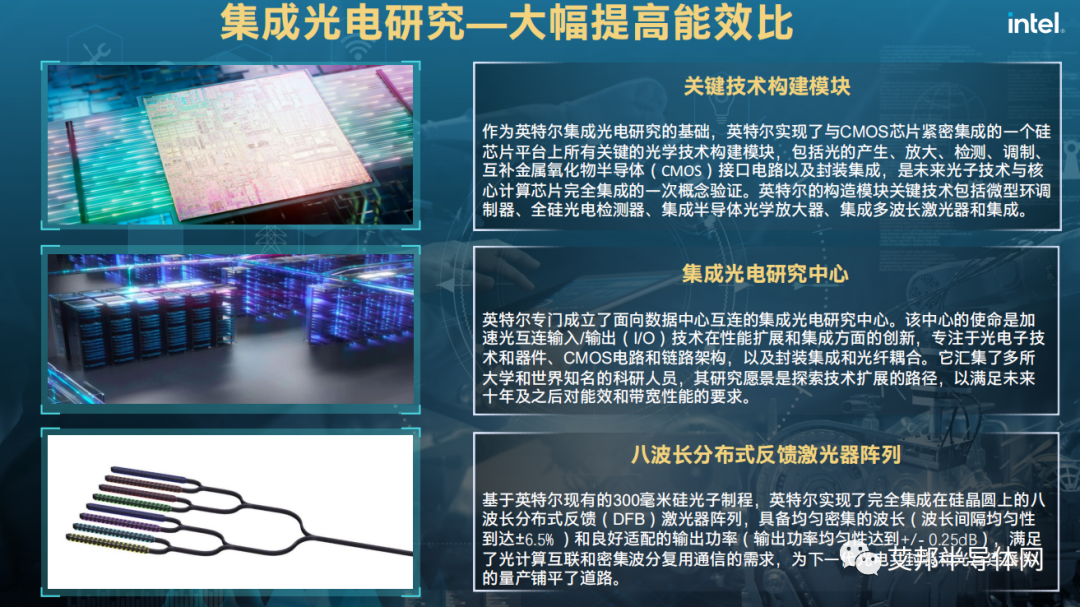

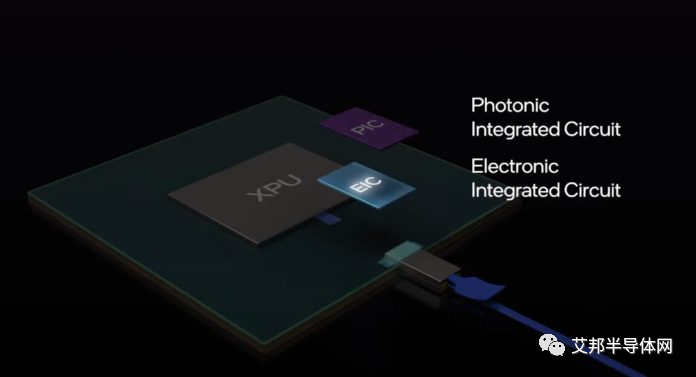

在国际上,2022年英特尔在集成光电方面的一些突破性进展。英特尔在一个平台上实现所有关键模块的集成,光电发射、放大、检测、调制都可以一个大芯片模块中利用CMOS工艺制造,整体尺寸和功耗降低非常多。同时,还涉及到一些基础的器件级的创新,英特尔研制了一个在硅基晶圆上8个波长的激光器阵列,这是光的产生部件,它会对光电封装的准确性和能效提升上有很大帮助,并为光电共封装和光互连器件的量产铺平道路。

图3 Intel光电研究进展

图3 Intel光电研究进展

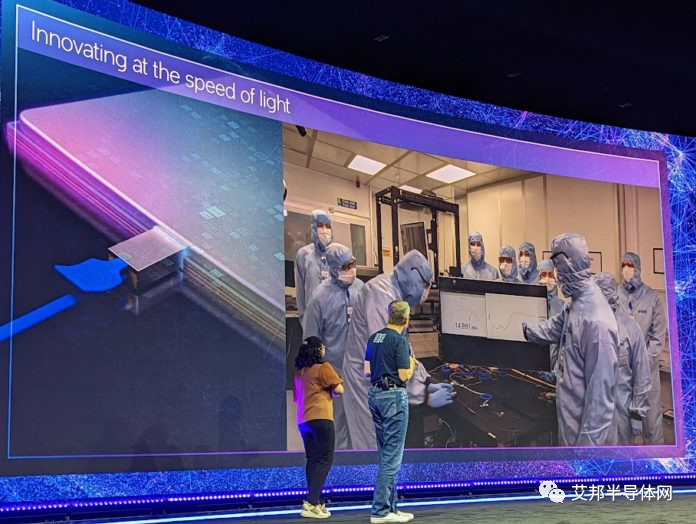

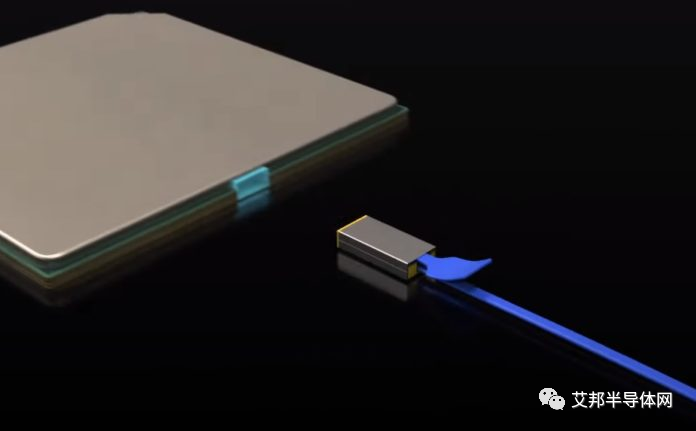

如图4进一步所示,在展示现场与苏格兰Intel实验室的连线。Intel在这个工作中首次解决了硅光芯片与光纤连接的问题。现有的方案是使用短光纤(尾纤)从芯片直接连到第二个连接器。Intel的新型连接器直面CPO应用的耦合难题,采用可插拔的方式,类似AOC线缆或者MTP连接器,可以将光纤直接连接到CPO封装上,如图5,6所示从Intel的展示视频看,这很可能是一种多连接器的连接方案。

图4 Intel CPO技术展示现场

图4 Intel CPO技术展示现场

图5 Intel CPO技术展示,将光纤直接与芯片相连

图5 Intel CPO技术展示,将光纤直接与芯片相连

图6 Intel CPO技术展示,将光纤直接与芯片相连

图6 Intel CPO技术展示,将光纤直接与芯片相连

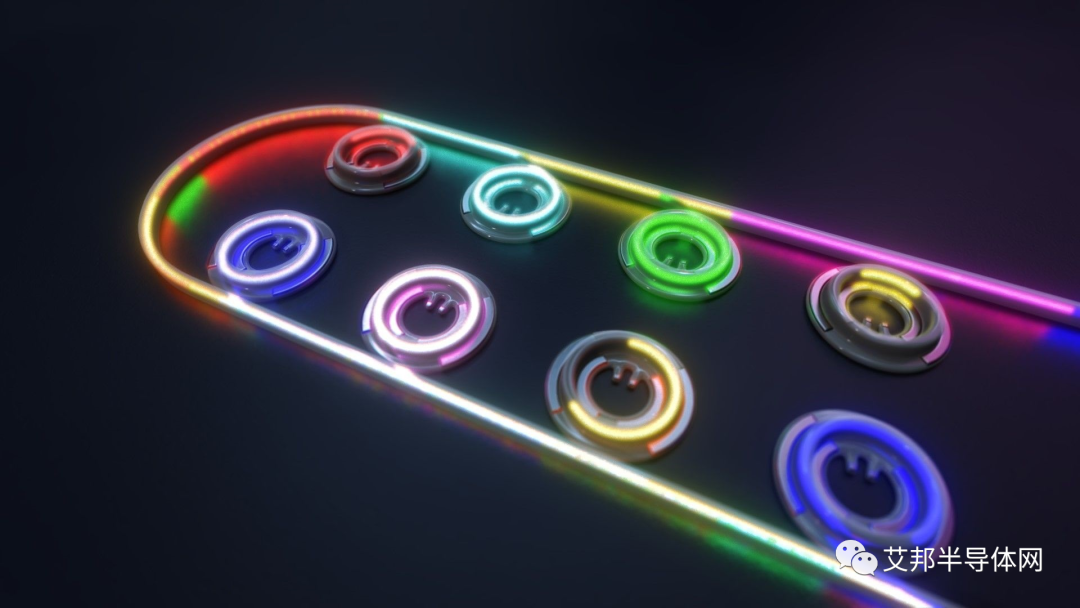

图3中最后一项八波长分布式反馈激光器阵列可能引起了大家的注意,这里顺便提一下。Intel的集成于硅晶片上的八波长分布式反馈(DFB)激光阵列,拥有高出行业标准的±0.25 dB的输出功率均匀性和±6.5%的波长间隔均匀性,在多波长集成光学领域处于业界领先。该技术确保了光源的一致波长分离,均匀的输出功率可以满足光计算互连以及密集波分复用(DWDM)的通信要求。与此同时,结合DWDM技术,既增加了带宽,又缩小了光子芯片的物理尺寸。特别要指出的是八波长DFB激光器阵列是使用英特尔商用300 mm混合硅光子平台设计和制造的,这与在3英寸或4英寸III-V族晶圆厂制造的传统半导体激光器相比,这项技术提高了波长均匀性,具有大批量制造和广泛部署的潜力。

图7 八波长分布式反馈激光器阵列接口

图7 八波长分布式反馈激光器阵列接口

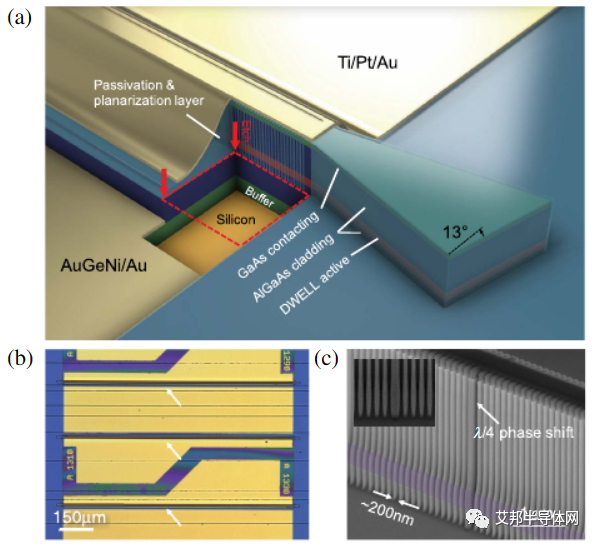

图8,中山大学硅基DFB激光器示意图(a) 激光器剖面图,展示了外延层结构、光波导结构和输出耦合器;(b) 激光器阵列光学显微镜照片;(c)侧壁布拉格光栅的电子显微镜照片,展示了超高宽深比的一阶光栅

图8,中山大学硅基DFB激光器示意图(a) 激光器剖面图,展示了外延层结构、光波导结构和输出耦合器;(b) 激光器阵列光学显微镜照片;(c)侧壁布拉格光栅的电子显微镜照片,展示了超高宽深比的一阶光栅

我国中山大学光电材料与技术国家重点实验室在该领域有专项研究,在2022年该实验室的论文里指出其可以将波长段数扩展到16段波长。该实验室于2018年推出世界首例硅基DFB激光器阵列,如图8所示。当然实验室产品离量产还是有一定的差距,希望我国的光电共封技术早日量产。如果您是该领域的专家,欢迎入群交流。

原文始发于微信公众号(艾邦半导体网):先进封装之被ChatGPT带火的光电共封装技术CPO