正如大家所知, AMD一直在思考下一代技术,让我们来看看AMD的一些先进技术,这是保证AMD产品能够领先的重要基础,即将最好的晶圆工艺与最好的封装工艺结合在一起。AMD是行业最早采用台积电7nm 制造技术的公司,到目前为止,我们已经将30 多种 7nm 产品交付市场。在我们的路线图中,5nm 技术如期进行,AMD将于明年推出首款5nm产品Zen 4。

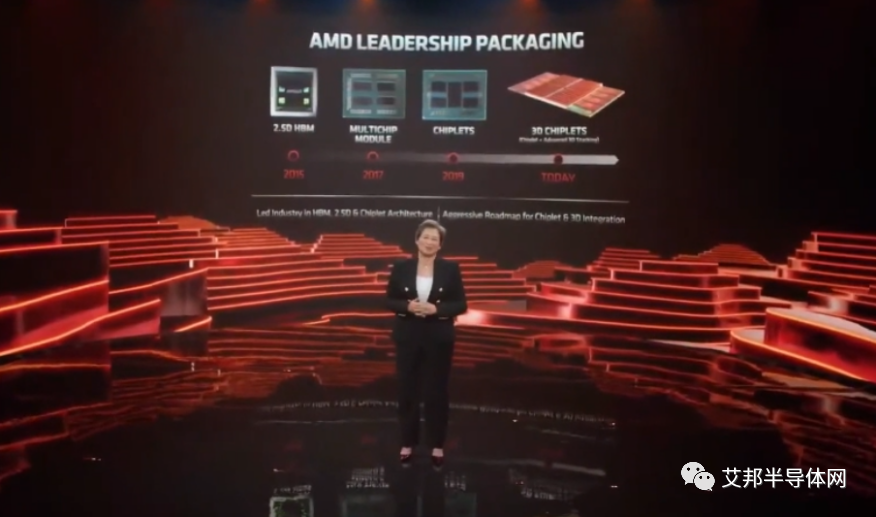

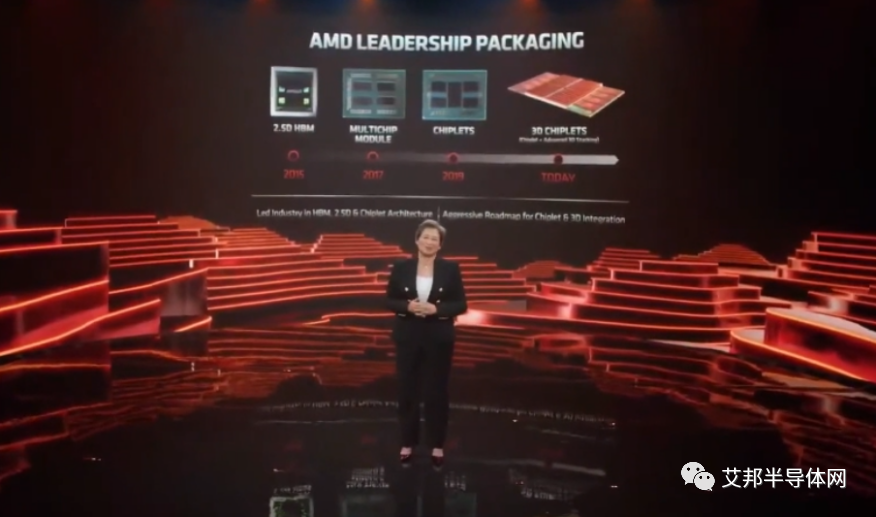

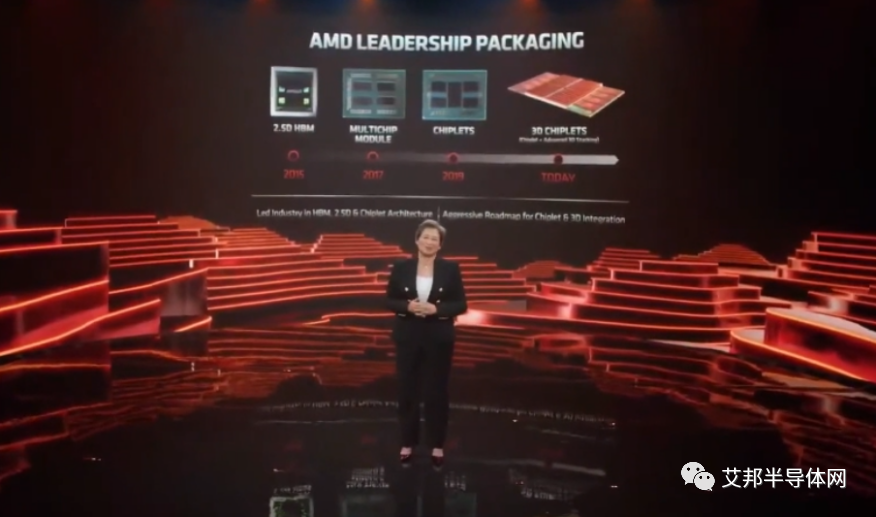

AMD也是先进封装技术的领导者,我们在封装领域的创新和投资已历时多年。2015年,AMD 向 GPU 市场推出了高带宽内存(HBM)和硅中介层(Si Interposer)技术的产品,使得我们在小尺寸内存带宽方面处于行业领先地位。之后我们在2017年推出了大容量多芯片模块封装,将数据中心和PC市场的计算性能推入了新赛道。在2019年,我们推出了Chiplet封装,将不同工艺节点的CPU内核且I/O规格不同的芯片封装在一起,显著提高了能效和功能。

今天我想向大家再展示一项新技术。在过去的几年里,我们与台积电针对3D封装技术进行了密切合作,这个技术可以将芯片垂直堆叠封装形成3D架构,从而制备高性能计算产品。

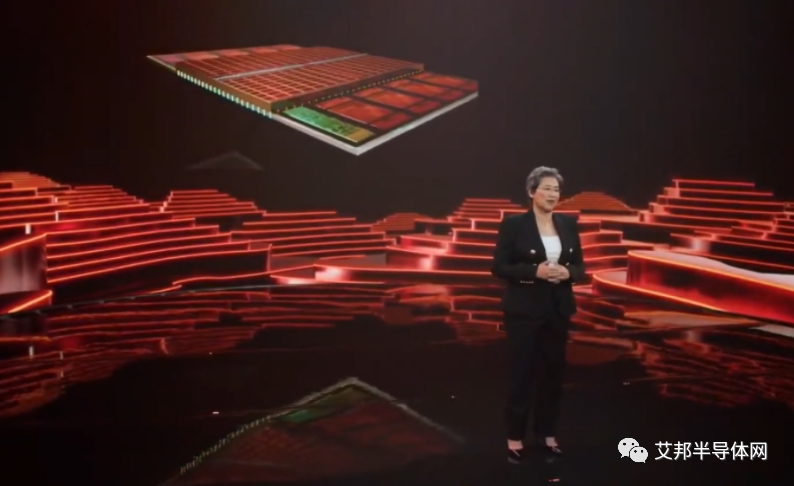

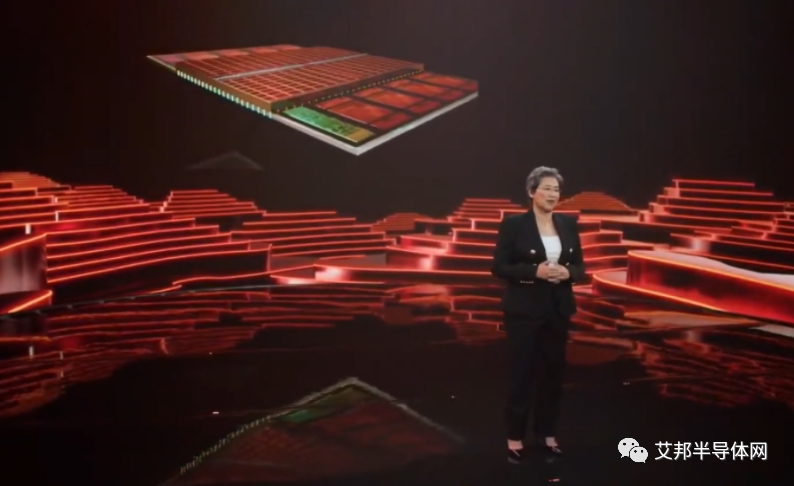

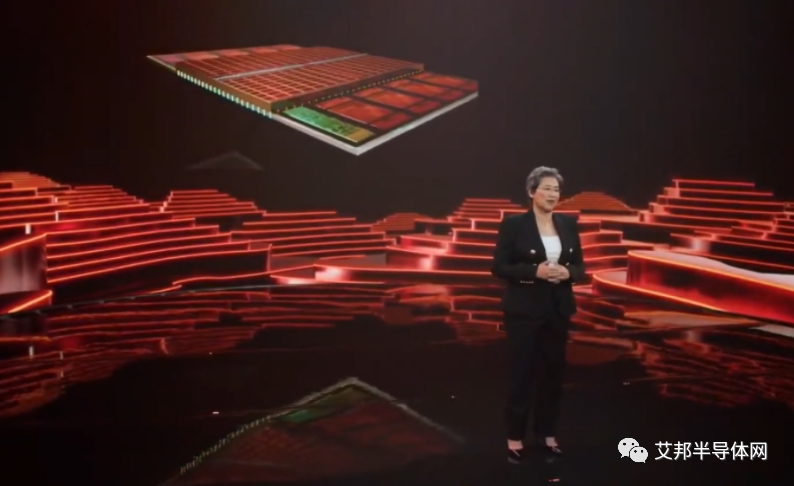

现在让我向您展示一下我们的3D芯片堆叠技术的工作原理。这项技术的第一个应用是制备3D垂直缓存 (3D V-Cache)。在展示原型中,我们采用AMD领先的Ryzen 5000系列处理器,在其每个CPU内核的顶部直接堆叠64MB 7nm SRAM,成功地将高速L3缓存的容量增加了两倍,有效地为我们的Zen 3处理器内核提供动力。通过硅通孔 (TSV)技术,3D 缓存直接贴装到Zen 3的CCD上面,信号和电源在堆栈芯片之间直接传递,实现了超过2 TB/秒的带宽。

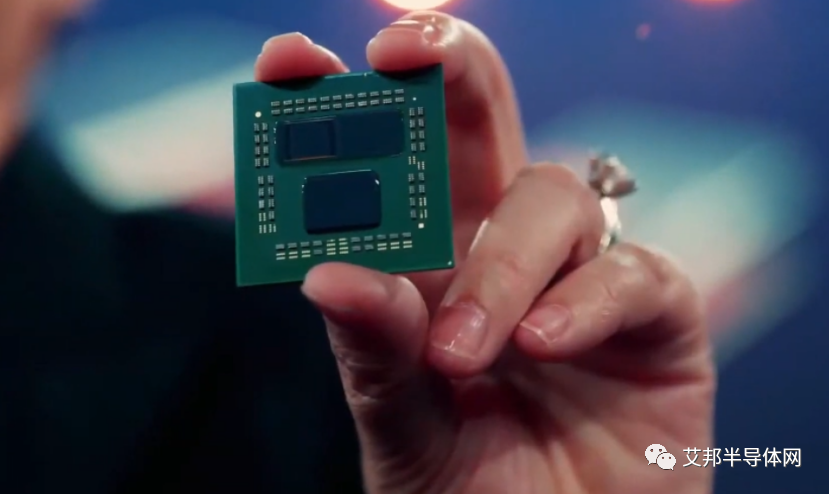

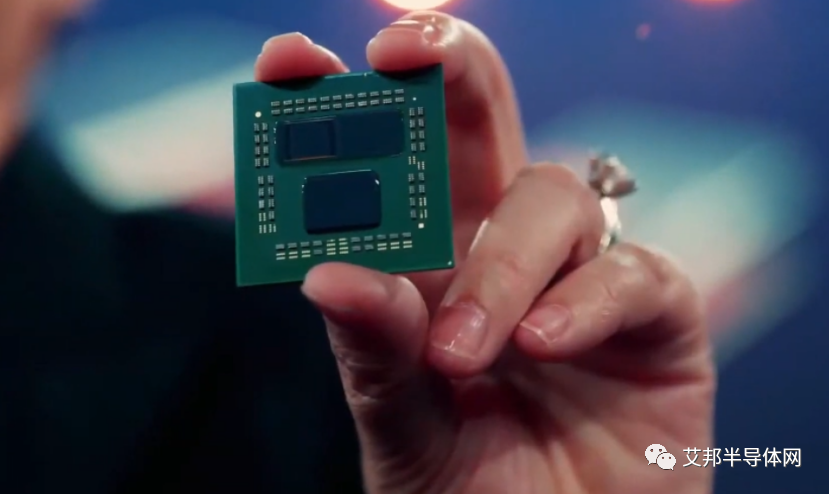

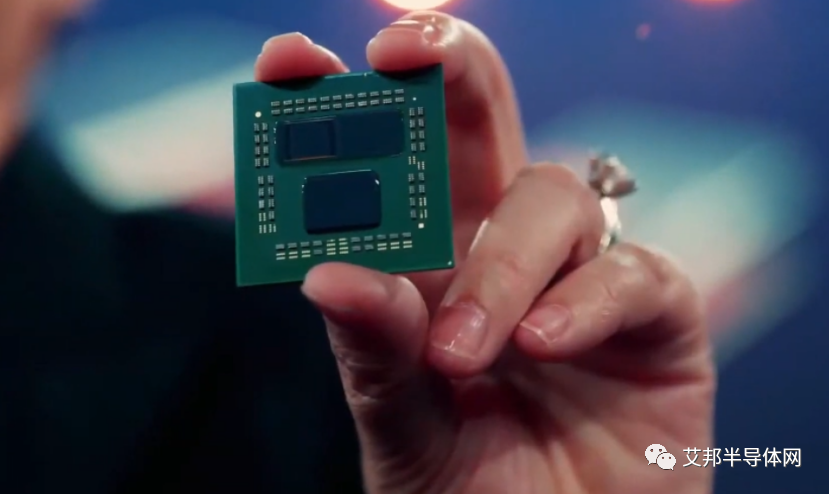

在制造环节,我们3D缓存芯片打薄并添加了结构硅层,为芯片组合体预制了无缝贴装表面。最终的CPU成品,即3D堆栈,看起来正如这个 Ryzen 5000处理器。接下来让我详细讲解。

这款原型是采用 3D Chiplet技术的Ryzen 5900x处理器。当然,我们已经取下了散热盖,方便大家观察内部的CCD (Core Chiplet Die),在此您可以看到6mm x 6mm 的方形 SRAM混合贴装在CCD之上。在实际的设备中,每个CCD都会贴装单独的SRAM,从而每个CCD将拥有96MB的缓存,换句话说12或16核的Ryzen处理器总共会有192MB缓存。

现在让我分享该技术更多的细节。我们使用硅通孔 (TSV) 技术的混合键合法,使其焊点互连密度达到 2D Chiplet封装技术的200多倍,是其他3D堆叠封装技术的15倍以上。这让封装集成更加高效,更密集。芯片间焊点互联使用铜-铜直接键合,不再使用任何类型的锡球焊接凸块。这种方法极大地提高了散热和晶体管密度,缩短互连间距,使得单个信号能耗仅为微凸块互联法的1/3。这些特性使其成为世界上最先进、最灵活的有源硅堆叠技术。

现在再让我们看看它的实际表现。大缓存对许多重工作负载的计算非常重要,其中PC游戏场景中的工作负载则为我们众所周知。让我们看一下Gears 5的性能演示。左侧是Ryzen 9 5900x,这是当今最快的游戏CPU。右侧是基于3D Chiplet技术的5900x原型芯片,其采用了3D V-Cache新技术。两个CPU具有相同的核心数和线程数,并将时钟频率固定在4G Hz。

坦白讲,这两款处理器的游戏性能都非常好,但3D Chiplet的原型芯片将性能平均提高了 12%。这非常惊人,也表明3D Chiplet对实际工作负载的提升有实质性的贡献。

事实上,当您研究当今的众多游戏时,会发现它们对PC内存系统有着强烈的需求。当内存越靠近处理器时,PC会变得更快。如果将这些热门游戏运行在采用V-Cache技术的PC上时,我们会发现在1080p分辨率模式下,游戏的平均性能提升了15%。想象一下,这15%的游戏性能的增加仅来自3D V-Cache技术,却相当于整个一代架构带来的提升。今天很高兴能向大家展示我们的3D Chiplet技术。事实上,我们在这项技术的开发上取得了长足进展,并计划在年底前开始生产拥有3D Chiplet技术的高规格产品。

原文始发于微信公众号(艾邦半导体网):AMD 揭秘 3D Chiplet 技术