近日,南方科技大学工学院国家示范性微电子学院潘权团队在高性能通信芯片设计领域取得重要进展,研究成果包括一款5G通信低功耗超宽带通信芯片,一款高速有线通信低功耗注入锁定时钟信号恢复电路芯片和一款高速光通信芯片。相关论文成果分别发表于IEEE Solid-State Circuits Society的顶级期刊IEEE Journal of Solid-State Circuits (JSSC),IEEE Circuits and Systems Society 的顶级期刊IEEE Transactions on Circuits and Systems (TCAS-I),和国内高水平期刊 Journal of Semiconductors (JOS)的2022年第一期的封面文章。JSSC和TCAS-I为芯片领域代表最高国际学术水平的顶级学术期刊。

5G通信低功耗超宽带通信芯片

近年来,由于5G 商用化的步伐加快和对毫米波技术的进一步研究,移动通信正迎来一个全新的时代。目前,世界各国对于5G通信频段的划分各不相同,除了已经获得授权的频段之外,还有一些未授权的频段亟需开发。对于5G毫米波通信系统来说,超宽带和低功耗一直都是重要指标。为了构建一个适用于5G应用的超宽带毫米波收发器,频率综合器(PLL)是最重要的模块,而注入锁定分频器(ILFD)就是毫米波PLL中亟待攻破的卡脖子部分。目前世界上已发表的毫米波ILFD都不能同时覆盖所有5G授权和未授权的频段。因此,一个可以同时支持全球所有频段的超宽带注入锁定分频器至关重要。潘权课题组发表以"Analysis and Design of Tuning-Less mm-Wave Injection-Locked Frequency Dividers with Wide Locking Range Using 8th-Order Transformer-Based Resonator in 40 nm CMOS"[1]为题的论文实现了世界上最宽的锁定范围和最高的能效比,可以覆盖全球所有5G毫米波频段,整体性能达到世界领先水平,为毫米波领域注入锁定分频器设计提供了一个可行方案,对5G通信的高频段多频带应用有着实际意义。

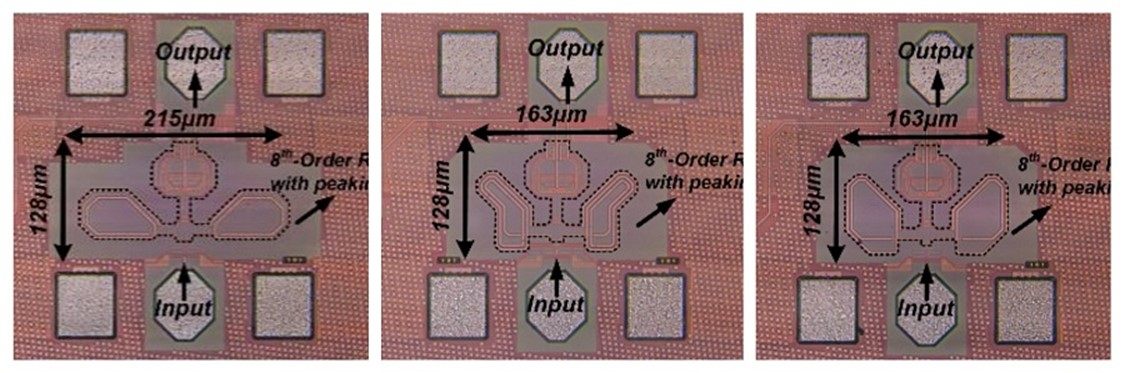

值得一提的是,在不影响电路性能的前提下,团队特意把芯片版图设计成三朵花的形状,期望南科大未来在芯片领域有更多独立自主的高质量科研成果。

论文[1]中三款芯片的显微图

南科大微电子学院科研助理姜棋耀为本论文第一作者,潘权教授为唯一通讯作者,南科大为论文唯一单位。本工作得到了国家自然科学基金、广东省自然科学基金和深圳市发展改革委员会项目的支持。

[1] Q. Jiang, Q. Pan*, "Analysis and Design of Tuning-less mm-Wave Injection-Locked Frequency Dividers with Wide Locking Range Using 8th-Order Transformer-Based Resonator in 40 nm CMOS," IEEE Journal of Solid-State Circuits (JSSC), Mar. 2022.

论文链接:https://ieeexplore.ieee.org/document/9728743

时钟数据恢复芯片

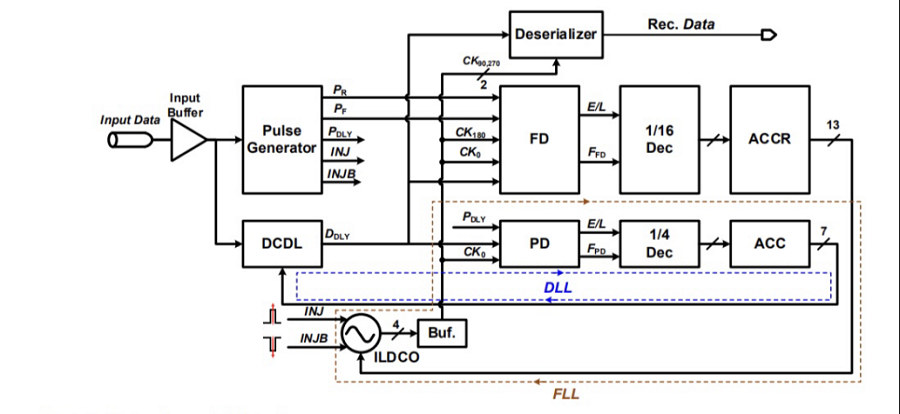

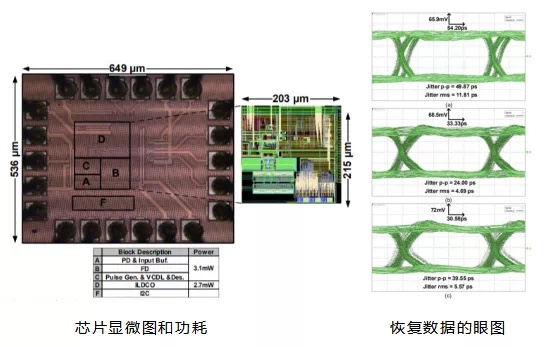

在高速芯片技术飞速发展的当下,时钟数据恢复技术作为通信系统的基础模块,保障了实际可用的可靠带宽,在工业生产中举足轻重。潘权课题组硕士研究生肖文博、博士后黄奇伟、Hamed Mosalam等采用40nm CMOS工艺,成功设计并验证了一款低功耗注入锁定型数据时钟恢复电路(ILCDR)。该成果以"A 6.15-10.9 Gb/s 0.58pJ /bit Reference-Less Half-Rate Clock and Data Recovery with 'Phase Reset' Scheme"[2]为题发表。该论文提出一种高效的"Phase Reset"(相位复位)方法以周期性对齐时钟和数据上升沿的相位。其中,频率误差可通过比较数据上升沿和对齐后的时钟来提取。同时,使用低功耗两级注入锁定型环形数控振荡器在提供四相交轴时钟的同时显著地减少了功耗。基于这种架构搭建的CDR在提供0.9V电压的条件下功耗仅为5.8mW,经测量高频抖动容限(JTOL)为0.15UIpp。并且,提出的CDR在能量效率上实现重大提升,能效比为0.58pJ/bit,达到国际同类型电路最佳水平。

论文[2]中新型超低功耗CDR系统架构图

南科大微电子学院硕士研究生肖文博和博士后黄奇伟为本论文共同第一作者,潘权教授为唯一通讯作者,南科大为论文唯一单位。本工作得到了国家自然科学基金、广东省自然科学基金和深圳市发展改革委员会项目的支持。

[2]W. Xiao, Q. Huang, H. Mosalam, C. Zhan, Z. Li, and Q. Pan*,"A 6.15-10.9 Gb/s 0.58 pJ/bit Reference-Less Half-Rate Clock and Data Recovery with 'Phase Reset' Scheme," IEEE Transactions on Circuits and Systems I, Reg. Papers, Feb. 2022.

论文链接:https://ieeexplore.ieee.org/document/9585315

高速光通信

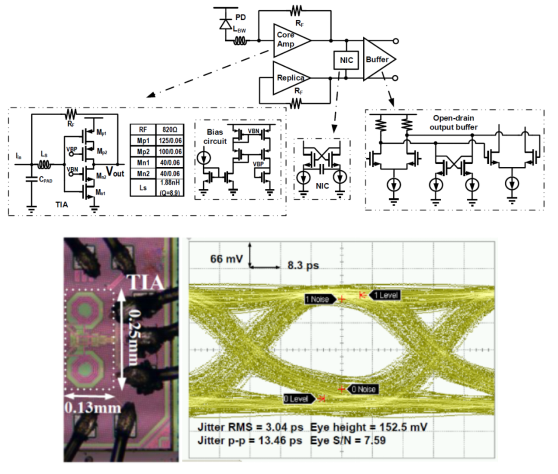

随着云计算设备和多媒体设备数目的飞速增长,人们对传输速率的要求越来越高,相较于传统的铜互连电路,高速光通信电路凭借其稳定、高能效和极低的信道损耗等优点被广泛用于各大数据中心,跨阻放大器(Transimpedance Amplifier,TIA)是高速光通信电路的核心模块。在传统TIA中,光电二极管较大的寄生电容会显著影响带宽,而如若通过牺牲增益来换取带宽会带来较大输入噪声,严重影响信号传输质量。同时,传统TIA架构会消耗较大的功耗,这无疑给高速光通信电路的设计带来了更大的挑战。潘权课题组发表的以"A 58-dBΩ 20-Gb/s inverter-based cascode transimpedance amplifier for optical communications"[3]为题的论文中提出了基于反相器的Cascode架构TIA,利用Cascode结构的高增益来降低输入阻抗和等效噪声电流,进而提升TIA的带宽和灵敏度。此外,电路还采用了串联电感峰化和负电容补偿等多种手段用于提高电路带宽,大大提升了电路的传输速率。[3]中电路采用TSMC 65nm工艺,在58 dBΩ的增益下,数据传输速率达到20Gb/s,而功耗仅为4 mW,FoM高达454。

TIA电路结构图以及芯片照片及其测试结果

[3] Q. Pan*, X. Luo, "A 58-dBΩ 20-Gb/s inverter-based cascode transimpedance amplifier for optical communications," Journal of Semiconductors (JoS), Jan. 2022.

论文链接:http://www.jos.ac.cn/article/doi/10.1088/1674-4926/43/1/012401

文章来源:南科大深港微电子学院,原文链接:https://sme.sustech.edu.cn/index/news/neiye/id/520.html

一颗芯片的制造工艺非常复杂,需经过几千道工序,加工的每个阶段都面临难点。欢迎加入艾邦半导体产业微信群:

长按识别二维码关注公众号,点击下方菜单栏左侧“微信群”,申请加入群聊