WLCSP(Wafer-Level Chip-Scale Package)是一种将晶圆级封装(WLP)和芯片尺寸封装(CSP)合为一体的封装技术。芯片尺寸封装(CSP)是指整个package的面积相比于silicon总面积不超过120%的封装技术。该技术有效促进集成电路的小型化,但是其不适合服务器级处理器的应用。晶圆级封装(WLP)是指在晶圆前道工序完成后,直接对晶圆进行封装,再切割分离成单一芯片,相对于传统封装将晶圆切割成单个芯片后再进行封装,WLP 技术在封装成本和生产效率等方面具有明显的优势。目前大部分先进封装,比如英特尔的Foveros系列,台积电的SOIC, InFO等等都是基于晶圆级的。WLCSP则是巧妙地结合上述两种封装方式的优点。相比于传统的引线键合,WLCSP最大特点就是封装体积小,互联路径短。WLCSP的应用非常广泛,相比于引线键合工艺能够更好地满足便携式电子设备、智能手机、平板电脑、可穿戴设备等小型高集成度产品的需求。但是WLCSP也是有其局限性的,因其可用于bump的面积受silicon面积限制,所以总共的IO(input/output)数量有限,通常其IO密度也相对较低。

Flip Chip Technologies(于2014年被天水华天收购)在1998年公布了其UltraCSP的专利技术。他们提出使用再分布层 (RDL) 将芯片的外围焊盘向芯片内部扇入并通过焊球(或凸块)连接到印刷电路板(PCB)或封装基板。自2001年开始,Amkor等其他OSATs和晶圆代工厂得申请得到了Flip Chip Technologies的许可来使用UltraCSP技术,自此WLCSP逐步被大规模应用。值得一提的是,这一专利已经过了20年的有效期了。成立于2003年的天水华天科技在2014年末以约2.58亿元收购了Flip Chip Technologies的100%股权。通过本次收购,华天科技进一步提高了在晶圆级封装及flip chip封装上的技术水平。算得上是一次相当成功的收购。图一显示了天水华天在Phoenix的分部 Flip Chip International。

值得一提的是大陆封测三巨头,长电,通富和华天的发家史都曾成功收购境外先进封测厂。长电科技公司于2003年上市是中国半导体业第一家上市公司。长电科技作为大陆封测龙头,取得如今的地位是跟2015年以“蛇吞象”方式收购星科金朋是分不开的。2015年长电科技以7.8亿美元的价格收购了当时全球排名第四位的新加坡厂商星科金朋 Statschippac,使其一下子跻身全球封测行业第一梯队。2007年上市的通富微电在2015年收购了AMD在苏州及马来西亚槟城的两家专门从事封测业务的子公司各85%的股权。通过此次收购,通富微电得到了AMD的芯片封装和测试业务,进而巩固了其在国内的领先地位并进一步提升了公司的行业影响力和海外知名度。这里提到的重大收购案都是在中美科技站开打之前,放如今都是很难完成的交易。

图一:天水华天在Phoenix的分部 Flip Chip International

WLCSP可以从有无重布线层来分成两种结构类型:直接凸块BOP (bump on pad)和重布层RDL(Redistribution Layer)。直接凸块WLCSP包含一个可选的介电层(常见的有聚酰亚胺,苯并环丁烯 和聚苯并双恶唑等),这个层用作有源裸片表面上的应力缓冲器。该介电层覆盖了除连接焊盘开窗区域(pad opening)之外的整个裸片面积。在这些开窗区域之上溅射或电镀凸块下金属层(UBM)。UBM是不同金属层的堆叠,包括抗扩散层、润湿层和抗氧化层。然后通过植球回流焊方式来形成焊球或者铜柱加锡膏凸块。与直接凸块WLCSP不同的是,重布层WLCSP使用两层或者更多的介电层。第一层介电层和BOP工艺一样附在裸片上。然后通过光刻显影薄膜沉积电镀等工艺在介电层上形成金属层。金属层通过垂直通孔和芯片的pads相连。如果集成度比较高的话,可能需要更多层的重布线。接下去需要在金属层上再敷上一层介电层,然后在介电层打孔形成vias。然后类似于第一层金属层的流程来完成制造第二层金属层。同样的方法,还可以继续用类似的工艺增加更多的重布线层。目前重布线层一般不超过4层。最后在表面涂布表面介电层,然后通过植球形成C4或者带铜柱的C2 bumps。

由于BOP WLCSP工艺流程可以被包含到RDL WLCSP中,接下来我们来大体地讲讲RDL WLCSP的制造工艺流程步骤。如图二所示,一层RDL WLCSP的主要制造流程步骤有:

- 清洗前端制程完成后的晶圆,通常使用超声波清洗

- 旋涂Spin coating介电层,常用的介电层材料有聚酰亚胺(PI)苯并环丁烯 (BCB)、聚苯并双恶唑 (PBO) 等聚合物, 偶尔也会用到基板材料ABF等。

- 固化介电层,通常需要一个小时。介电层的厚度通常在4-7微米之间

- 旋涂Spin coating涂上光刻胶

- 然后使用光刻技术(对准,曝光,显影)在光刻胶层对应芯片pads的地方打开通孔。然后通常用干法蚀刻 PI、BCB或PBO介电层。介电层通孔完成后剥离光刻胶。取决于线距线宽,bump pitch等因素,也可以使用激光直接在介电层上钻孔。这种方案更经济,流程也更简单。

- 在整个晶圆上溅射钛铜种子层,通常种子层相对来说比较薄,不超过2微米

- 旋涂光刻胶

- 通过曝光显影等来定义金属层结构

- 在光刻胶开口处电镀铜,也可以根据需要来电镀镍钯金

- 剥离光刻胶

- 蚀刻掉钛铜种子层

- 旋涂Spin coating介电层

- 旋涂Spin coating涂上光刻胶

- 然后使用光刻技术(对准,曝光,显影)在光刻胶层对应焊盘凸点的地方打开通孔。然后通常用干法蚀刻 PI、BCB 或 PBO介电层。介电层通孔完成后剥离光刻胶

- 在整个晶片上溅射钛铜种子层

- 涂上光刻胶和掩模,然后用光刻技术打开凸点焊盘上的通孔以暴露带有 UBM 的区域

- 电镀铜芯

- 电镀焊料,通常是SnAg等材料

- 剥离光刻胶

- 蚀刻掉钛铜种子层

- 涂抹助焊剂并回流焊料

多层RDL WLCSP的制造工艺,就是重复步骤2-11。另外PI材料本身就是一种光刻胶,所以在使用PI作为介电材料层时,光刻胶相关的步骤就可以略去。

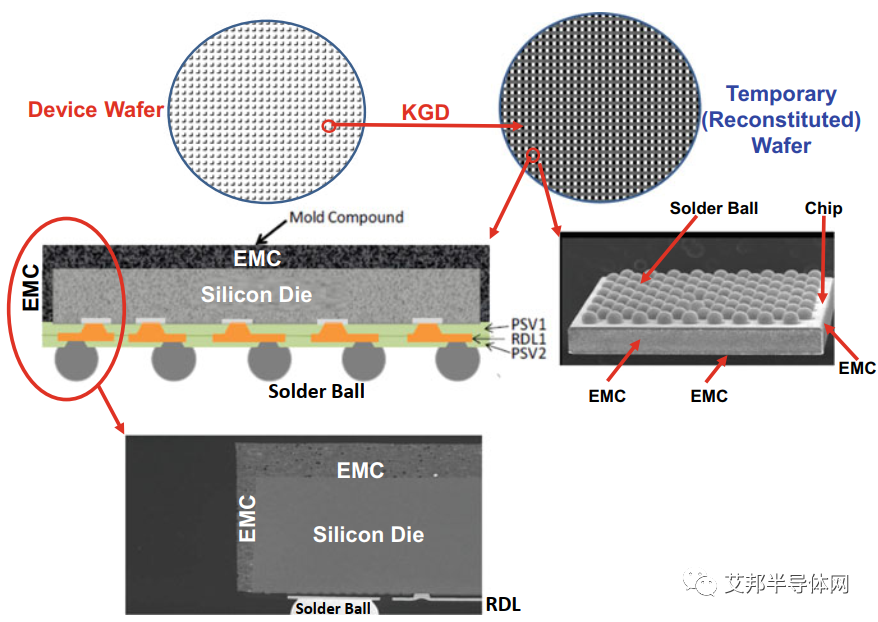

只有正面有介电层的WLCSP芯片的mechanical reliability是相对比较差的。背面碎裂和侧壁开裂等failure modes相当程度上限制WLCSP的应用。成本较高的5面甚至6面塑封WLCSP封装工艺大大改进了可靠性,进而也越来越受欢迎。星科金朋(2015年被长电收购)在2011年公布了他们的5面塑封WLCSP专利,他们称之为eWLCSP,如图三所示。芯片的背面和四个侧面都受到塑封料保护。值得指出的是eWLCSP跟eWLB技术是非常类似的。关注艾邦,今后我们还会详细讲讲eWLB技术。星科金朋的eWLCSP跟Chip first face down扇出型工艺非常类似。Device wafer经过CP测试后被切割成一个个芯片。良品芯片被选择出来重新贴装到一个晶圆载板上。塑封后把芯片从晶圆载板脱离开。在芯片的正面做重布线层,植球等,最后切割成一个个单颗eWLCSP芯片。

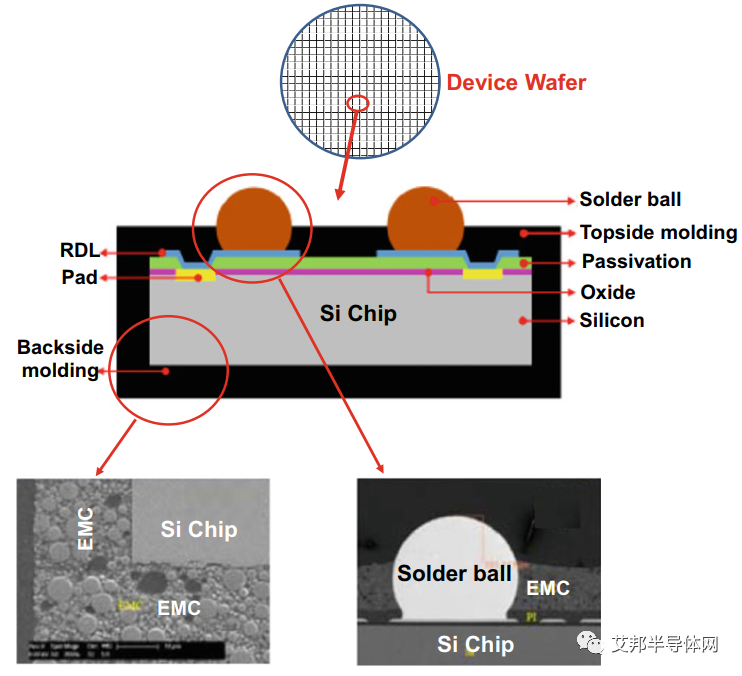

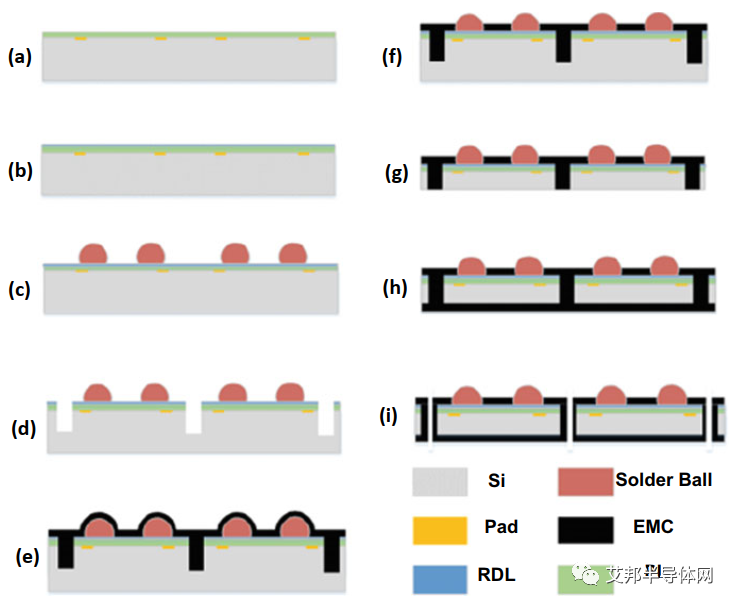

新加坡的UTAC公司,台湾的矽品公司和大陆的华天科技分别在2015年,2016年和2018年推出了6面受保护的WLCSP,如图四所示。UTAC公司的WLCSP芯片的四个侧面和正面受到环氧树脂保护,芯片的背面则是由传统的胶带贴膜的方法。矽品和华天科技公司则是推出了6面都受环氧树脂保护的WLCSP芯片制造工艺。这三家公司的WLCSP工艺是非常相似,不同之处在于他们背面芯片的保护层工艺。他们都没有像星科金朋那样去先切割和临时键合到一个晶圆载板上再塑封,然后翻过来再去来制作重布线,植球,划片等工艺。如图五所示,他们的工艺流程大体可以分成以下步骤:

- 清洗前端制程完成后的晶圆

- 重布线层制作

- 植球

- 晶圆厚度部分切割

- 晶圆正面塑封

- 背部研磨直到都出环氧树脂层

- 芯片背部塑封

- 切割

受益消费电子、汽车电子等小尺寸芯片的需求拉动,WLCSP 封装的市场容量已结占到先进封装总量的约12%。我们预计WLCSP封装市场容量有望进一步提升。艾邦半导体在后面的文章中会接着这个话题讨论PLCSP封装工艺和市场现状。

参考文献:

- Elenius, P., and H. Hollack, “Method for forming chip scale package,” US patent 6,287,893

- Strothmann, T., S. Yoon, and Y. Lin, “Encapsulated Wafer Level Package Technology (eWLCSP)”, Proceedings of IEEE/ECTC, May 2014, pp. 931–934

- Zhao, S., F. Qin, M. Yang, M. Xiang, and D. Yu, “Study on warpage evolution for six-side molded WLCSP based on finite element analysis”, Proceeding of the International Conference on Electronic Packaging Technology (ICEPT), August 2019, pp. 1–4

- Lau, J. H., C. Ko, T. Tseng, T. Peng, K. Yang, C. Xia, P. Lin, E. Lin, L.N. Liu, C. Lin, D. Cheng, and W. Lu, “Six-Side Molded Panel-Level Chip-Scale Package with Multiple Diced Wafers”, IMAPS Transactions, Journal of Microelectronics and Electronic Packaging, Vol. 17, December 2020, pp. 111–120

- Qin, F., S. Zhao, Y. Dai, M. Yang, M. Xiang, and D. Yu, “Study of Warpage Evolution and Control for Six-Side Molded WLCSP in Different Packaging Processes”, IEEE Transactions on CPMT, Vol. 10, No. 4, April 2020, pp. 730–738

原文始发于微信公众号(艾邦半导体网):晶圆级封装(WLCSP)简介

成员: 5306人, 热度: 153517

陶瓷 天线 通讯 终端 汽车配件 滤波器 电子陶瓷 LTCC MLCC HTCC DBC AMB DPC 厚膜基板 氧化铝粉体 氮化铝粉体 氮化硅粉体 碳化硅粉体 氧化铍粉体 粉体 生瓷带 陶瓷基板 氧化铝基板 切割机 线路板 铜材 氮化铝基板 氧化铍基板 碳化硅基板 氮化硅基板 玻璃粉 集成电路 镀膜设备 靶材 电子元件 封装 传感器 导电材料 电子浆料 划片机 稀土氧化物 耐火材料 电感 电容 电镀 电镀设备 电镀加工 代工 等离子设备 贴片 耗材 网版 自动化 烧结炉 流延机 磨抛设备 曝光显影 砂磨机 打孔机 激光设备 印刷机 包装机 叠层机 检测设备 设备配件 添加剂 薄膜 材料 粘合剂 高校研究所 清洗 二氧化钛 贸易 设备 代理 其他 LED