通过减少空调使用时间,拔掉不使用的电子设备插头……你是否也会通过这些方式来节电?节电有助于减少碳排放,从而改善气候变化。三星半导体为了减少数据中心使用的能源消耗,制造出了低功耗内存芯片。

从人工智能 (AI)到第五代移动通信技术 (5G)、物联网 (IoT) 再到自动驾驶汽车,芯片已成为第四次工业革命时代的核心技术之一。随着芯片技术的先进化和复杂化,制造芯片的工艺技术也在快速发展。随着下一代设备逐渐小型化,芯片也变得越来越小,超微工艺技术也变得愈发重要。

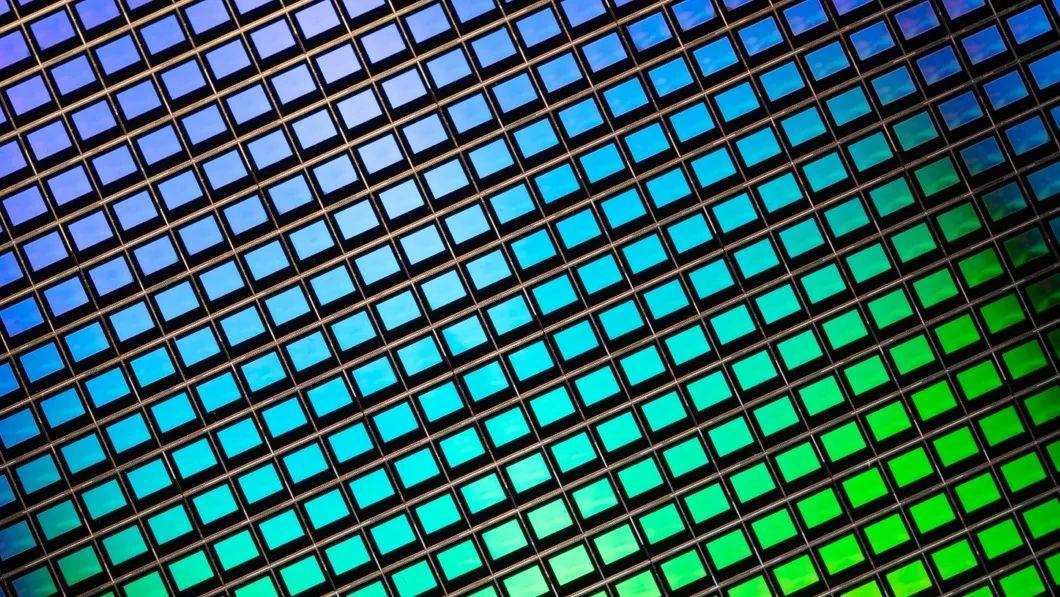

制作芯片,首先需要在晶圆上刻画极其精细的电路图案。晶圆是一种用于制造半导体集成电路的薄盘。在这个直径只有300毫米的晶圆中,放置的半导体元件越多,其性能就越高。

EUV(极紫外光刻)运用更加精准的13.5纳米 (nm)波长,这比现有的氟化氩 (ArF) 激光技术短14倍,可以实现7nm 以下的精细电路图。EUV不仅可以提高芯片的性能和能效,还能减少工艺中的步骤,在降低最终产品能耗的同时提高生产率。

三星不断创新,不仅是为了制造出更优秀的产品,也是为了更好地保护环境。三星已将三维立体堆叠式封装技术“X-Cube(eXtended-Cube)”应用于系统半导体。X-Cube 是一种将多个晶圆垂直堆叠到单个芯片中的技术,它可以减小芯片整体尺寸。借助X-Cube ,芯片设计人员可以更灵活地构建大容量存储解决方案,显著提高数据处理速度和能源效率,同时降低能源对环境的影响。

三星坚持不断创新,以实现可持续发展的环境。从人工智能到5G、物联网,再到自动驾驶汽车,三星正在推动第四次工业革命的发展。

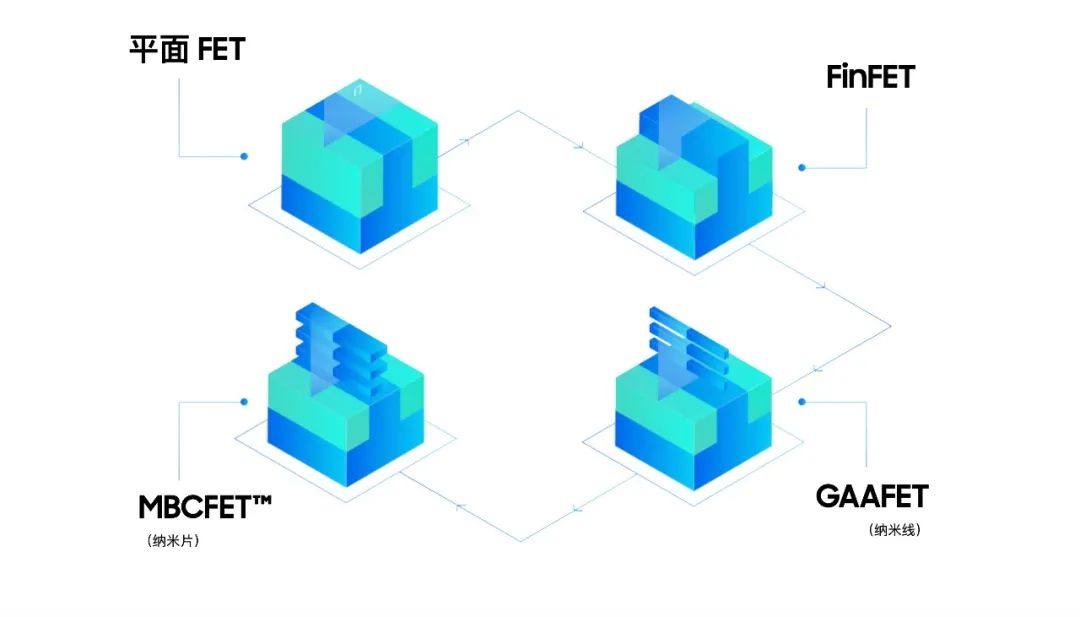

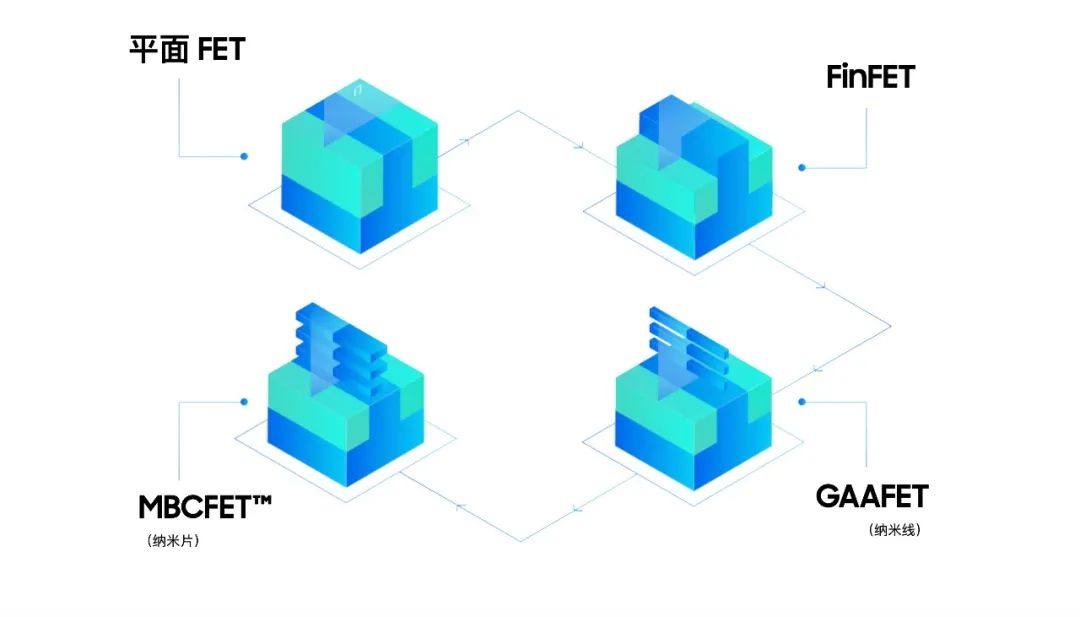

3纳米GAA (MBCFET®)

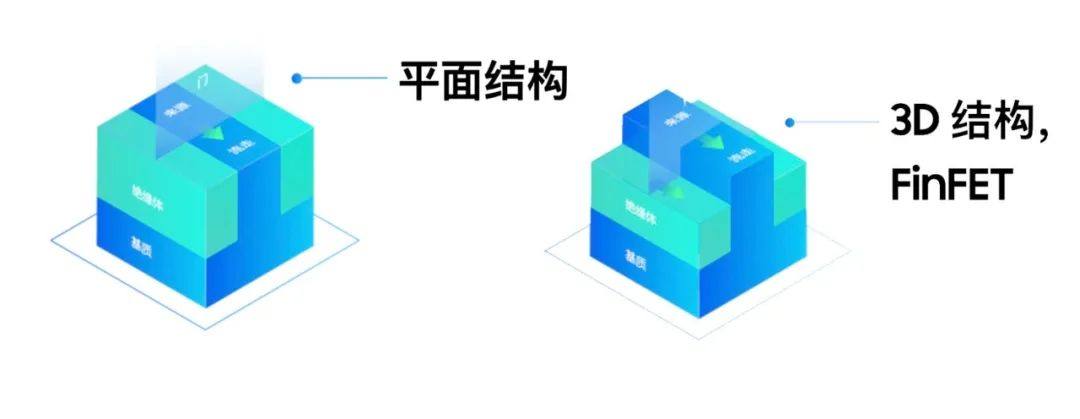

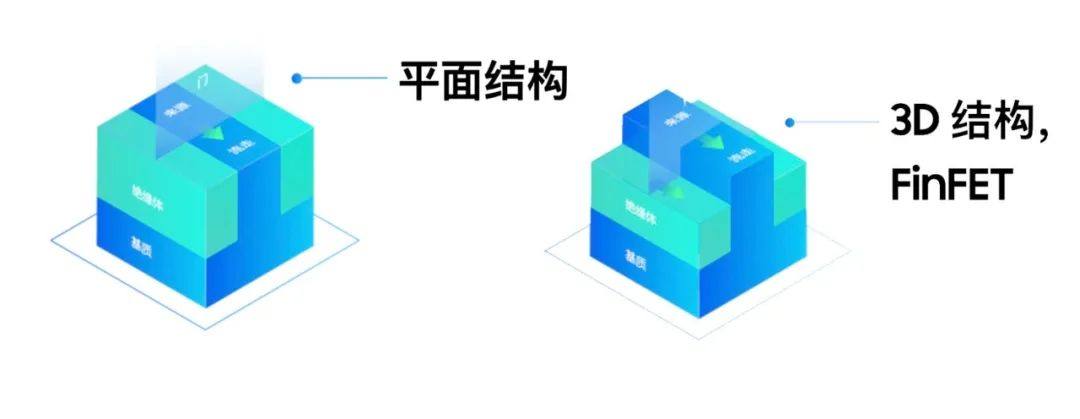

从二维 (2D)到三维 (3D)

芯片是由多个晶体管组成的,这些晶体管具有扩大电流流动或开关的作用。当向栅极施加电压时,通过沟道可以使电流从源极流到漏极。在平面(2D)结构中,晶体管的栅极和沟道与同一个表面接触。如果为了制造体积小、低功耗的芯片,缩小晶体管尺寸的话,那么源极和漏极之间的距离会变近,会导致栅极无法正常工作,发生漏电的短沟道效应等问题,因此,在降低工作电压方面存在局限性。

为改善这一点,一种叫“FinFET”的三维(3D)结构工艺技术得以开发。这种结构看上去像鱼鳍的形状,所以被称为“鳍式场效应晶体管”。栅极和通道间的接触面越大,效率越高。FinFET通过采用3D结构,使栅极和通道拥有三个接触面,增大了接触面积,提升了芯片性能。但是,在4纳米以下的工艺中,FinFET存在工作电压无法持续降低的局限性。

■新一代3纳米GAA结构,可以进一步降低超精细电路的运行电压

在3纳米以下的超精细电路中使用GAA(Gate All Around,全环绕式栅极)结构的晶体管时,栅极环绕通道四个侧面,可以更好地控制电流,实现更高能效。

■通过三星独特的GAA技术——MBCFET™(Multi Bridge Channel FET,多桥通道场效晶体管),可以获得更高能效

在直径为1nm的细导线通道上保持足够的电流是很困难的,三星MBCFET™通过长而薄的纳米表层使此过程变的容易,提高性能和能效得以提高。

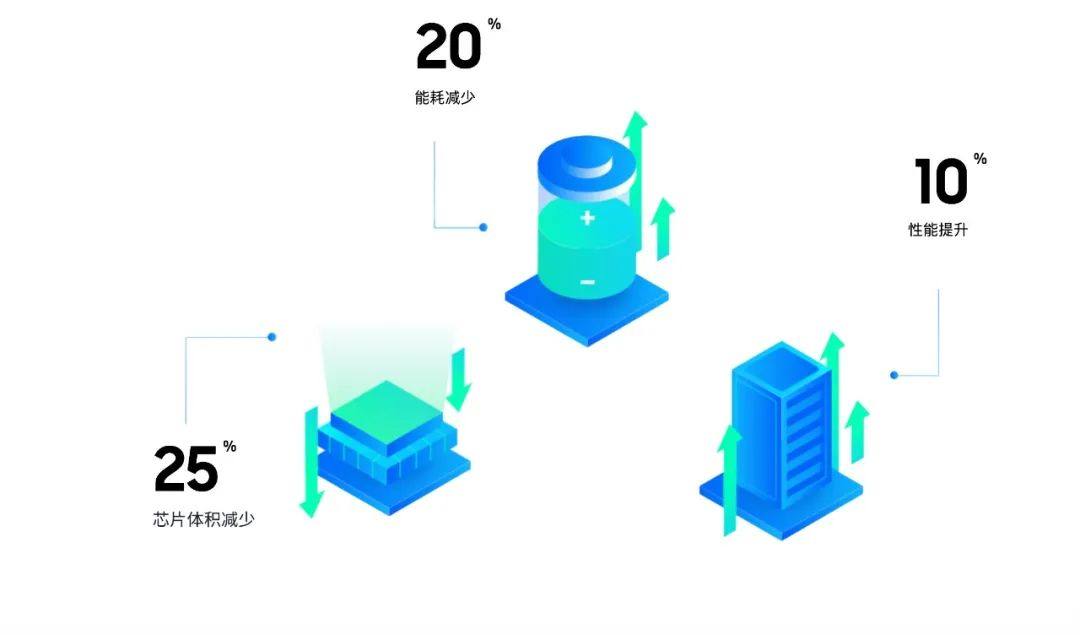

与7nm FinFET相比,MBCFET™能将芯片体积减少 25%,能耗降低约20%,性能提高约10%。

为了保护地球,三星一直积极探索,不断创新研发高性能以及低功耗的绿色产品和工艺,为可持续发展贡献智慧方案。

*本文中的产品图片以及型号、数据、功能、性能、规格参数等仅供参考,三星有可能对上述内容进行改进,具体信息请参照产品实物、产品说明书或三星官网(www.samsung.com/cn)。除非经特殊说明,本网站中所涉及的数据均为三星内部测试结果,涉及的对比均为与三星产品相比较。

原文始发于微信公众号(三星半导体和显示官方):三星半导体|以绿色工艺,制造绿色芯片