三星电子计划在2024年推出先进的3D芯片封装技术SAINT,希望将多个元件聚集在一起封装成单一电子元件,从而提高半导体性能。三星电子还表示,将在2025年开发针对高层HBM的无凸点封装(Cu-Cu直接键合或混合键合)。

近年来,随着多核处理、人工智能(AI)、物联网(IoT)等技术的快速发展,芯片的集成度和性能越来越高,对封装尺寸和成本的要求也越来越严格。传统的封装技术已经无法满足新一代芯片的封装需求。

封装领域的一个突出进步是3D Cu-Cu混合键合技术,它提供了一种高密度、低成本、高性能的方案,可以有效提高封装的可靠性和稳定性,同时降低成本和尺寸。这一变革性的解决方案有助于实现高速、低延迟的芯片互连,提高系统性能和能效。

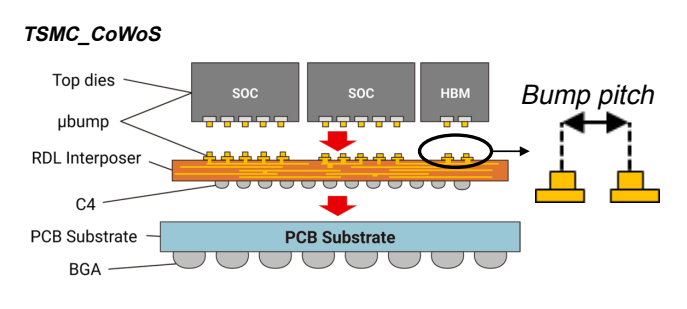

凸点间距与先进半导体封装

1965年发明了第一个半导体封装,此后封装技术不断发展。现在,有许多封装技术,从最广泛使用的引线键合到最先进的3DIC。之所以叫先进半导体封装,一种分类方法是看凸点间距的大小。较小的凸点间距意味着更多的I/O数,即更高的互连密度,这是许多高计算应用所必需的。通常,我们将先进半导体封装定义为凸点间距小于100µm的任何封装。

凸点间距

I/O数是随着凸点间距的减小而增加的,例如:10µm凸点间距封装技术可以提供大约400倍于200µm凸点间距封装技术的I/O数。

Cu-Cu混合键合的典型应用

Cu-Cu混合键合技术可以提高封装的可靠性和稳定性。在传统的封装技术中,芯片与基板之间的连接通常采用引线或载带等方式,这些连接方式容易受机械振动、温度变化等因素的影响,导致连接失效或损坏。而Cu-Cu混合键合的连接具有更高的强度和稳定性,可有效地提高封装的可靠性和稳定性。

此外,Cu-Cu混合键合技术的制造工艺相对简单,可实现晶圆级大规模生产,从而降低成本并提高效率。该技术可应用于不同类型的芯片和基板材料,具有广泛的适用性,特别是在高密度、高性能的封装中具有显著优势。Cu-Cu混合键合的典型应用包括:

-

倒装芯片封装(FC):在倒装芯片封装中,通过Cu-Cu混合键合实现芯片的凸点与基板的相应触点互连。这种封装方式具有高密度、高性能的特点,广泛应用于高性能计算、通信、军事等领域。

-

3D封装:在芯片堆叠封装中,通过Cu-Cu混合键合实现芯片之间的互连,将多个芯片堆叠在一起,从而在有限的空间内增加更多的功能和性能。这种封装方式在智能手机、平板电脑等便携式设备中应用很广。

-

晶圆级封装:将整个晶圆封装在一起,通过Cu-Cu混合键合实现芯片之间的互连。这种封装方式具有高密度、低成本、小型化的特点,广泛应用于各种高性能集成电路。

传统凸点工艺难以缩小间距

在传统的倒装芯片焊接工艺中,凸点间距被限制在40μm-50μm,无铅焊料和Cu在230℃左右熔化后可形成稳定的接点,接点间需要底部填充物来提高其机械性能。不过,热膨胀失配可能导致翘曲和管芯移位等可靠性问题。

当凸点间距减小到大约10μm时,焊球尺寸的减小增加了形成金属间化合物(IMC)的风险,降低了IMC点的导电值和机械性能。此外,如果凸点间距太小,相邻的焊球可能会接触到,在回流焊过程中出现桥接现象导致芯片故障。而焊料和IMC的电阻率大约是Cu的十倍,不适合高性能组件封装。

另外,随着焊料凸点间距的缩小,用于接合的凸点高度和表面积的减小使得建立可靠的电连接变得越来越困难,需要精确的制造工艺来避免误差。为此,关键的共面性和表面粗糙度变得至关重要,因为即使是微小的不规则性也会影响键合的成功。

由于采用较小的Cu柱和凸点直径,制造中面临蚀刻困难等障碍,更有可能发生过腐蚀(undercutting)。另外,由于有效确保均匀性和控制共面性变得更加困难,电化学沉积(ECD)镀层的复杂性也会增加。而且,随着凸点尺寸的不断缩小,键合质量对凸点共面性、表面粗糙度和硬度等因素的敏感性使其对温度、时间和压力等参数的调整变得更加复杂。

为了解决倒装焊的局限性难题,行业提出了Cu-Cu混合键合技术。该技术是在介电材料之间嵌入金属触点,并使用热处理使Cu原子固态扩散将材料连接在一起,消除了焊接时遇到的桥接问题。Cu工艺是半导体行业中公认的技术,可以实现小于1μm的凸点间距。

与倒装焊相比,混合焊的优点显而易见。首先,它实现了超细间距和小接点尺寸,有助于实现高I/O数。因为器件需要越来越多的连接来满足性能要求,这对现代半导体封装至关重要;其次,与通常依赖于底部填充材料的倒装焊不同,Cu-Cu混合键合无需进行底部填充,降低了寄生电容、电阻和电感及热阻;最后,Cu-Cu混合键合中减小了连接厚度,几乎消除了倒装芯片技术中10-30μm厚度的焊球,为更紧凑、更高效的半导体封装开辟了新的可能性。

Cu-Cu混合键合面临的挑战

Cu-Cu混合键合技术为先进半导体封装带来了巨大的前景,但它也带来了一系列挑战,需要有针对未来发展的创新解决方案。

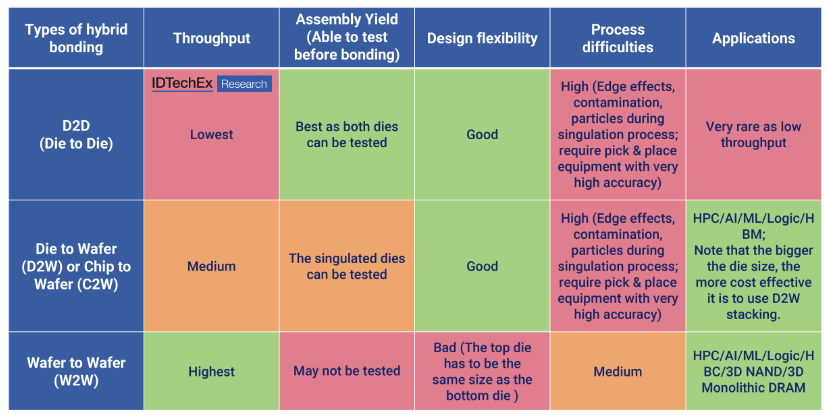

目前有三种Cu-Cu混合键合方式:晶圆对晶圆(W2W)工艺是最常用的工艺;管芯对晶圆(D2W)或芯片对晶圆(C2W)工艺正处于密集研发中,因为这两种方法可以满足更多需要集成不同尺寸管芯的应用。

Cu-Cu混合键合的三种方法和应用

对于这三种方式,制造中的一个关键是键合环境,通过化学机械抛光(CMP)优化实现平坦清洁的介电表面至关重要。此外,介电材料能够承受较低退火温度和较短持续时间,对于最大限度地减少键合过程中晶圆变形和翘曲的可能性也很重要。Cu解决方案的优化电化学沉积(ECD)还可以减少退火时间并降低退火温度,从而提高效率。

在D2W/C2W工艺的情况下,重要的是解决与划片(die singulation)和边缘效应相关的挑战,并最大限度地减少对管芯和晶圆的污染。高精度贴片机对于确保精确的管芯放置非常必要,可以将误差缩小到0.2µm。为了适应可能的放置误差,必须有更大的Cu焊盘。此外,先进的薄晶圆处理技术将在确保成功实现Cu-Cu混合键合方面发挥重要作用。

Cu-Cu混合键合的步骤

Cu-Cu混合键合的实现需要经过几个步骤。首先,按照芯片大小将晶圆分割成单一的晶粒,以用于随后的芯片贴装、引线键合等工序。第二步是表面处理,使用化学等手段对晶圆表面进行清洁、去氧化层等处理,以去除表面的污染物和氧化层,提高键合质量。然后对晶圆表面进行研磨抛光,以去除表面的粗糙度和缺陷,提高表面平整度和键合可靠性。切割和研磨抛光操作需要精确控制,以确保晶圆的尺寸和厚度符合要求。

前期处理是Cu-Cu混合键合的重要步骤之一,其目的是为了确保晶圆的表面状态和尺寸精度符合要求,以提高键合质量和可靠性。

在进行键合准备时,需要进行预热和压力调节。首先将芯片和基板分别放置在预热炉中进行预热,以达到适宜的键合温度。预热温度的选择应根据芯片和基板材料的特性合理调整;同时还需要调整键合机压力,使其能够正确施加在芯片和基板之间,以确保键合的牢固性和稳定性。

在键合操作过程中,需要严格控制键合温度、压力和时间等参数,以确保键合的质量和可靠性。

总之,Cu-Cu混合键合作为一种先进的芯片连接技术,在微电子封装领域具有广泛的应用前景。Cu-Cu混合键合的未来发展可能将集中在精炼和优化工艺方面,包括CMP、介电材料、ECD(电化学沉积)解决方案、贴片机的进步,以及处理薄晶圆的创新。克服这些挑战将为在先进半导体封装中更广泛地采用Cu-Cu混合键合铺平道路,从而能够制造出更小、功能更强大、更节能的电子器件。

END

原文始发于微信公众号(TechSugar):化解先进半导体封装挑战,有一个工艺不能不说