安森美 (onsemi) 1200V碳化硅 (SiC) MOSFET M3S系列专注于提高开关性能,相比于第一代1200V碳化硅MOSFET,除了降低特定电阻RSP (即RDS(ON)*Area) ,还针对工业电源系统中的高功率应用进行了优化。此前我们描述了M3S的一些关键特性以及与第一代相比的显著性能提升,本文则将重点介绍M3S产品的设计注意事项和使用技巧。

由于NTH4L022N120M3S的阈值电压具有 NTC,因此在最高结温TJ(MAX) = 175°C时具有最低值。即使数据表中的典型VGS(TH)为2.72V,但在考虑样品25%的工艺变化和温度系数的最坏情况下,它可能会降至1.5V。这意味着超过1.5V的噪声会导致开启。这具有很大的潜在风险,因此需要考虑抑制噪声,这使得设计变得困难和复杂。

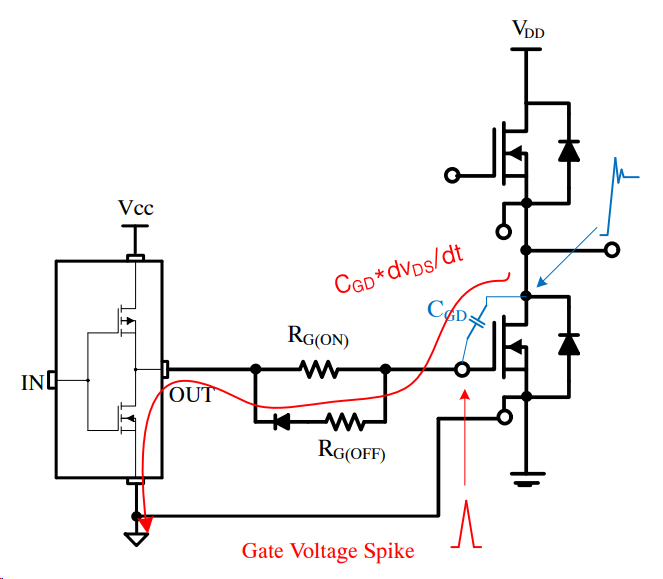

即使成功抑制,由于电桥应用中的米勒电容器,可能会因所谓的寄生导通效应而导通,如图9 (a)所示。当上开关导通时,下开关两端的电压变化为dVCE/dt。电流通过寄生米勒电容CGD和外部电阻流入地。该电流可近似表示为CGD*dVCE/dt,会在路径中的电阻器上产生压降。如果电压超过阈值电压,即使在关断后也会引发寄生导通。

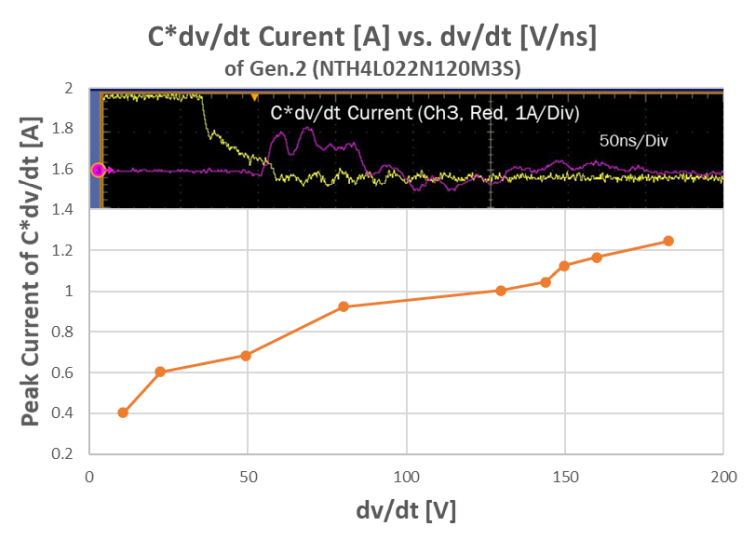

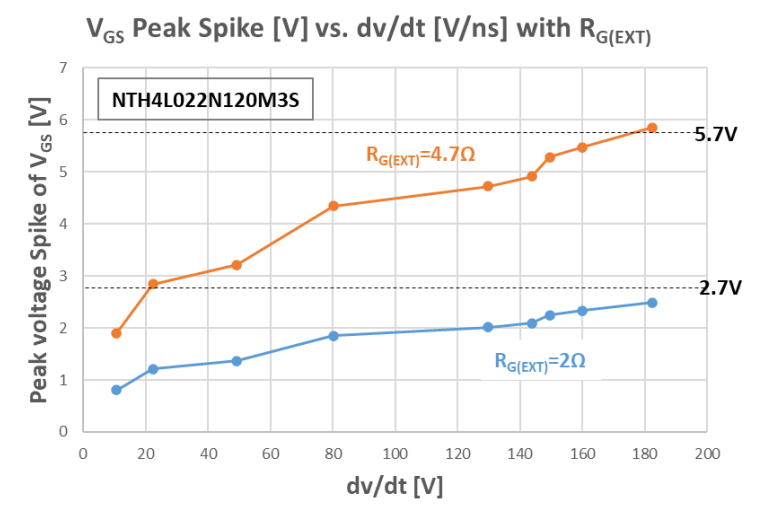

图9 (b)中的红色波形显示了通过该路径测得的电流。电流峰值与dv/dt成正比,并导致电阻器两端产生峰值电压。这意味着该电流将限制外部栅极电阻(RG(ON)和RG(OFF))的选择。图9 (c)是峰值电压值,通过电流乘以路径中的总外部电阻RG(EXT) 计算得出。较高的 RG(EXT)会导致较高的电压尖峰,因此面临意外开启的风险。如果VGS(TH)为2.72V并且不使用负偏压,则RG(EXT) = 4.7Ω,因寄生导通的可能性较高,所以要限制使用。而RG(EXT)= 2Ω则没有问题。在所有dv/dt范围内避免超过VGS(TH)的情况。增加RG(EXT)可以降低dv/dt,但要计算增加RG(EXT)后dv/dt的减少值,电压峰值增加值,这将导致在电桥应用中,选择合适的电阻变得困难。

有四种缓解方案可以建议,第一种是单独导通和关断栅极电阻以改变电阻,第二种是在栅极和源极之间添加电容以分流米勒电流,第三种是使用负栅极偏置电压来提高阈值电压, 最后是使用额外的晶体管进行有源米勒钳位。避免此问题的有效且简单的方法是使用负电源电压。图9(c)中,如果施加-3V,则实际阈值电压变为5.72V,因此可以更灵活地选择栅极电阻。

(a) 寄生导通机制

(b) 测量的米勒电流与 dv/dt

(c) VGS 尖峰峰值电压与 dv/dt 的关系

图 9. 寄生导通现象

与硅MOSFET通常使用10V和IGBT通常使用15V作为栅极驱动电压不同,碳化硅MOSFET由制造商根据不同的VGS(OP)条件或根据每个产品进行推荐。这可能意味着该技术尚未成熟,仍然有许多挑战需要克服,例如SiC/SiO2界面缺陷、沟道迁移率差、栅极氧化物质量和VGS(TH)稳定性问题。

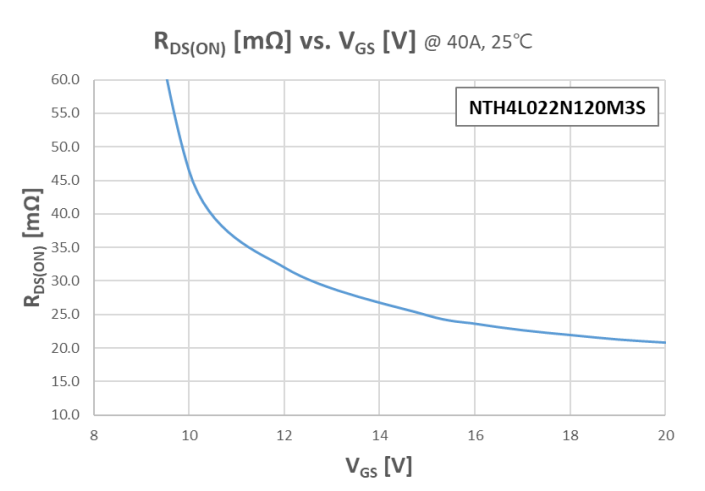

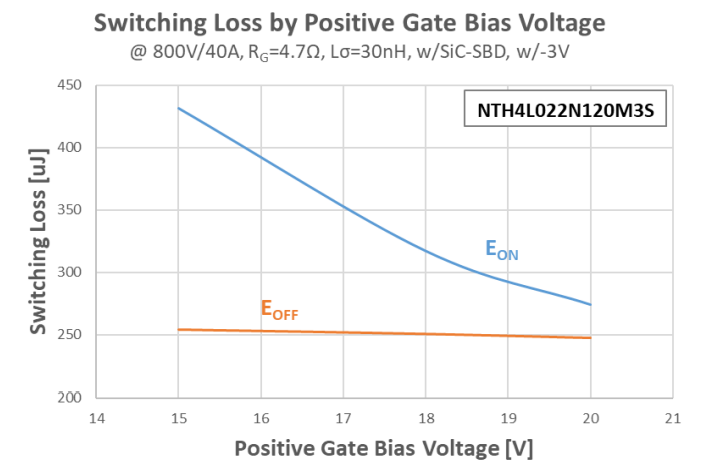

随着正栅极偏压的增加,导通电阻(RDS(ON))降低,并且使外部碳化硅SBD的导通开关损耗(EON)降低,但关断开关损耗(EOFF)没有大的变化,如图10(a)和(b)所示。需要在栅极驱动电路设计上更仔细,并会导致更高的栅极驱动损耗。增加的电压和不可避免的电压尖峰将对栅极氧化物造成更大的压力。众所周知,较高的正偏压会导致VGS(TH)产生更大的漂移,从而导致RDS(ON)和EON/EOFF等电气性能下降。

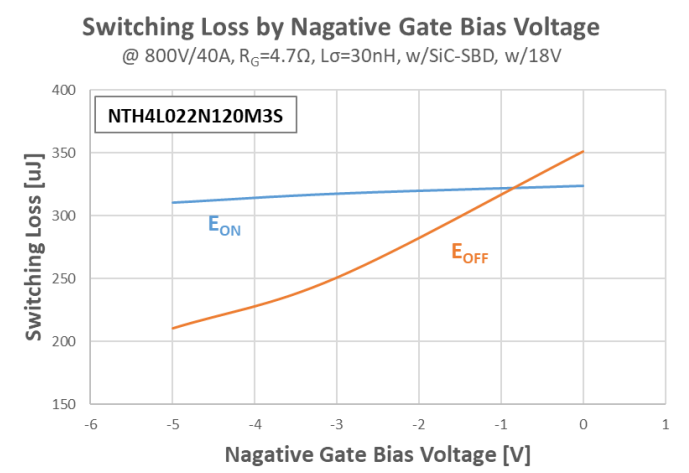

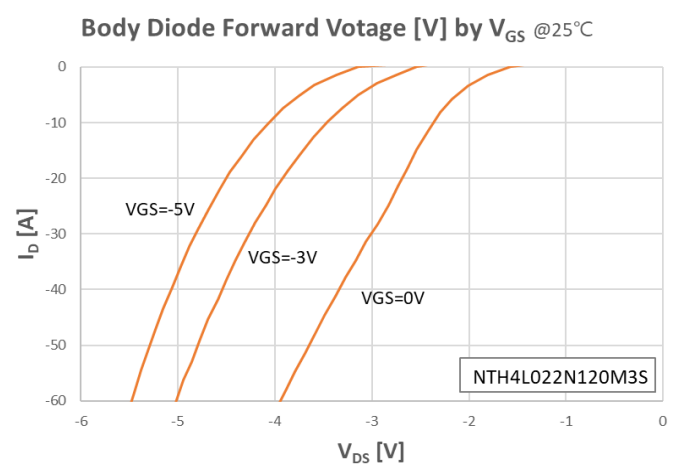

负栅极偏压增加到负值,关断开关损耗 (EOFF) 会降低,导通开关损耗 (EON) 没有变化,如图 10 (c) 所示。在体二极管中,正向电压 (VF) 增加,如图10 (d)所示,这是由于VGS=0V时沟道关闭不稳定以及负偏压增加时,沟道电流减少所致。反向恢复特性会稍微变差。同样,也会对栅极氧化层产生更大的应力,因此可能导致VGS(TH)发生更大的漂移,并且高电源电压可能会给栅极驱动电路设计增加复杂性。

综上,一般建议1200 V M3S产品采用−3/18V,如“VGS(OP),推荐工作栅极电压”部分所述,这是通过综合考虑性能和可靠性,提出的优化建议。可以选择不同电压来优化每个应用的工作状态。例如,如果设计人员希望体二极管具有较低的VF,并且可以接受EOFF增加,那么0V驱动是不错的选择。如果不能满足 EMI 规定,并且在效率和热性能方面有足够的余量,那么15V驱动将是一个不错的选择。

(a) 根据正栅极偏压的RDS(ON)

(b) 根据正栅极偏压的开关损耗

(c) 根据负栅极偏置的开关损耗

(d) 根据负栅极偏压的正向电压

图 10. 根据VGS的性能

在开关性能方面,RG(EXT)越小,开关损耗越低。但是,对栅极的强驱动会导致di/dt和dv/dt过高,电路板中的寄生电感和电容会导致电压和电流急剧尖峰,以及高频L/C谐振。设计人员应找到合适的RG(EXT),以满足符合EMI下的最佳性能。

图11(a)描述了一般开关波形中EMI干扰的主要来源。所有这些EMI源都与di/dt和dv/dt有关。高di/dt导致寄生电感上的电压尖峰L*di/dt,高dv/dt导致寄生电容中的电流尖峰C*di/dt。并且两者都会触发数十或数百MHz的L/C谐振振荡,直接影响EMI。

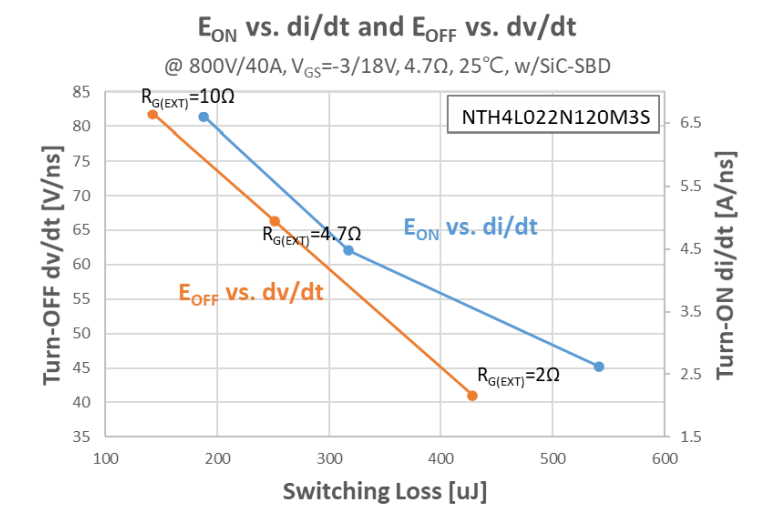

图11(b)表明,在相同的反向恢复条件下,EON由导通di/dt主导,而EOFF由关断dv/dt主导。在开关性能和EMI之间处于权衡关系。如果VGS(OP)固定,则可以通过RG(EXT)来控制,因此需要优化RG(EXT)。如果PCB布局不好,寄生参数很高,可能无法通过给定的di/dt和dv/dt满足EMI规范,如果没有机会进一步修改PCB布局以最小化寄生元件,则需要通过增加RG(EXT)来降低di/dt和dv/dt。才有可能满足EMI规范,代价是牺牲系统效率。

(a) 开关中的EMI源

(b) di/dt和dv/dt通过RG(EXT)

图 11. EMI考虑因素

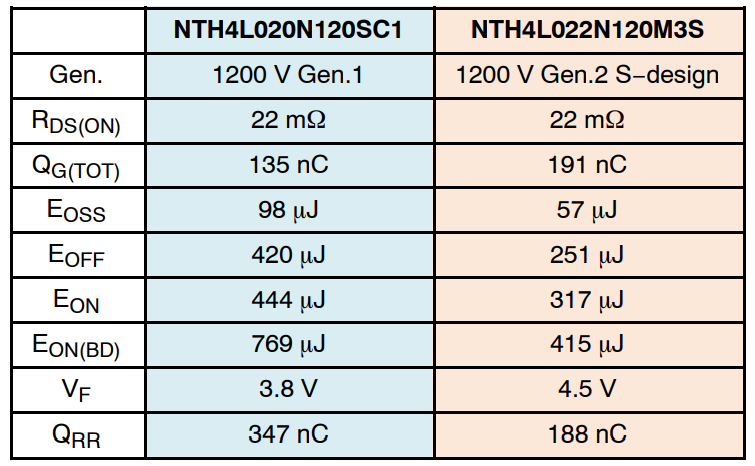

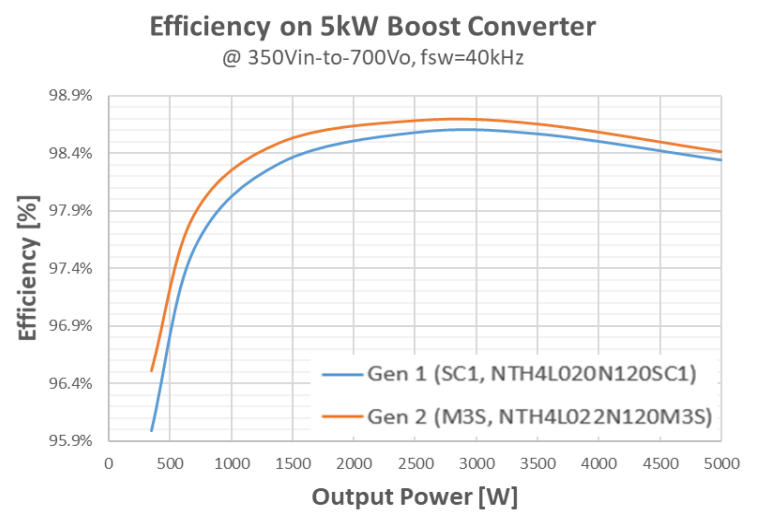

本应用笔记介绍了安森美1200V M3S碳化硅MOSFET与第一代SC1相比的主要特性,可以看出M3S取得了显著的改进,如表3所示。图12显示了系统的实际性能,在40kHz开关频率下测量的5kW升压变换器的效率。结果明确显示M3S比SC1表现更好,特别是在轻负载下,在该范围内开关性能占主导地位,因此说M3S是更适合高开关频率应用的产品。

表 3. 主要性能比较汇总表,所有数据均在同一测试台上、在一个典型样品的条件下进行测量。(VGS = −3 / 18V,RG(EXT) = 4.7Ω,VDS = 800V,ID= 40A,Lσ = 30nH, 14A灌/拉驱动器, 25°C, di/dtRR = 2A/ns)

图 12. 5kW升压转换器的测量效率

原文始发于微信公众号(安森美):安森美1200V碳化硅MOSFET M3S系列设计注意事项,您知道吗?