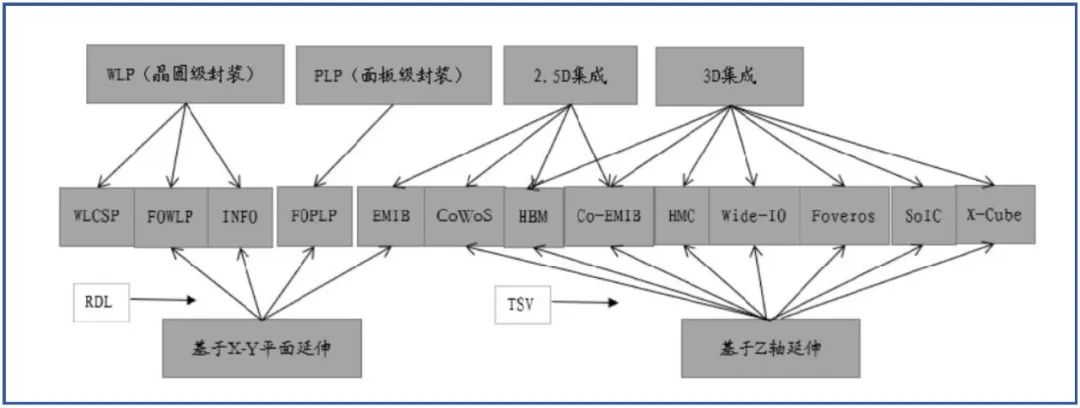

先进封装 (AP) 是指封装集成电路 (IC) 以提高性能的多种创新技术。与传统封装相比,它具有高集成度、工艺方法更加多元以及更优的导电和散热性能等优点。

先进封装的结构大致包括:倒装芯片(Flip-Chip,FC)、2.5D封装与3D封装、晶圆级封装(Wafer Level Package,WLP)、系统级封装(SiP)、Chiplet。

先进封装的工艺大致含有:Bump(凸块)工艺、RDL(重布线层)工艺、TSV(硅通孔)工艺。

先进封装结构

-

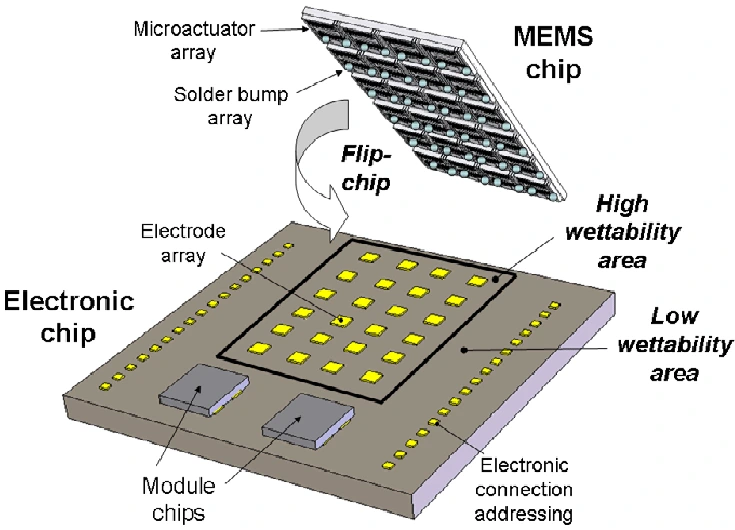

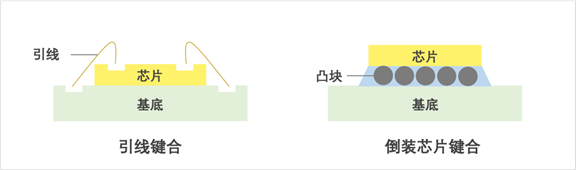

倒装芯片(Flip chip)

在传统封装技术中,芯片被封装在底部,并通过金线连接到封装基板上。而倒装芯片技术则将芯片直接翻转并安装在封装基板上,然后使用微小的焊点或导电胶水进行连接。这种封装技术具有较高的信号密度、较小的体积、高速传输和良好的热传导性能,因此在半导体行业得到了广泛应用。

-

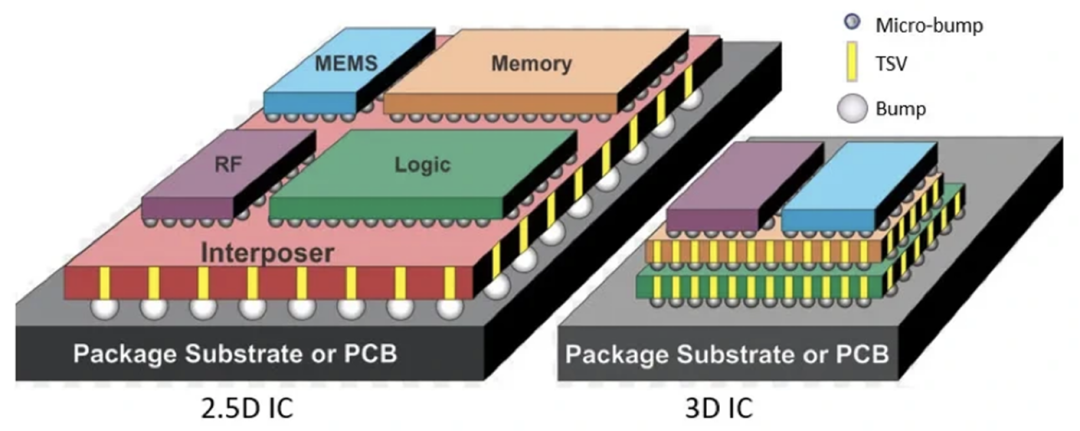

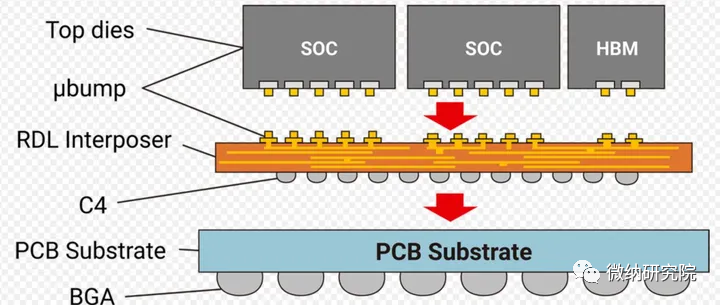

2.5D封装与3D 封装

2.5D 封装:采用硅或重分布层 (RDL) 扇出的中介层被用于在 SoC 的裸片之间路由信号;3D 封装:采用混合键合或以上技术的某种组合来实现芯片的垂直堆叠。

2.5D/3D 堆叠封装涉及垂直堆叠多个裸片或芯片,形成三维结构。该平台可实现更高的集成度、更高的性能和更小的外形尺寸,使其成为应对人工智能、5G 和 HPC 应用挑战的重要技术。

-

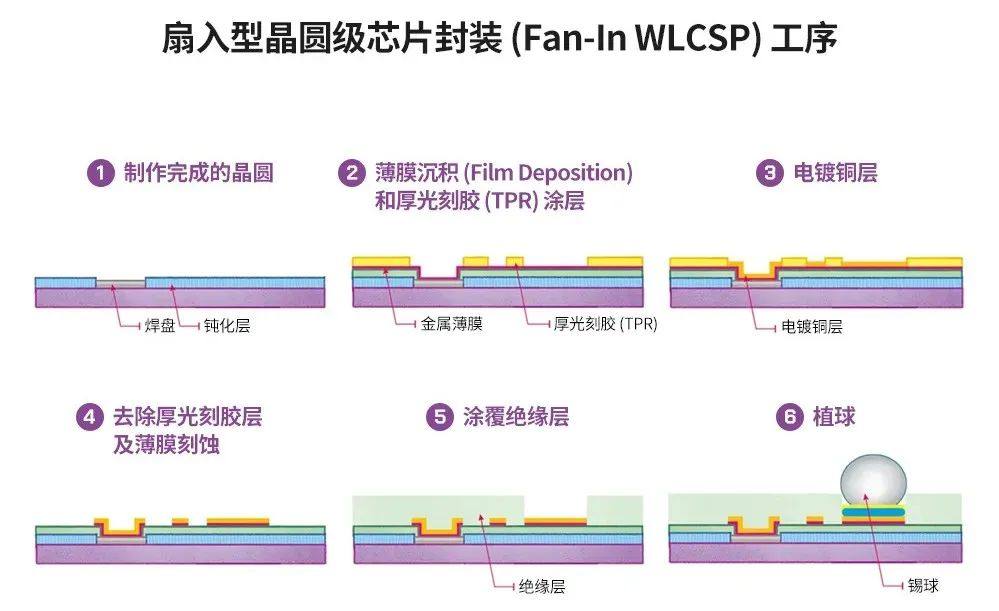

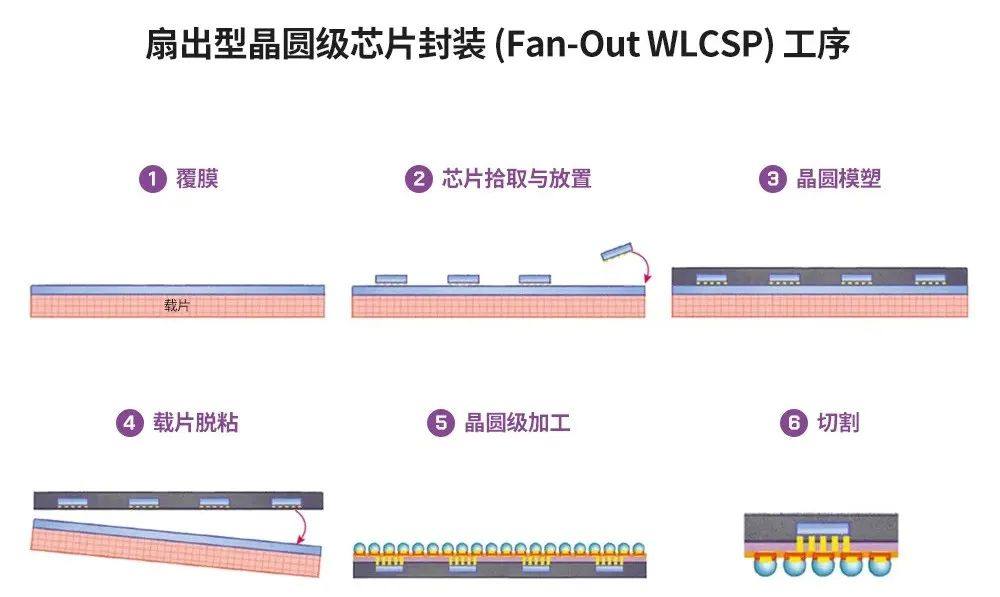

晶圆级封装

晶圆级封装是在切割晶圆成单个芯片之前,在整个晶圆上进行封装过程。晶圆级封装分为扇入型晶圆级芯片封装(Fan-In WLCSP)和扇出型晶圆级芯片封装(Fan-Out WLCSP),其特点是在整个封装过程中,晶圆始终保持完整。

-

系统级封装(SiP)

系统级封装(SiP)技术是通过将多个裸片(Die)及无源器件整合在单个封装体内的集成电路封装技术。在后摩尔时代,系统级封装(SiP)技术可以帮助芯片成品增加集成度、减小体积并降低功耗。

来源:长电科技

-

Chiplet

Chiplet是一种集成电路设计和封装方法,它将一个芯片(称为主芯片)与多个辅助芯片(称为chiplet)集成在一起,以形成一个功能完整的系统。Chiplet技术的出现是为了解决集成电路尺寸和复杂性不断增加所带来的挑战,提高系统集成度、性能和灵活性。

先进封装工艺

-

Bump(凸块)工艺

凸块制造技术(Bumping)是在芯片上制作凸块,通过在芯片表面制作金属凸块提供芯片电气互连的“点”接口,广泛应用于 FC、WLP、CSP、3D 等先进封装。Bumping 工艺介于产业链前道集成电路制造和后道封装测试之间,是先进封装的核心技术之一。

-

RDL(重布线层)工艺

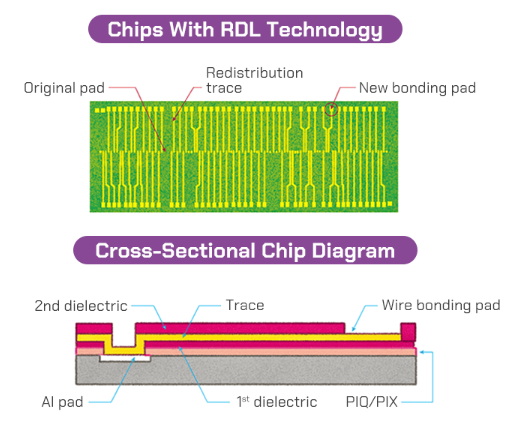

RDL是指重新布线的行为。该工艺的目的是通过添加额外的金属层来重新排列晶圆上已经形成的键合垫。RDL技术是一种晶圆级工艺,只重新配置焊盘,经过RDL的晶圆要经过传统的封装工艺来完成封装。下图显示了使用RDL技术将衬垫重新分配到边缘的中心衬垫芯片的示意图和横截面结构。

-

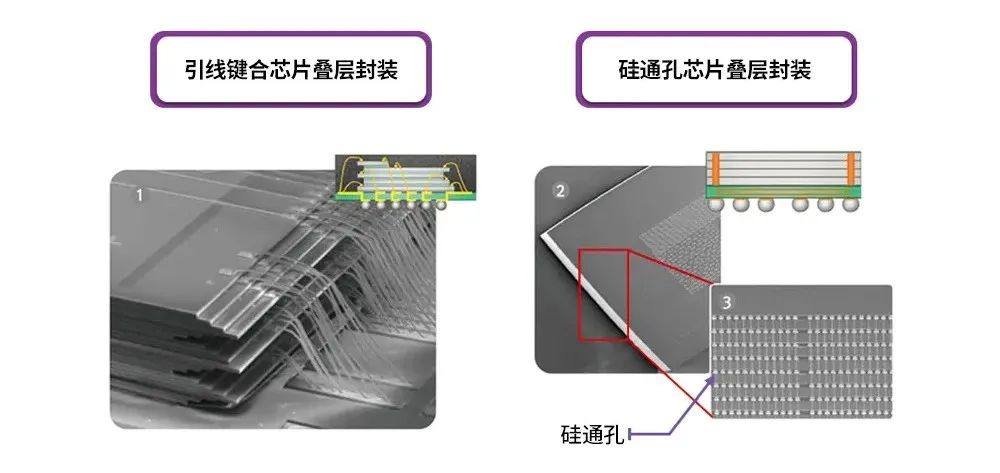

TSV(硅通孔)工艺

硅通孔是一种通过在硅片上钻孔来容纳电极的芯片堆叠技术。硅通孔封装的主要优势在于性能优越且封装尺寸较小。相比采用传统引线方法实现芯片与芯片互连或芯片与基板互连,硅通孔通过在芯片上钻孔并填充金属等导电材料来实现芯片垂直互连。

使用硅通孔技术的芯片剖面图(ⓒ HANOL出版社)

资料来源于网络公开资料,侵删

原文始发于微信公众号(艾邦半导体网):一文了解先进封装结构及工艺