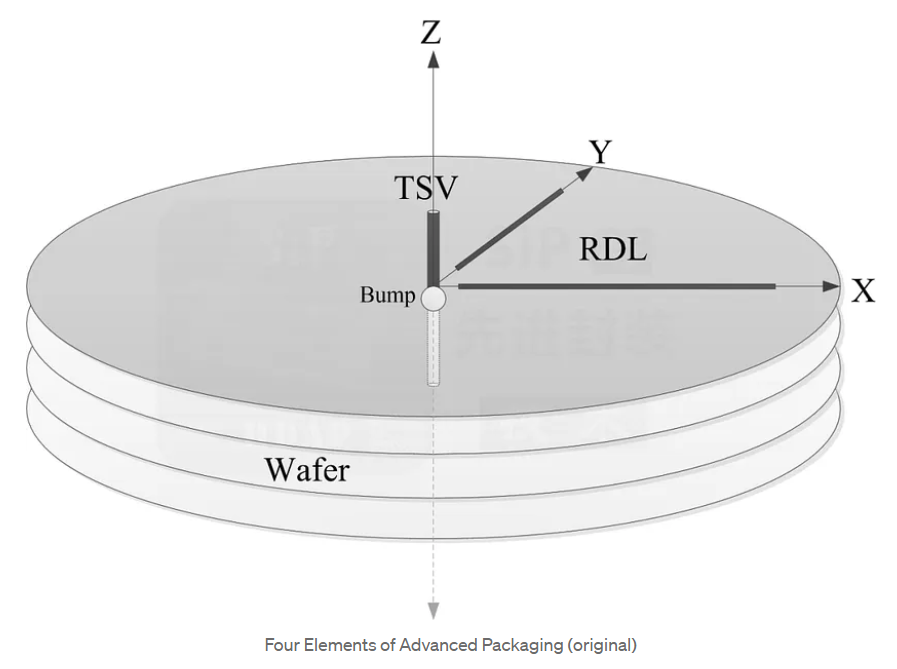

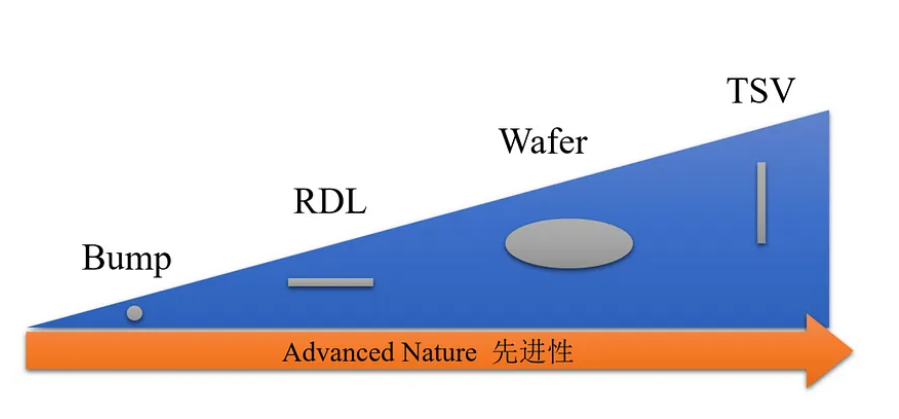

先进封装的四大要素——TSV(硅通孔)、Bump(凸点)、RDL(重布线层)、Wafer(晶圆)——在现代半导体封装中扮演了核心角色。它们在封装工艺中各自承担的功能,从不同维度推动了芯片小型化、集成度和性能的提升。

1. Wafer(晶圆):基础材料和封装载体

Wafer 是先进封装的基础,作为芯片制造的载体和平台。它由高纯度的硅材料制成,晶圆的质量和尺寸直接影响芯片的性能和良率。先进封装中,Wafer不仅是芯片制造的核心,也是未来异质集成和多芯片封装的基础。

技术作用:晶圆是所有半导体电路加工的基础,芯片的电路都是在晶圆上进行光刻、刻蚀和沉积等复杂工艺加工而成。

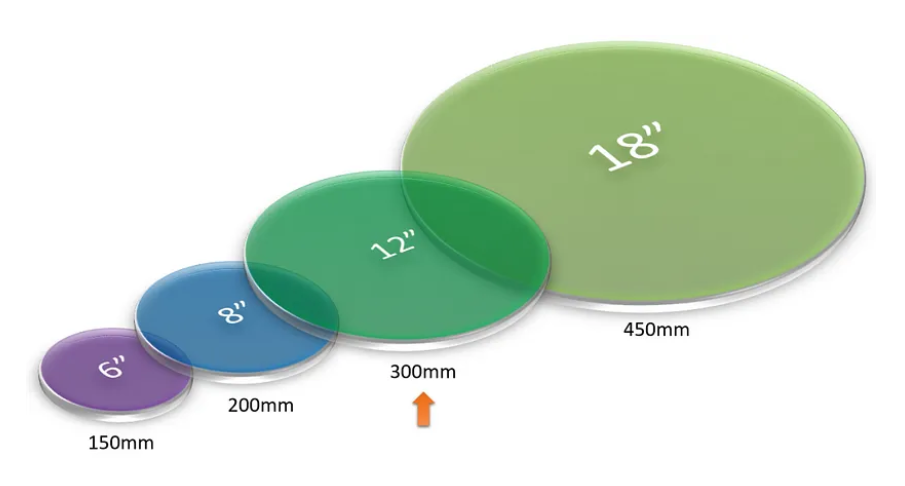

随着晶圆尺寸的增大(如从200mm到300mm),可以在单个晶圆上制造更多芯片,从而提升生产效率,降低成本。

晶圆的纯度和表面平整度对于芯片的性能至关重要,尤其是在先进制程(如3nm、2nm)下,对结构缺陷的控制要求极高。

为什么Wafer是四大要素之一:Wafer作为封装和集成电路的核心材料,是所有后续封装步骤的基础载体。没有高质量的晶圆,后续的TSV、Bump、RDL等技术也无法实现高效集成。

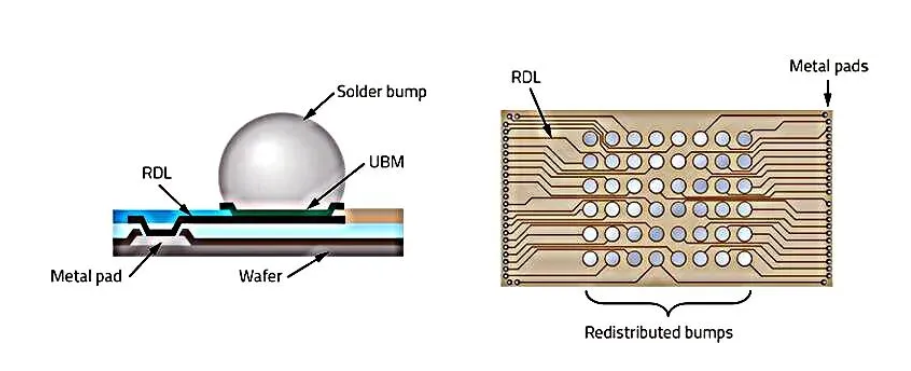

2. Bump(凸点):芯片与封装基板的电气和机械连接

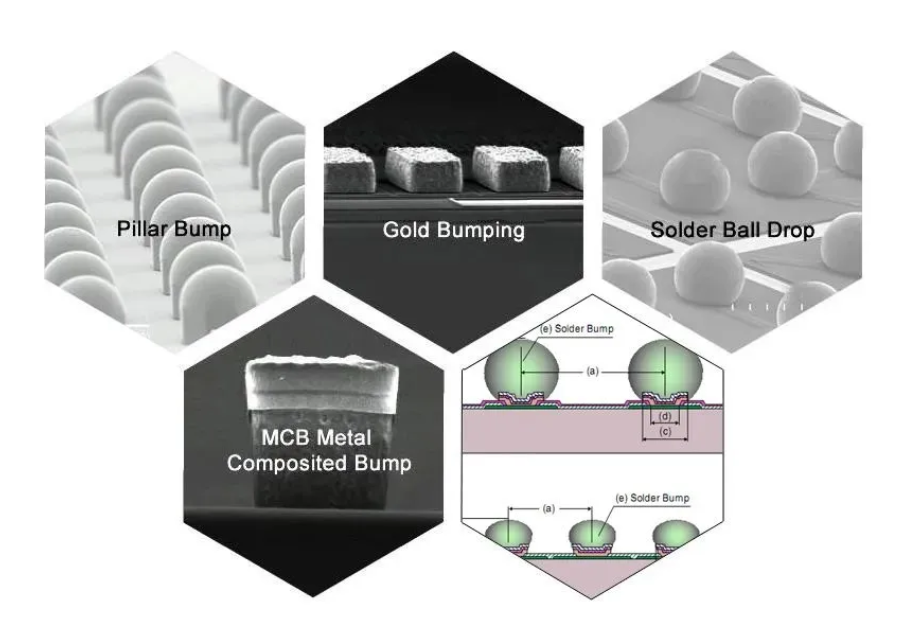

Bump 是实现芯片与封装基板之间连接的重要元素,类似于桥梁连接两者。通过Bump,电信号可以从芯片传输到封装基板,完成芯片与外部系统的通讯。

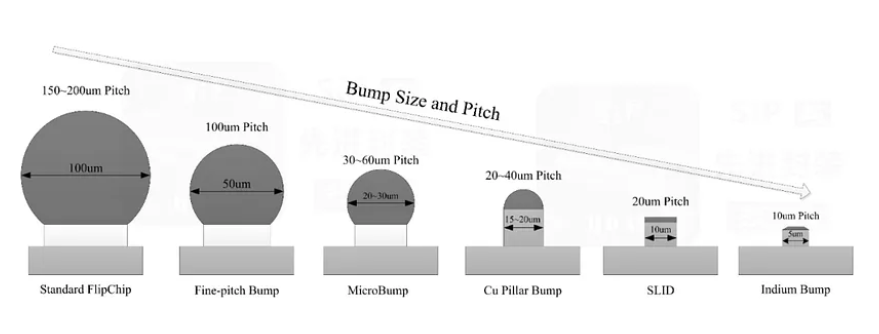

技术作用:Bump的尺寸和密度对芯片封装的整体性能起着重要作用,尤其是在微型化封装(如倒装芯片技术Flip-Chip)中,凸点的大小和排列会直接影响封装的可靠性和散热性能。

现代无铅材料如铜柱Bump替代了传统的锡铅合金凸点,不仅在环保方面更优,还具有更高的导电性和机械强度,适合高性能计算和移动设备。

为什么Bump是四大要素之一:Bump承担着实现芯片与部基板的可靠电气连接,并确保稳定的信号传输。它是实现芯片封装接口的核心技术,直接影响芯片的散热、导电性和机械强度。

3. RDL(Redistribution Layer,重布线层):重新分配电气信号

RDL是用于在芯片封装中重新分配电信号的金属层,类似于一座城市中的道路网络。它通过改变芯片上引脚的布局,实现更高密度的信号连接,从而在有限空间内提高封装性能。

技术作用:RDL能够扩展和重新分配信号路径,将芯片上的输入/输出引脚(I/O)从密集区域重新布线至较大区域,避免传统封装中引脚密度不足的问题。

现代封装中,RDL层的设计已经从单层发展为多层结构,以应对复杂信号和高密度集成的需求。尤其是在Fan-Out(扇出型)封装和WLP(晶圆级封装)中,RDL的精细化布线技术成为核心。

为什么RDL是四大要素之一:RDL通过重新布线,有效提升了芯片的I/O密度和信号传输效率,能够支持多层电路互连以及先进封装中的异质集成。这使其成为封装高性能化和小型化不可或缺的技术。

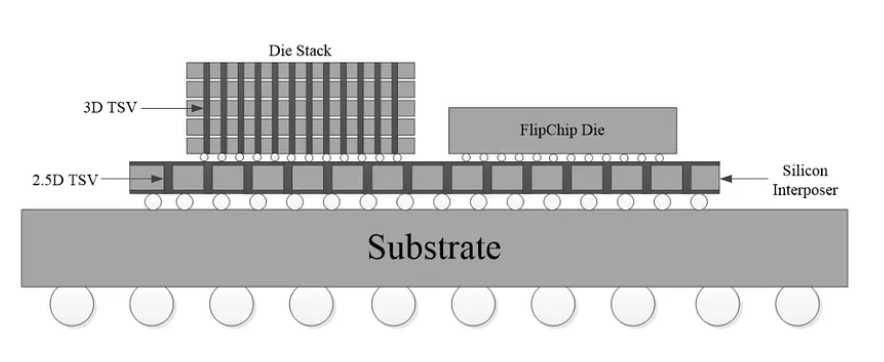

4. TSV(Through-Silicon Via,硅通孔):实现垂直方向的电气互连

TSV 是一种在硅片中开孔,允许电信号在芯片的不同层之间垂直传输的技术,主要用于3D集成电路和2.5D封装。

技术作用:通过TSV技术,芯片可以通过垂直方向的电气互连,实现多层芯片堆叠,显著提高了芯片的互连密度和集成度,降低了信号延迟和功耗。

2.5D TSV通过转接板(interposer)将多个芯片集成在一起,而3D TSV则通过芯片直接垂直堆叠,实现更高的集成度和效率。

为什么TSV是四大要素之一:TSV为垂直方向上的芯片互连提供了有效解决方案,特别是在3D封装中,TSV可以大大缩短信号传输距离,提升芯片集成度,适应了高性能计算和AI芯片对高效能的需求。

小结一下:Wafer、Bump、RDL和TSV是先进封装中的四大关键技术要素,它们分别从材料基础、连接、信号分配和垂直互连四个角度,解决了高性能封装中的不同问题。Wafer是芯片封装的载体,Bump连接芯片与外部基板,RDL优化了信号布线,TSV则实现了垂直互连。它们共同推动了半导体封装技术向更小尺寸、更高密度和更高性能的方向发展。

原文始发于微信公众号(老虎说芯):一文读懂先进封装的四大要素?TSV、Bump、RDL、wafer