摘要:在最近的半导体封装中,采用硅通孔 (TSV) 技术已成为集成 2.5 和 3D Si芯片以及中介层的关键。TSV 具有显著的优势,包括高互连密度、缩短信号路径和提高电气性能。然而,TSV 实施也存在电气损耗、基板翘曲和高制造成本等挑战。相比之下,基于玻璃的玻璃通孔 (TGV) 具有良好的特性,例如出色的绝缘性能、成本效益和可变的热膨胀系数 (CTE) 值,可减轻堆叠器件的翘曲。此外,它们还有助于小型化并支持高频应用。本文概述了半导体封装发展中玻璃基板、TGV 钻孔技术、功能层沉积和铜填充工艺的最新进展。在阅读本文之前,欢迎识别二维码申请加入玻璃基板TGV产业链微信群。

1 简介

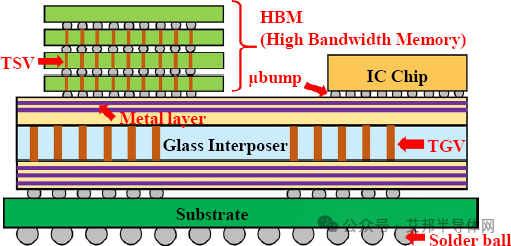

随着移动设备和物联网 (IoT) 的发展,人们正在开展三维 (3D) 封装技术的研究,以实现更小更薄的封装尺寸和更高的电气可靠性。尽管半导体传统上采用硅基板,但为了满足移动电子设备和物联网等先进电子元件的要求,对玻璃基板的需求也在增加。2022 年玻璃通孔 (TGV) 基板的市场规模估计为 6000 万美元,预计到 2029 年将达到 4.805 亿美元,2023 年至 2029 年预测期内的复合年增长率为 34.2% 。玻璃具有低介电常数、低电损耗和可变的热膨胀系数 (CTE),被认为是射频通信和中介层应用的合适材料,需要形成精确的 TGV 来实现芯片之间的电连接。图 1显示了以玻璃和 TGV 作为中介层的 2.5D 半导体封装应用的示例。

图1 适用于 2.5D 半导体封装的玻璃中介层

与传统的引线键合相比,TGV 可实现更密集的互连,从而能够在有限的空间内放置更多的电信号。在玻璃基板上实施的 TGV 有助于抑制串扰和插入损耗等问题,这些问题在硅基 TSV 中很常见。玻璃出色的 RF 透明度使高频信号能够轻松通过 TGV 传输,从而实现高频下的低电气损耗和在无线通信和雷达应用中的高性能。此外,玻璃基板的刚性和绝缘性、低成本以及厚度约 100 ㎛ 的超薄柔性玻璃基板的好处在电子封装领域具有优势。而且,玻璃基板的热稳定性和机械稳定性可实现更密集的互连和可扩展性,从而提高半导体性能。

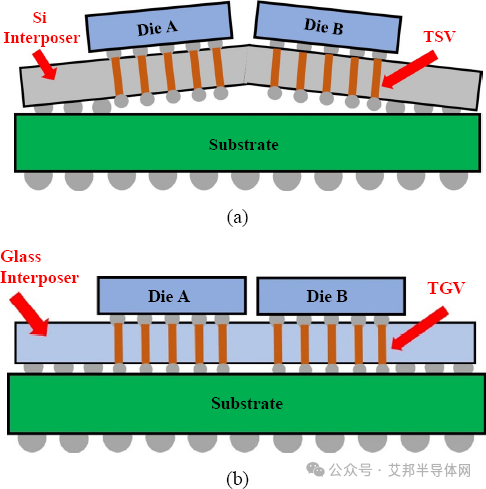

优化 CTE 对于实现可靠的 3D 封装至关重要。与硅不同,非晶玻璃具有可变的 CTE,这可最大限度地减少因与其他材料的 CTE 不匹配而导致的翘曲。图 2显示了 2.5D 封装中因 CTE 不匹配而导致的翘曲:(a) 显示硅中介层的翘曲,而 (b) 演示了如何调整 CTE 以最大限度地减少玻璃和基板之间的翘曲。

图2 使用不同中介层材料的 2.5D 封装,(a) 硅中介层,(b) 玻璃中介层

翘曲也是先进封装领域面临的一大难题,如具有高集成度和优异散热特性的扇出型晶圆级封装(FOWLP)。与传统封装相比,FOWLP 的厚度更薄,并且是在晶圆级进行加工,因此其翘曲程度远高于芯片级。玻璃材料可调节的CTE可最大程度地减少因基板变薄变大而引起的问题,在先进3D封装领域具有很高的适用性。另一方面,也需要解决与Si相比热导率较低、表面缺陷导致裂纹等难题。近日,随着英特尔在Semicon Japan展会上宣布以TGV及相关技术实现“先进半导体封装基板技术的下一代发展”,相关各类技术领域也都取得了重大进展。

本研究将探讨玻璃基板上半导体3D封装的高性能、可靠的TGV形成技术及相关研究。

2 TGV 形成技术

2.1 激光诱导选择性蚀刻(LISE)

LISE 是一种 TGV 形成技术,该技术使用激光局部蚀刻照射区域以形成图案。使用脉冲宽度极短(从飞秒到皮秒)的激光,可以在很短的时间内集中照射高能激光脉冲。在玻璃基板上形成 TGV 的过程中,激光在短时间内将高能量局部传送到玻璃表面。这会引起热机械效应,从而改变玻璃的表面膨胀和密度,从而产生对化学蚀刻敏感的区域。在这些区域用 KOH 等溶液进行化学蚀刻会形成纳米衍射光栅结构(称为纳米凹坑),从而改变玻璃的表面。通过调节激光照射的脉冲能量和化学蚀刻条件,可以控制纳米凹坑的大小,并获得所需的通孔形状。

利用LISE在熔融石英基底中制备纳米衍射光栅结构也有报道。Jia等人使用波长为1030nm的单脉冲飞秒激光以不同的脉冲间隔照射平行线图案,然后用85°C的KOH溶液进行5小时的选择性蚀刻。脉冲持续时间为290fs,脉冲重复频率为1MHz。SEM测量表明,在脉冲间隔为1μs和2μs时,由于热积累和扩散,没有发生选择性蚀刻,导致纳米结构分散。从3μs的脉冲间隔开始,热能扩散到周围环境,从而观察到规则且连通的纳米衍射光栅结构。然而,超过5,000μs的脉冲间隔后,虽然出现了纳米衍射光栅,但它们并不互连,从而阻止了蚀刻的进行。总之,据报道,纳米衍射光栅结构的产生和连接是飞秒激光选择性蚀刻过程中图案形成的主要机制。

Kim 等研究了超短脉冲激光持续时间和脉冲波形对硼硅酸盐玻璃中 TGV 形成速率的影响。实验中采用间隔为 213ps、10ns 和 500ms 的单脉冲和双脉冲。每个脉冲辐照 0.2至 1ps 后,使用 KOH 溶液,通过 OM 和 SEM 的横截面比较形成的 TGV。比较表明,随着脉冲持续时间从 0.2ps 增加到 1ps,TGV 的直径减小,深度增加,但只有间隔为 10ns 的双脉冲显示出一致的深度。这是因为不同的载流子相关现象主要取决于脉冲之间的时间间隔。在间隔为 213ps 的双脉冲中,由于电子接收能量,激活载流子处于激发态,此时会有额外的光子辐射,从而增加电子的动能,进而增加光子的穿透深度。然而,对于间隔为 10ns 的脉冲,电子会返回基态,并且会有额外的光子辐射,导致热扩散占主导地位。在这种情况下,热扩散的长度不会随脉冲持续时间而发生显著变化,因此 TGV 的深度保持一致。

脉冲宽度为1ps时,间隔为213ps的双脉冲形成的TGV孔最深,为22.39 ㎛,并观察到厚度为156±22 nm的纳米衍射光栅。综上所述,间隔为ps的双脉冲可以通过增强电子的动能来提高TGV的形成速率,证明了提高电子的动能比热扩散更有利于加工。

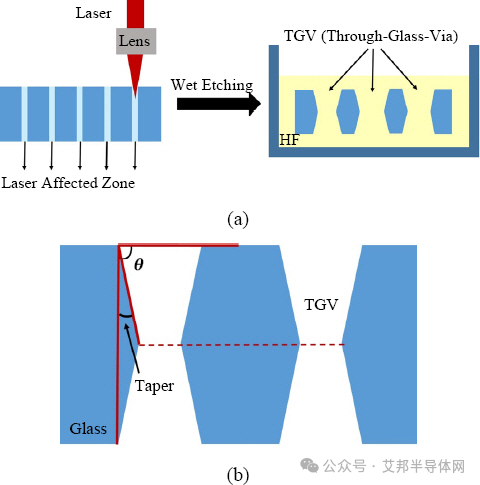

蚀刻液浓度也是影响TGV轮廓的主要因素,Chen等报道通过调整硼硅酸盐玻璃中HF蚀刻液的浓度可以改善TGV侧壁的锥度。实验所用的激光器为皮秒单脉冲激光器,脉冲能量为55μJ,脉冲宽度为16ps。用单脉冲激光束辐照的三个相同样品分别用10%、5%、3%浓度的HF溶液蚀刻,通过横截面测量TGV侧壁的角度。对于表面直径为60 ㎛的TGV,随着HF溶液浓度从10%降低到3%,通孔侧壁的角度从80.65°增大到84.18°,有效改善了TGV轮廓。同时,随着脉冲数从1增加到10,通孔侧壁的角度从80.65°增加到81.13°,但增加幅度很小。图3为实验中所采用的LISE技术的示意图及所形成的TGV的横截面。

图 3(a)LISE工艺示意图,(b)硼硅酸盐玻璃上TGV结构的横截面图

2.2 电火花加工法(EDM)

EDM 是一种利用放电的 TGV 形成技术,利用高电压和电流在玻璃基板上形成精确的结构。该技术涉及分两个步骤将玻璃保持在两个对齐的电极之间。首先,集中放电并产生热量,从而局部降低玻璃的粘度。其次,通过焦耳加热提取玻璃,形成一个孔。与传统的 TGV 形成方法相比,EDM 工艺可以在相对较短的时间内形成具有高纵横比的孔。EDM 仅使用放电,但也使用诸如 ECDM(电化学放电法)之类的方法,该方法通过添加电解质将放电与化学反应结合起来。

Harindra 等人使用 KOH 电解液的 ECDM 工艺在熔融石英基板上形成 TGV,并制作了 3D 电感器。由于硅基板上的电感器电阻率低,因此需要沉积绝缘层的工艺。另一方面,在玻璃基板上制作的电感器不需要绝缘层,简化了工艺,而且玻璃的透明光学特性使其更容易在生产过程中发现缺陷。实验在直径 2 英寸、厚度 520 ㎛ 的熔融石英基板上进行,使用 2x5 和 2x2 阵列的不锈钢多尖端形成孔。测得的 140±10 ㎛ 尺寸多尖端形成的 TGV 的平均顶部和底部直径分别为 580±71 ㎛ 和 286±45 ㎛。制作了螺旋电感和环形电感,测得的电感电阻分别为 338 mΩ 和 168 mΩ。这项研究证实了 TGV 工艺在 3D 电感制作中的适用性。图 4是在熔融石英基板上制作 3D 电感的工艺示意图。

已经开展了研究,利用添加剂或激光加工来改善由 EDM 和 ECDM 形成的 TGV 的特性。

Zhixiang 等通过在 KOH 电解液中添加非转移功能 (NTF) 电解液聚丙烯酰胺 (PAM)进行了一项研究,以提高 ECDM 形成的 TGV 的均匀性和重复性。NTF 电解液不具有高电传输特性,用于控制 ECDM 工艺中的电效应。与传统的 KOH 电解液不同,使用 NTF 电解液可以实现阻尼和限制效果。阻尼效果是指减少 ECDM 工艺中产生的振动。在 ECDM 加工过程中,由于电解液和电极之间的放电,玻璃表面会产生微振动,从而对精密加工产生负面影响。限制效应是指限制 ECDM 加工过程中发生放电的区域,从而实现精密加工。通过限制效应使放电集中在特定区域,可以形成精确的 TGV。实验中,将浓度为 0.1 wt% 至 0.9 wt% 的 NTF 电解液添加到 KOH 电解液中,并在钠钙玻璃基板上进行 ECDM 加工。结果表明,使用 0.5 wt% NTF 电解液制成的 81 个微孔阵列的过切标准偏差为 3.34 ㎛,与仅使用 KOH 电解液的标准偏差 9.79 ㎛ 相比有显著改善。TGV 形成过程中产生的热影响区 (HAZ) 宽度也减少了 64.81%,证明了 NTF 电解液在 ECDM 工艺中的有效性。

Harmesh 等人进行了研究,以使用添加碳纳米管 (CNT) 的电极来提高 EDM 的性能。在实验中,在主要由碳和铬组成的钢基体上使用纳米粉末形式的 CNT,并且在 EDM 过程中将 CNT 颗粒与电介质混合,产生火花并有助于提高工件的侵蚀速率。火花均匀分布在 CNT 颗粒之间,提高了工件的材料去除率 (MRR) 和表面粗糙度 (SR)。结果表明,与传统 EDM 相比,添加 4g CNT 的 EDM 工艺的 MRR 高 80%,SR 低 67%。总之,添加的 CNT 的浓度是显著影响 EDM 工艺中 MRR 和 SR 的关键参数。

Zhao 等对激光辅助 (LA) ECDM 进行了研究,该技术将激光加工与 ECDM 相结合。实验中,采用波长为 1064 nm、脉冲持续时间为 12 ps 的 Nd:YVO 4激光器,激光辐照后在 NaOH 电解液中进行 ECDM。结果表明,由于限制效应,激光辐照后进行的 ECDM 加工精度有所提高。此外,仅用激光加工的孔呈 V 形,锥度较大。在 LA-ECDM 中,孔的轮廓从 V 形转变为 U 形,锥度明显改善。

通过电化学放电加工形成TGV具有在短时间内制造大量TGV的优点,但加工过程中产生的热量引起的电极磨损会对TGV轮廓产生负面影响。电极磨损直接影响加工精度和形成的TGV的可靠性,由于EDM加工成本的约70%归因于电极更换,因此减少磨损至关重要。

Jafferson 等进行了通过低温冷却减少电极磨损的实验。实验中,以-185°C 的液氮作为低温冷却材料,以铜和钨为电极材料,以 1 mm 厚的不锈钢为基体。结果表明,钨电极的工具磨损率 (TWR) 降低了 58%,铜电极降低了 35%,表明低温冷却显著降低了工具磨损。此外,对经过低温处理的电极进行维氏硬度测试表明,钨电极的硬度增加了 120%,铜电极的硬度增加了 17%,证明了低温冷却的有效性。

3. 功能薄膜形成及TGV中的Cu填充

3.1 TGV内壁功能薄膜涂覆

功能薄膜是薄薄的沉积或涂层薄膜,旨在提供特定的物理、化学或电气特性。这些薄膜具有各种功能,并用于众多技术领域。每种功能薄膜都是根据其应用领域的要求设计的,在 TGV 制造过程中起着至关重要的作用。

薄膜的用途包括(1)种子层:用作填充金属(如Cu和Au)的平滑电镀涂层,(2)绝缘层:用于电隔离TGV并防止相邻TGV之间的电流泄漏和干扰,以及(3)粘附层:用于加强种子层和绝缘层之间的结合。

在玻璃基板上形成薄膜时,包括溅射在内的干法很常见,但在高纵横比 TGV 中实现均匀的膜厚存在挑战。相比之下,湿法涉及将玻璃基板浸入溶液中形成薄膜,可在 TGV 和玻璃表面上均匀一致地形成薄膜。如果种子层未在 TGV 内壁上正确形成,则随后可能会出现诸如 Cu 填充不完整等缺陷。

Chen 等人使用 Ni 活化和化学镀 Ni-P 在 TGV 中形成金属种子层。实验使用由 Li-Al-Si 组成的光反应性玻璃;Ni-P 镀层中的化学反应如下(等式 1、2)。

Ni-P镀层试件在200~450℃空气中退火30min,150℃以下升温速率为120℃/h,150℃以上升温速率为60℃/h。结果表明,350℃以上退火后,镀层结合力明显提高,400℃以上形成氧化膜,使电阻增大。另据研究报告,Ni-P种子层在热处理后结晶,显示Ni和Ni3P相。Ni-P相以非晶态为主,退火后出现类似树枝状结晶,提高了与TGV的结合力。因此,镍种子层可以有效涂覆长宽比为10:1的通孔,平均层厚度约为200nm,通孔内部表现出均匀的电镀特性。

Inoue 等采用湿镀法,即先化学镀一层 Cu 薄膜,然后再进行电镀,在玻璃基板上形成 Cu 种子层。结果表明,在 Na 玻璃基板上,Cu 的附着强度为 0.6 kN/m,在无碱玻璃基板上,Cu 的附着强度约为 0.4 kN/m。

Takayama 等提出了一种将低真空高速溅射与电镀相结合在无碱玻璃基片中TGV内部形成Cu种子层的方法。高速溅射时,膜压为0.5-5 Pa,功率为35 kW,溅射时间为28 秒,在TGV基片平坦部分形成3㎛ Cu膜,在TGV中心形成0.29㎛ Cu膜,长宽比为3.75(通孔直径80㎛,深度300㎛)。溅射后采用硫酸和焦磷酸镀液进行电镀,焦磷酸对Cu的附着强度超过1.0 kN/m。

Yiu 等人通过施加溶液基金属氧化物的粘附促进层 (APL),在熔融石英衬底上实现了高纵横比 TGV 填充。APL 通过旋涂沉积在 TGV 的侧壁上,然后进行 Cu 层的化学镀和使用直流电流的电镀。结果表明形成了没有空隙的 HAR-TGV,其长度为 345 ㎛,直径为 25㎛。APL 层可以通过浸涂和旋涂等多种方法沉积,并且在直流波形而不是复杂的 PPR 波形下实现 HAR-TGV 凸显了其重要性。

同时,Shigeo 等人提出了一种湿镀工艺,该工艺可以在玻璃上直接形成铜膜,而无需在铜和玻璃之间添加粘附层。首先,对无碱玻璃基板进行超声波清洗、碱性脱脂和紫外线照射,以去除玻璃表面的有机材料并增强粘附性。通过湿镀工艺镀上3 ㎛ 铜层作为种子层,然后通过电镀和SAP(半加成工艺)在TGV的侧面、正面和背面涂覆15 ㎛厚的铜。结果表明,湿镀铜种子层和电镀铜均镀层均匀,实现了0.35 kN/m的高粘附强度和玻璃优异的表面平整度。测得的TGV 电阻低于平均值6.71 mΩ /via。TGV镀膜湿镀可应用于大型玻璃基板,且无需额外的功能性薄膜镀膜即可进行工艺,具有廉价、高效的优点。

Hariki 等人还提出了一种薄膜附着和封闭电镀方法,以在 TGV 中填充 Cu,而无需在内部形成种子层,并报告了在通孔内部成功填充 Cu。

3.2 TGV 和 TSV 填充镀铜

TGV、TSV的Cu填充主要采用电镀法。电镀是通过电流将金属离子移动到阴极,在特定表面镀上目标金属的方法。在Cu电镀过程中,电流通过含有Cu离子的镀液,Cu离子移动到阴极,在阴极获得电子并被还原为铜。还原后的Cu离子沉积在TSV、TGV表面,形成镀层。

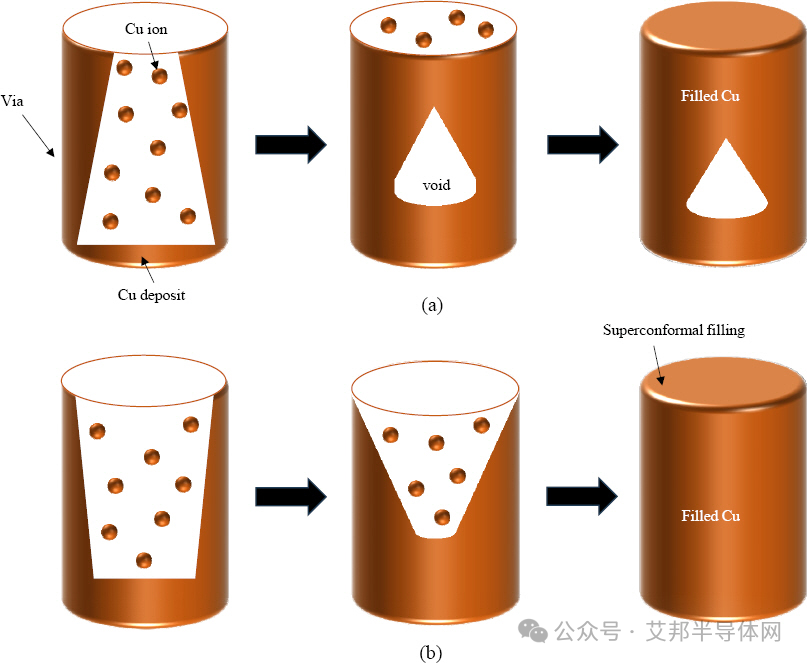

TGV 和 TSV 内部通过电镀形成的金属层受施加的电流密度和波形影响。在 DC(直流)Cu 填充中,通孔开口处的电流密度较高,导致顶部镀层比底部厚,使通孔开口首先与 Cu 连接,使其容易在通孔内部出现空洞和接缝等缺陷。可以通过施加脉冲电流、使用添加剂优化电镀溶液以及使用超声波来改善此类缺陷。

用于优化电镀液的添加剂包括抑制剂、促进剂和整平剂。抑制剂和促进剂控制电镀过程中金属沉积的速度,而整平剂则诱导均匀的金属沉积,从而提高电镀质量。

关于添加剂,Ling 等研究了抑制剂和促进剂对 TGV 中 Cu 填充的协同作用。在实验中,使用深度为 150 ㎛ 的锥形通孔,顶部直径为 50 ㎛,底部直径为 20 ㎛。所用电镀液为 99.7 g/L CuSO₄、10 g/L H₂SO₄和 50 ppm Cl⁻,添加新型抑制剂 A、促进剂 B 和整平剂 C,沉积电流密度为 0.5 ASD(安培每平方分米)、1 ASD 和 1.5 ASD。在第一个实验中,抑制剂、促进剂和整平剂的比例为 50:1:1.25,在 1 ASD 下 2.25 小时内通孔完美填充,无空洞。在抑制剂浓度较低时,抑制剂和加速剂的协同作用导致通孔表面厚度增加,从而增大了通孔顶部和底部之间的表面厚度差异。然而,随着抑制剂浓度的增加,抑制剂 A 分子优先吸附在通孔表面,从而减慢了沉积速率。结果,通孔表面厚度减小,顶部和底部的表面镀层始终保持不变。因此,在抑制剂、加速剂和整平剂比例为 60:1:1 的情况下,在 1.5 ASD 的较高电流密度下,通孔在 1.5 小时内完美填充,没有空洞。

Jin 等研究了 TGV 填铜过程中用作整平剂的 PVP (聚乙烯吡咯烷酮) 的分子量对 Cu 表面抑制层形成的影响。实验采用含有 0.94 M CuSO₄、0.31 M H₂SO₄、2 mM HCl 的水系电解液,其中抑制剂为 PEG (聚乙二醇)、促进剂为双(3-磺丙基)二硫化物 (SPS),整平剂 PVP 的分子量分别为 10,000、29,000、360,000 和 1,300,000 g/mol。实验中使用的 TGV 高度为 400 μm,为锥形结构,开口直径为 80 μm,中点直径为 40 μm。结果表明,分子量较小的PVP(10,000 g/mol)在Cu表面形成了更致密的抑制层,有效地抑制了Cu电极的电镀并实现了无缺陷填充。相反,分子量较大的PVP(360,000 g/mol)层致密性较差,含有许多可容纳促进剂的缺陷。这表明吸附的PVP分子之间的空间位阻随分子量的增加而增大,阻碍了随着分子量的增加在Cu表面形成致密的抑制层。研究发现聚合物添加剂的分子量会影响吸附物的结构和竞争吸附,这凸显了选择合适的聚合物添加剂对增强Cu填充过程性能的重要性。

在稳定的直流电流波形下,通过添加剂优化电镀液对防止缺陷有很好的效果。然而,由于直流电流的性质,当施加大电流时,由于通孔位置的电流密度差异,完全防止空洞的产生具有挑战性。为了解决这个问题,目前正在使用采用PPR(周期性脉冲反向)波形的电镀方法。PPR波形由脉冲电流、反向脉冲电流和关闭脉冲周期组成,通过重复脉冲和反向脉冲电流与关闭脉冲,实现通孔的超共形填充。在脉冲电流周期内,Cu镀在通孔内,在反向脉冲周期内,过镀的Cu层溶解回来。在关闭脉冲期间,铜离子扩散回电镀液中,平衡通孔内的离子浓度,防止表面优先镀铜。

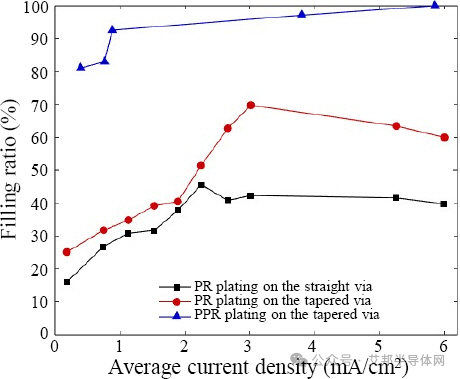

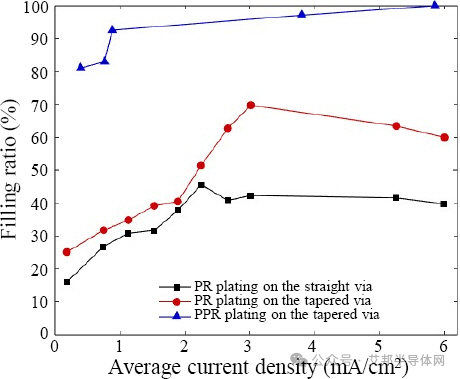

激光加工的 TGV 通常具有锥形通孔结构,根据激光钻孔方法的不同,通孔的一侧或两侧可以具有斜坡。研究人员使用 PR 和 PPR电流研究了直通孔和锥形 Si 通孔中 Cu 的填充程度。在相同的 PR 电流条件下,电流密度为 2.29 mA/cm² 时,直通孔的填充率最高为 45%,而电流密度为 3.04 mA/cm² 时,锥形通孔的最大填充率为 71%,这表明锥形通孔的填充率高于直通孔。

在 PPR 电流波形中,锥形通孔在平均电流密度为 5.85 mA/cm² 时显示出 100% 的 Cu 填充率,总体而言,PPR 波形的填充率高于 PR。图 5是根据 PR 和 PPR 波形中的电流密度表示垂直和锥形通孔的 Cu 填充率。

图 5 根据 PR 和 PPR 电流密度计算的直通孔和锥形通孔的 Cu 填充率(电镀时间:1小时)

关于使用 PPR 波形进行电镀,研究人员进行了一项分阶段 PPR 研究,使用三种电流密度水平来改善处理时间。在初始阶段,采用低电流密度对通孔的入口、壁和底部进行保形电镀。在中间阶段,采用中等电流密度对通孔内部进行超保形电镀,最后采用高电流密度将通孔完全填充为铜。因此,最后阶段补偿了初始阶段和中间阶段在低电流密度下所花费的时间,实现了缺陷最小化的铜电镀。这些结果证明了优化电流波形对于快速可靠地填充铜的重要性。

在TSV的Cu填充中,采用不添加任何添加剂的PPR电流波形实现了无空洞填充。Zhu等的实验中,对直径 50㎛ 的TSV施加 0.4 A/dm² 的脉冲电流和 -0.8 A/dm² 的反向脉冲电流,可得到V型铜层生长并实现无空洞超共形电镀。根据电流波形比较结果可知,以与脉冲电流相同的 0.4 A/dm² 进行的直流电镀内部存在较大的空洞。反向脉冲有助于Cu的溶解,有助于铜层的V型生长,而负脉冲延长了铜离子的扩散时间,使通孔内的离子浓度保持平衡。然而,在使用PPR电镀Cu时,电流密度的增加会导致通孔底部形成倒V型结构,从而产生空洞。图 6是在 (a) 高电流密度和 (b) 低电流密度下使用 PPR 进行 Cu 填充的示意图。随着电流密度的降低,通孔顶部形成的直接 V 结构增加,并且在低电流密度下,直接 V 结构优于倒 V 结构,从而实现无空洞填充。

图 6采用 PPR 电流的 Cu 填充过程示意图,(a) 高电流密度,(b) 低电流密度

Inoue 等人通过化学镀 Cu 薄膜形成和镀 Cu 证实了 8 英寸无碱玻璃晶片上的 TGV 中 Cu 的均匀填充。

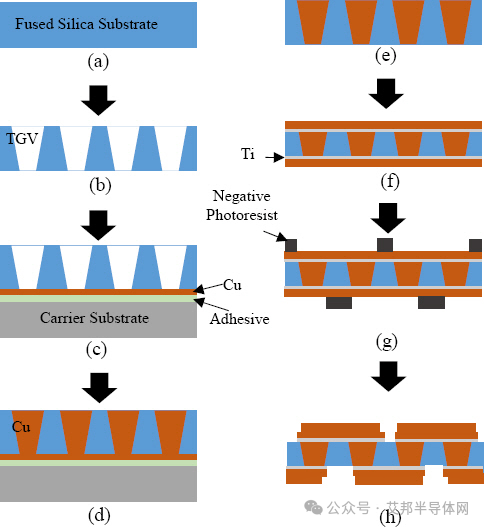

前人研究多为自下而上的分段电镀方式,Cu从底部向顶部积累,而Ke等研究了一种双面电镀工艺。双面电镀是一种同时对靶材两面进行电镀的方法,适用于需要在基材两面进行电镀的情况。实验中以Ti作为扩散阻挡层,Cu作为种子层,通过调节电流密度、添加剂、镀液等参数实现均匀无空洞的TGV填充。双面电镀工艺存在镀液流速不均、基材两面存在差异等问题,需要在电镀的各个阶段调整电流和参数。但与分段电镀相比,双面电镀有填充时间更快、适用于两面图案不同的基材等优势。

4. 结论

由于采用 TSV 技术集成 2.5D 和 3D 硅芯片和中介层,高密度、高性能半导体封装领域取得了重大进展。虽然 TSV 具有增加互连密度和缩短信号路径等优势,但人们仍在努力克服其缺点,包括电气损耗、基板翘曲和高制造成本。作为解决 TSV 技术缺点的替代方案,基于玻璃的 TGV 在绝缘性能、成本效益和高频域适用性方面具有优势。此外,由于其可变的 CTE 值,它们可以有效缓解堆叠设备(例如 2.5D 和 3D 结构)中的翘曲。因此,它作为下一代半导体封装技术备受关注,目前正在进行大量研究。由于玻璃基板、TGV 钻孔技术、功能层涂层和 Cu 填充工艺的不断进步,该技术有望提高半导体封装领域的性能、可靠性和成本效率。

来源:Joumal of Welding and Joining

作者:Beom Chang Seok, Jae Pil Jung

首尔大学材料科学与工程系,首尔,02504,韩国

我们诚邀您加入“玻璃基板与TGV技术交流群”,与行业精英共同探讨玻璃基板及TGV技术的前沿动态,共享资源,交流经验。在这里,您可以第一时间获取技术革新信息,深入解析行业趋势,与行业领袖面对面交流,共同推动技术革新,探索无限商机。

活动推荐:

主要议题(包含但不限于):

| 1.玻璃基板封装技术的最新进展与未来展望 |

| 2.TGV 玻璃关键技术面临的挑战及其解决策略 |

| 3.玻璃衬底材料与先进封装 |

| 4.玻璃衬底材料的本构模型、破坏机理及其在工程中的应用 |

| 5.先进封装产业升级中玻璃基互连技术的作用 |

| 6.玻璃基板生产的可靠性探讨 |

| 7.最新一代 TGV 玻璃通孔技术助力先进封装 |

| 8.激光系统在 TGV 中应用及发展 |

| 9.PLASMA 技术在 TGV 加工中应用 |

| 10.面板级玻璃基板的激光诱导蚀刻 & AOI |

| 11.飞秒激光助力先进封装玻璃基板发展 |

| 12.显微镜在半导体先进封装缺陷检测中的应用 |

| 13.TGV 填孔电镀配方及工艺 |

| 14.印刷铜浆与电镀铜优劣分析 |

| 15.PVD 技术在玻璃基板先进封装制程应用 |

| 16.在玻璃基板上开发湿化学铜金属化工艺 |

| 17.异构封装中金属化互联面临的挑战 |

| 18.高效RDL制造技术:赋能多种互联结构的面板级封装 |

| 19.TGV金属线路制作的工艺难点及技术解决路径 |

| 20.玻璃基板介电层材料研究 |

报名方式一:加微信

李小姐:18124643204(同微信)

邮箱:lirongrong@aibang.com

扫码添加微信,咨询展会详情

注意:每位参会者均需要提供信息

或者复制网址到浏览器后,微信注册报名

https://www.aibang360.com/m/100235?ref=100042

原文始发于微信公众号(艾邦半导体网):高性能半导体封装TGV技术最新进展