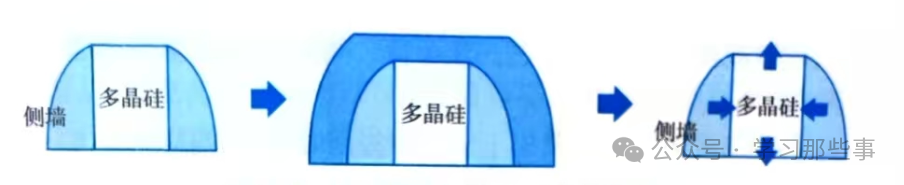

(1)应力记忆技术(SMT),作为一种在CMOS工艺中应用的应力调控手段,具有独特的工艺流程。该流程首要步骤是构建包含伪多晶硅材料的栅极构造。在侧墙形成之后,通过沉积工艺在结构上添加氧化硅和氮化硅层。紧接着,对氮化硅层实施退火处理,此过程中,氮化硅、栅极、沟道以及侧墙之间会产生热应力和内应力效应。这些应力会被“记忆”在栅极的伪多晶硅和沟道区域中(因此得名应力记忆技术)。注意即便在后续的工艺中移除了氮化硅层,NMOS沟道方向仍会维持一定的张应力状态,进而影响NMOS器件的载流子迁移特性(见图1)。其背后的机制在于硅氮化物的覆盖层能为NMOS器件引入单轴拉伸应力。为了优化器件性能和降低功耗,可以选择快速热退火(RTA)工艺或采用能显著改变应力的材料。应力记忆效应会导致多晶硅在特定方向上受到拉伸,而在另一方向上受到压缩。这些应力会进一步传递到沟道中,转化为沟道内特定方向上的压缩应力和拉伸应力,其中拉伸应力有助于提升NMOS器件的性能。对于多晶硅的离子注入过程,若保持剂量不变,投影射程的增加会增强应力记忆效应,因此需要考虑应力传递的量级。然而,在28nm及以下节点的CMOS器件制造中,NMOS区域的应力记忆效应往往难以达到预期效果,这主要是由于应力层厚度较薄、应力层与沟道的间距较大以及需要去除伪多晶硅等因素所致。因此,技术人员需针对前两项因素寻求解决方案,以克服这些挑战。

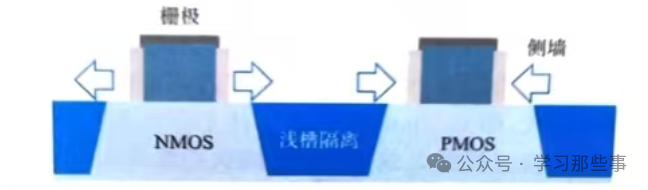

图1:应力记忆技术应力转移示意图

相比之下,选择性SMT技术通过有选择地去除或保留不同器件上的氮化硅,来优化器件性能。例如,去除PMOS上的氮化硅而保留NMOS上的氮化硅,可以显著提升NMOS的电子迁移率,使其电流驱动能力提高约15%,而对PMOS的性能无显著影响。

当前,SMT的主流技术是在侧墙与自对准硅化物之间插入特定工艺层。在完成源、漏极离子注入后,采用高应力水平的膜层(如高应力氮化硅)作为保护层,并对多晶硅栅极进行高温退火处理。

SMT工艺常见有两种实施方式。第一种方式是在侧墙形成后,对源、漏极进行非晶化离子注入,随后生长一层薄二氧化硅作为缓冲,再在整个晶片上沉积一层高应力氮化硅。接着,通过光刻和干法刻蚀去除PMOS区域的氮化硅,并用酸液清洗掉暴露的二氧化硅。之后进行高温退火处理(常用快速高温退火技术,甚至可达毫秒级),此过程可分为一次退火和二次退火。最后,使用磷酸去除剩余的氮化硅。第二种方式与第一种类似,但区别在于不进行光刻和干法刻蚀先行去除部分区域,而是统一在退火后去除氮化硅,这对氮化硅薄膜的工艺要求更为严格。为了减轻SMT对PMOS的负面影响,可以在氮化硅沉积后采用紫外线照射,以降低薄膜中的氢含量,从而减少硼离子的损失。

氮化硅的低温相具备特定的点阵常数,其中a轴长度为0.758纳米,c轴长度为0.5623纳米。其介电常数较高,范围在6至7之间,且击穿场强可达1×107伏特每厘米,适合通过化学气相沉积或溅射法进行制备。在沉积氮化硅时,NH₃和N₂常作为反应气体,反应速率相对较快。生成的氮化硅薄膜中往往含有一定量的氢原子,这些氢原子对薄膜的致密度、折射率以及应力水平有着显著影响。为了满足器件特性的需求,工程师们通过调整工艺参数(如反应温度、气体流量、射频电源的频率与功率、以及反应气压)来控制氢原子的含量,从而制备出性能理想的氮化硅薄膜。此外,在SMT工艺中,还需考虑源/漏退火工艺以及应力顶盖层(ACL)底部的多晶硅栅极再结晶过程,这一过程诱发的应力会被“记忆”在MOS器件中,进而使MOS器件的电性能提升约10%。针对PMOS与NMOS晶体管对应力需求的不同,还可以在MOS器件上实施选择性的局部应变,以进一步提升其电性能。

(2)硅储源/漏应力技术的诞生,旨在解决SMT工艺主要改善NMOS性能而对PMOS性能提升不明显的问题。在高电场环境下,载流子散射现象加剧,导致迁移率下降,同时氧化层界面散射也会变得更加严重,进一步降低了载流子迁移率。为了克服这一问题,可以在沟道内引入薄层的锗(Ge)材料,以提升载流子迁移率,从而改善器件性能。

Intel公司于2003年针对90纳米及以下工艺节点,引入了硅锗源/漏应力技术。该技术通过在硅片上外延生长硅锗材料,直接对沟道施加压应力,从而显著提升了PMOS的性能,特别是电流驱动能力,增幅可达25%。其背后的原理在于利用锗(晶格常数5.65埃)与硅(晶格常数5.43埃)晶格常数之间的差异,在源漏区域产生压应力,进而增强了PMOS中空穴的迁移率和饱和电流。与传统的硅源/漏应力技术相比,硅锗源/漏技术不仅能够引入单向压应力,还能带来更大的能隙和更高的硼活化效率,从而有效降低了扩展电阻。此外,硅锗源/漏技术还促进了双沟道整合的实现,尤其适用于高介电常数栅极优先(gate-first)技术,其中高介电常数介质具备较高的等效氧化层厚度(EOT)。然而,该技术也存在工艺复杂度高、硅帽层厚度影响性能等缺点。

在硅锗源/漏应力技术中,应力的施加和对短沟道效应的控制高度依赖于工艺参数的精确控制,包括硅/硅锗界面的预清洗、硅锗块体的外延生长、外延生长的深度、厚度和形状,以及硅储层中锗的含量。同时,在处理过程中还需考虑层的弛豫现象,以及硅锗源/漏与沟道之间的距离对应力水平的影响。此外,嵌入式锗化硅(eSiGe)的边缘效应(即栅极长度的依赖性)和尺寸缩减也会对器件性能产生影响。eSiGe的成品率不足、仅对PMOS性能有提升效果,以及与先进栅极沉积技术(如高k栅介质/金属栅极,HK/MG)的兼容性问题,都是工程师们需要后续关注和改进的方向。

由于硅锗材料直接对沟道施加应力,因此硅锗源/漏的轮廓设计会直接影响引入沟道的应力水平。不同形状和位置的硅锗源/漏对应力的改善效果也各不相同。通常,硅锗与沟道的距离越近,对沟道产生的压应力就越显著。为了优化应力效果,研究者们一直在不断改进硅锗源/漏的形状设计。例如,Σ形状的SiGe源/漏表现出显著的应力效应,但需要使用特殊工艺来实现,包括反应离子刻蚀、离子注入非晶化处理,以及沿硅晶体(111)方向进行高选择性的湿刻等步骤。对于更小尺寸的器件,则采用了双台阶形状的硅锗源/漏设计,通过在不同位置形成不同深度的台阶,以实现更精确的应力控制。采用这种技术,PMOS的驱动电流得到了100%的改善。

图2:Σ形的SiGe源/漏形成过程

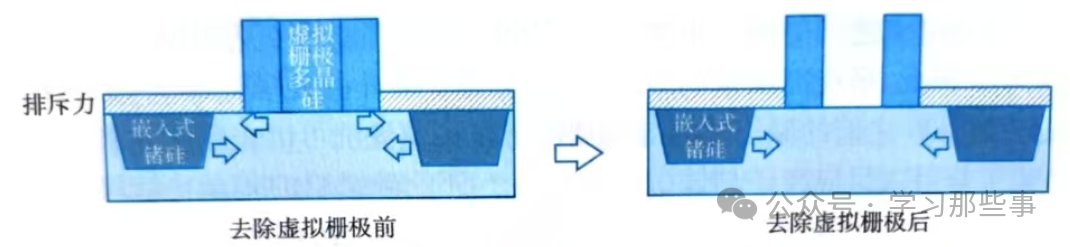

在锗硅源漏工艺的发展过程中,去除虚拟栅电极成为进一步提升应力效果的关键步骤。通过消除栅极的排斥力,可以增强作用于沟道的横向压应力,使沟道晶格发生形变,晶格常数减小,从而获得更高的沟道应变和空穴迁移率。以大马士革结构制造的PMOS器件为例,其作用机理可参照图3。在去除虚拟栅电极后,可在栅电极处的凹槽内填充多晶硅或金属栅。这一过程中产生的应力能够得到有效保留,从而提升器件的驱动电流。

图3:去除虚拟栅电极前后的效果图

图4:双极应力刻蚀阻挡层的补偿式金属氧化物半导体场效应晶体管器件示意图

原文始发于微信公众号(学习那些事):沟道应变工艺技术