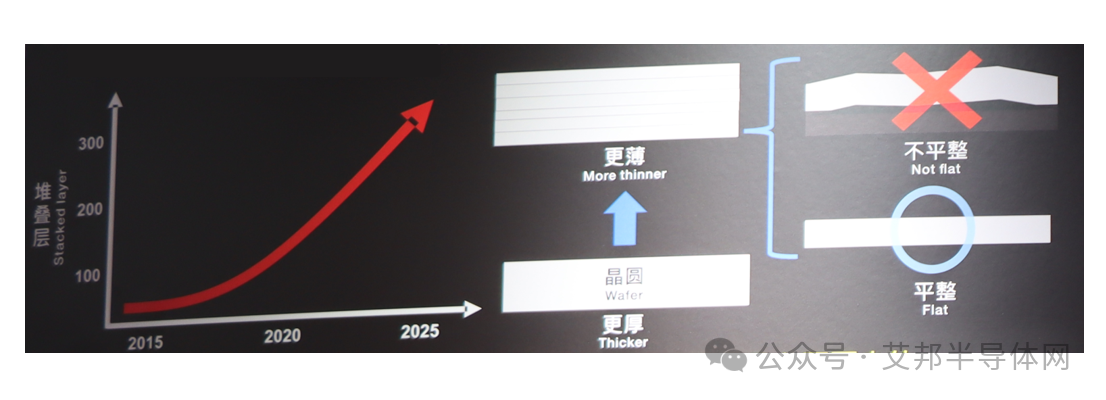

在半导体技术飞速发展的今天,“更薄、更小”已成为行业的核心趋势。从智能手机到人工智能芯片,高密度、高性能的集成电路需求不断攀升,而器件的薄型化与小型化正是实现这一目标的关键。本文将深入解析半导体器件为何需要持续缩小尺寸,以及背后的技术挑战与创新解决方案。

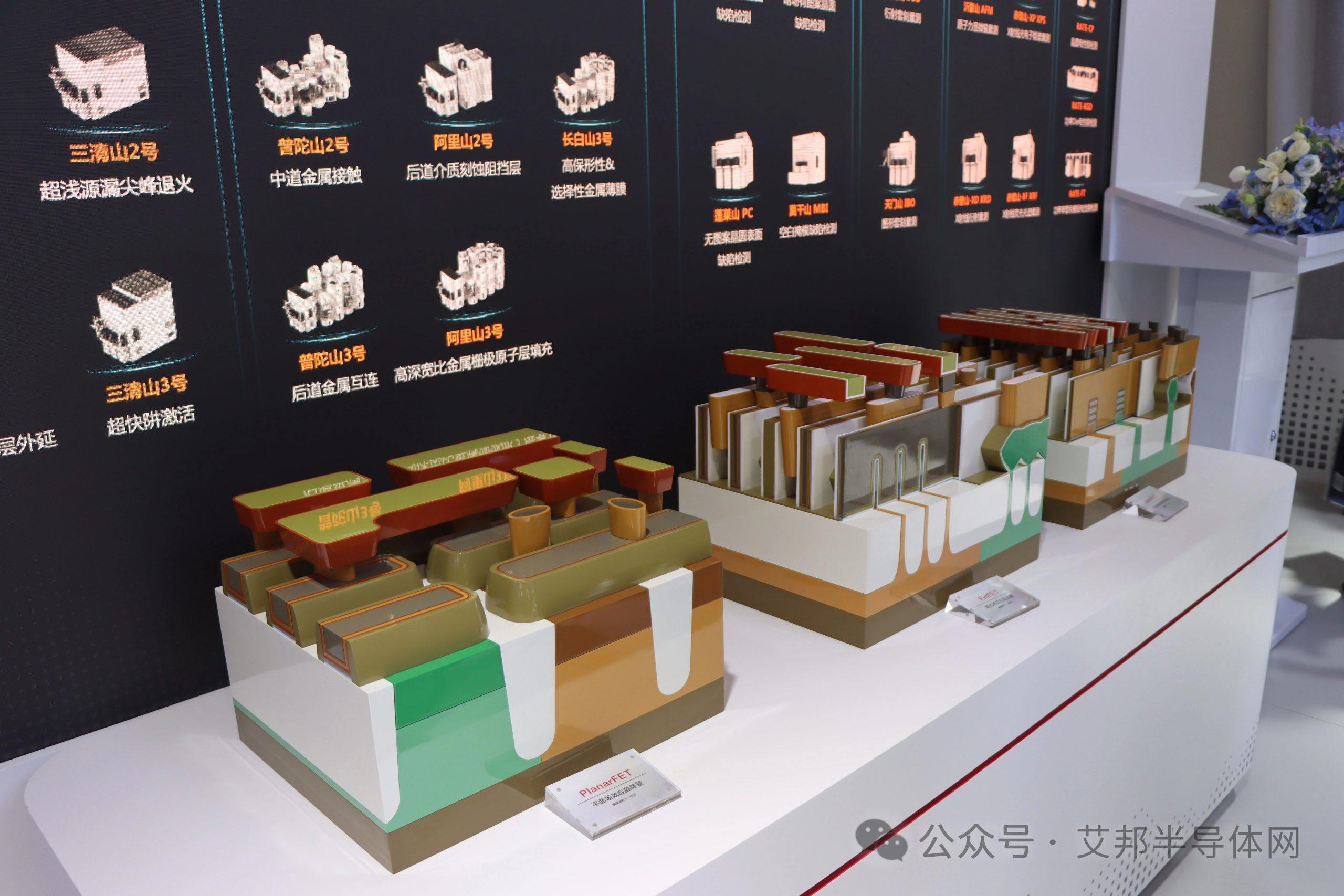

举个直观的例子:如果把芯片比作一栋建筑,缩小尺寸并优化结构后,可以在同样面积的土地上建更多房间(晶体管),且房间之间的通行(电流传输)更快、更节能。

晶体管图摄于新凯来展台

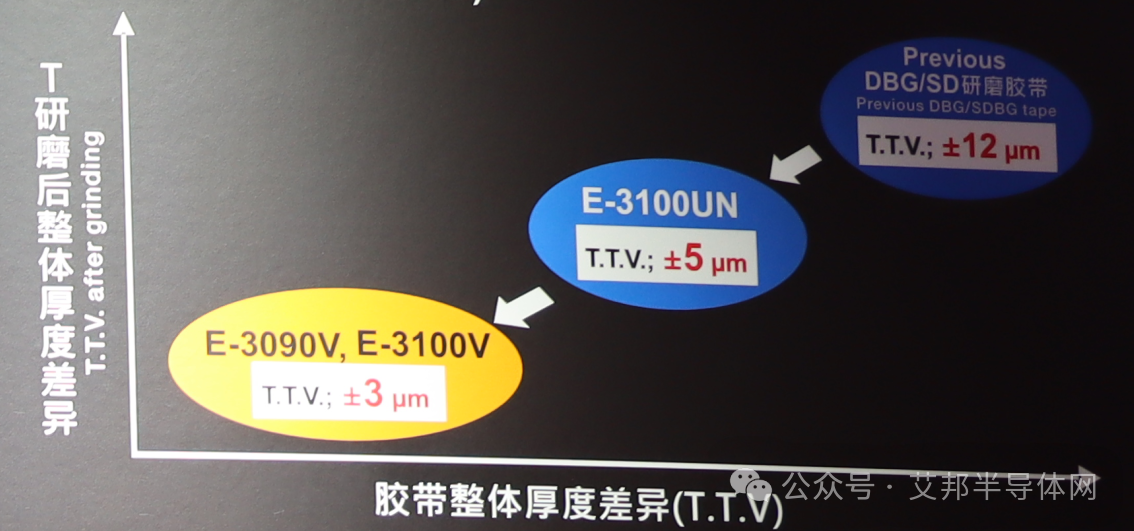

晶圆边缘是研磨过程中的脆弱区域,填充特殊材料后,不仅能防止碎裂,还能增强整体结构强度。这类似于给玻璃杯边缘包覆防撞条,避免意外磕碰。

6.抗静电

随着电路密度提升,芯片对静电放电(ESD)的敏感度呈指数级上升。一次微小的静电释放就可能导致内部电路永久损坏。尤其在超薄芯片中,静电防护需贯穿设计、制造、封装全流程,例如使用防静电材料、优化接地设计等。

结语:薄型化是通往未来的钥匙

从DBG工艺到边缘修整技术,从抗静电设计到材料创新,半导体行业的每一次突破都在为“更薄、更小”铺路。这不仅关乎性能的提升,更是打开智能穿戴、柔性电子、量子计算等新领域大门的核心钥匙。未来,随着工艺的持续精进,我们或将见证“芯片隐形于无形”的时代——而这一切,正始于今日的每一纳米进步。

(本文基于Adwill展会宣传图及行业公开资料整理,部分工艺细节可能因技术迭代有所更新。)

长按识别二维码关注公众号,点击下方菜单栏左侧“微信群”,申请加入群聊

活动推荐一:2025年第四届功率半导体产业论坛(6月13日 苏州)

Nico 肖:136 8495 3640(同微信)

邮箱:ab012@aibang.com

方式二:长按二维码扫码在线登记报名

https://www.aibang360.com/m/100230?ref=172672

一颗芯片的制造工艺非常复杂,需经过几千道工序,加工的每个阶段都面临难点。欢迎加入艾邦半导体产业微信群:

长按识别二维码关注公众号,点击下方菜单栏左侧“微信群”,申请加入群聊