搬运自我的微博(ID:giratinar)

目录

一.关于先进封装的碎碎念

二.2.5D先进封装

1.2.5D先进封装是啥

2.英特尔与台积电、日月光、Amkor在这一领域的布局

3.EMIB与EFB、CoWoS的产业逻辑

4.区分InFO与CoWoS

5.关于M1U的杂谈

6.Si-Fi技术

三.3D先进封装

1.定义与限制条件(排除MEMS和CIS)

2.关于3D Cahce的误会

3.关键技术——令人痛恨的TSV

4.关键技术——混合键合

5.英特尔和他的TCB

四.未来

1.台积电的野望

2.嵌埋式封装

3.14+14>7?

PS:分了好久用零碎时间写的,所以一些术语可能前后对不上,反正基板=载板,转接板=中介层

.一.关于先进封装的碎碎念

不知不觉写了这么多,为了避免歧义,本文讨论的2.5D/3D都是指在中段完成封装的东西,一些后段堆叠的封装不再讨论之列(比如单独的PoP封装)。谈2.5D/3D先进封装之前,再嘴碎多说几句,本文就是业务时间写的杂谈性质的文章,难免有疏漏,欢迎评论or私信指出,而且一篇文章要扯这么多内容肯定有很多覆盖不到的地方,仅仅是一个抛砖引玉的作用,有兴趣的多去外网查查资料。然后再瞎扯之前,先抛出两个观点:1.半导体行业很多时候并不是看技术先进与否,成本、商业模式和自身利益才是这帮人更优先考虑的,理解了这一点就能明白为什么有的企业要做一些”与众不同“的操作。2.封装演进的本质是在成本可控的情况下尽可能提升互联的密度与速度,所以先进封装并不是灵丹妙药,如果你造不出一个合格的SoC/chiplet,那用上什么封装都是白搭。

PS:下文可能比较少提到amkor和大陆封装厂,因为我手上关于它们的资料很少,我就选择性忽略了

二.2.5D先进封装

1.2.5D先进封装是啥

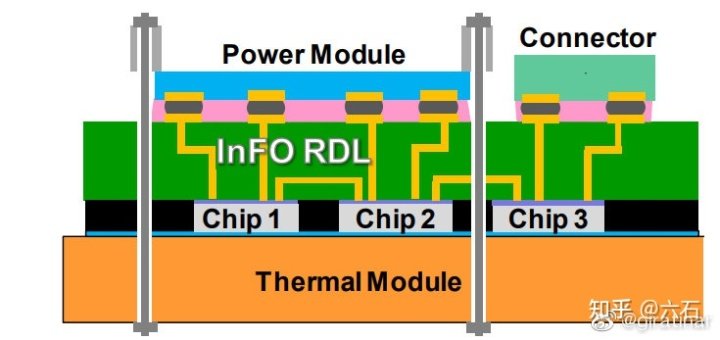

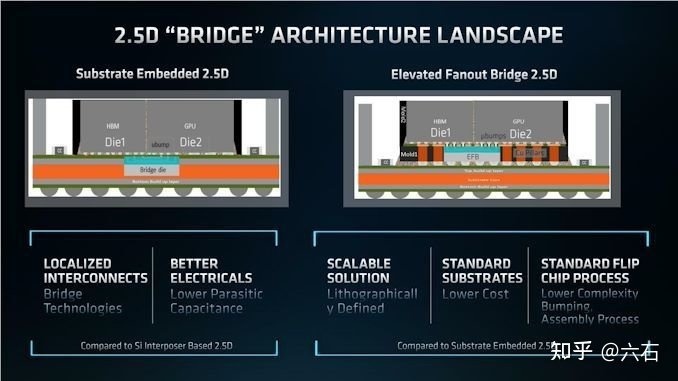

2.5D封装第一次走入大众视野应该是AMD的15年发布的的fury显卡,配合了4GB HBM显存(以前主要是一些远离消费领域的FPGA和ASIC使用过),在这之后,2.5D封装常常与HBM捆绑,频频出现在显卡、ASIC和FPGA上,但是从定义上,其实业界一直没有给出2.5D封装的严格定义,2.5D封装也不像3D封装那么直白,它其实有好多种形式,为了方便下文说明,我这里简单给2.5D封装做一个”定义“,2.5D封装指的是芯片/chiplet之间通过转接板(或者叫中介层)、硅桥、高密度RDL或者任何I/O密度远高于ABF载板的互联手段的封装,核心是两点:1.多die集成;2.互联部分引入高I/O密度的”介质“而不是依靠载板上走线,除此之外,用不用TSV、中介层是什么材质啥的不影响,基于这两点,我们在市面上比较常听到的2.5D封装有CoWoS(废话)、EMIB、高密度和LSI版本的FoCoS三种,正好对用了2.5D封装的三大类:1.互联层是整块转接板,2.互连层是一小块硅桥,3.互连层是高密度RDL或者RDL中的硅桥。

PS:InFO能不能算2.5D封装?InFO其实有好多种,如果是A系列用的那种只封单die的普通晶圆级扇出封装,应该是不能算,但是如果是多芯片封装然后RDL层IO密度高有硅桥的InFO(InFO-oS、InFO-LSI和部分InFO-MCM)算是2.5D封装,同理可以推广到FoCoS等扇出技术上。如何快速辨别呢?有个小把戏就是看它RDL层底下需不需要载板,需要的话就是2.5D封装(大概率)。

PS2:AMD在目前ZEN处理器上用的是2.5D封装吗?这里注意区分一下chiplet和2.5D封装,这两个概念是分开的,有些文章把他们划了等号,chiplet目前更多是一种设计理念,ZEN系列使用了chiplet,不算用了2.5D封装。

2.英特尔与台积电、日月光、Amkor在这一领域的布局

我觉得没什么好一一介绍的,干脆写个"等式",然后讲讲里面比较”特殊“的EMIB和InFO-SoW。

2.5D封装可以简单分成3种:

1.一整块硅/玻璃等做中介层,所有芯片放在这个中介层上,性能在大多数情况下可以说是最好的,缺点也很明显,太贵了,目前这个技术除了英特尔,每家都有实际商用的,最典型的就是台积电的CoWoS-S=各家名叫2.5D interposer的封装技术

2.使用硅桥互联,这几乎是目前性能与成本最平衡的技术,但是除英特尔以外的厂商应用的时间节点更晚,基本上台积电的InFO-LSI=日月光的FOCoS-LSI=安靠S-cennect≈EMIB,EMIB比较特殊,下文会重点讲一下。

3.使用高密度RDL层互联,这几年有所突破的一个技术,通过SAP加成法沉积铜线路而非Embedded法,实现了高布线密度而高I/O密度,一定程度上能替代整块的转接板(高密度RDL以后有机会另开文章说,相关的论文还没看完

),基本上台积电的CoWoS-R≈InFO-oS=日月光的FoCoS高密度版本=安靠S-Swift。

4.论外:InFO-SoW,本质上也是高密度RDL互联,但是,是什么样疯狂的灵魂要搞出这种东西

可以说风格也和第一个用上它的客户特斯拉很符合了。

在之前写扇出封装的文章里,我觉得InFO-SoW只是实验室对封装尺寸的极限探索所以没有介绍,后来特斯拉用Dojo打了我的脸。一句话总结InFO-SoW就是既然这世界上有cerebras这样想做超大芯片的人,就有想做超大封装的人

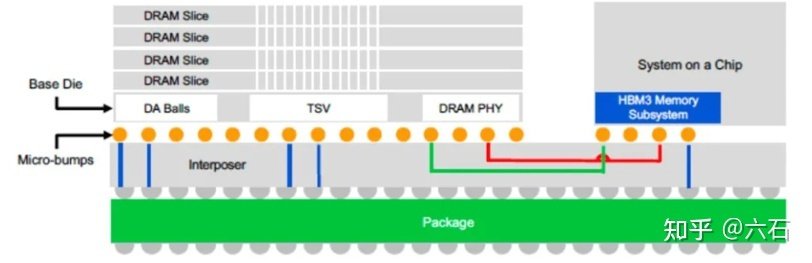

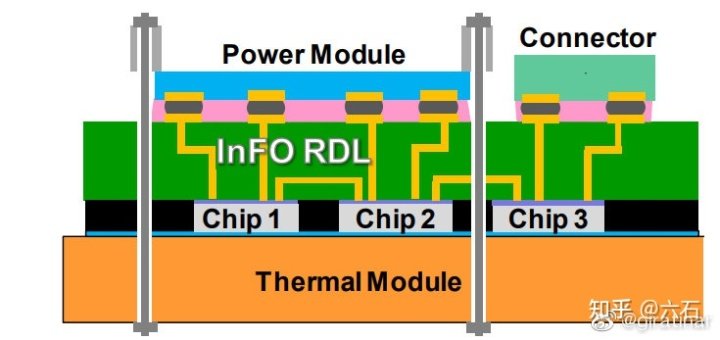

,InFO-SoW就是面向大规模MCM而生的,它把芯片阵列用晶圆级的RDL层连接在一起,还集成了功率模块、互联单元和“晶圆级”的均热板(如上图),实现了system on wafer,InFO-SoW封装甚至把基板、PCB都给去掉了,成品就是一个用金属架子支撑结构的大盘子

直接就可以放在模块里用了。

为什么台积电会想搞这样一个玩意?我们回看现在基于基板甚至板级的MCM封装,有一个很大的问题就是怎么解决C2C(chip to chip)的互联,基板上互联最直接粗暴,但是高层数ABF基板可怜的良率和成本并不能支撑你去做一个大规模的MCM,同时该死的趋肤效应会给你的信号传输带来巨大的困扰,更不要说板级MCM了,而硅中阶层的方法好是好,但是太贵了,如果真要做一个芯片阵列级别的MCM封装,成本吃不开,InFO-SoW的解决方法就是怼了6层的RDL,让布线空间充足无比,信号完整性和功耗表现也更好,同时直接在芯片封装成品的边缘上方放置了Conenctor单元方便与外界互联,power单元也直接怼在芯片正上方,真的是大力出奇迹的典范。

因为面向高性能领域尤其是AI应用,InFO-SoW设计之初就没有考虑过风冷,直接上了水冷散热,台积电的给原型产品设计的最大散热功耗可以达到7000W,可以说是非常凶猛了

3.EMIB与EFB、CoWoS的产业逻辑

EMIB是一个很有趣的东西,它能够达成和使用整块硅中介层差不多的性能,也不需要像中介层打大量的TSV(在后续部分我们会聊一下为啥TSV这么令人讨厌),使得硅桥本身的制作工艺更简单,成本也更低,并且引入硅桥之后,原本需要10层以上的ABF基板可以较少到7层甚至4层,这对节约ABF基板成本帮助很大(10层板良率不到50%,每多一层良率还要下降),因此英特尔这么多年”懒得“使用硅中介层这种技术。本质上EMIB它也是一种硅桥技术,但是和AMD展示的EFB、InFO-LSI不同,它的硅桥是嵌埋式的,硅桥互联最早在2011年由英特尔提出,然后在2016年这个技术变成了现在EMIB,拥有了嵌埋的概念。之后EMIB逐步被英特尔拿来主要在服务器端使用,EMIB可以无视光刻曝光的尺寸限制(硅中介层面临这个问题的,苹果的专利里有探讨类似的内容),可以随意在横向扩展各式各样的芯片,属于好用又”便宜“的玩意,那么为啥嵌埋式硅桥或者说硅桥这么好用,台积电、日月光没有第一时间跟进呢?答案是各家的商业模式决定的,下面以EFB为例探讨一下这个问题。

AMD在MI250X上展示的EFB应该就是和 InFO-LSI或者FoCoS-LSI的改型(大概率是后者,日月光的定制版本),两个硅桥技术的区别就是一个会对载板进行加工并且是嵌入在载板中的,一个不需要动基板,整个硅桥是在RDL层之中的, 然后EFB是平面工艺,这意味这它可以使用标准的FC封装,这里的使用标准FC封装其实是指芯片完成与EFB合封之后可以用FC贴到基板上,这样在后道的基板级封装上灵活性就比EMIB好很多(方便换厂商),也不用寻找能做嵌埋硅桥的基板厂商,另外EFB因为多了一层RDL层调高了芯片整体的高度,所以die需要做更进一步的减薄。

这么来看,EFB是个好技术,苹果M1U也采用了类似的技术,但是之前为啥除了英特尔以外没什么人用?更别说EMIB这类嵌埋式硅桥了,按理说弄个硅桥对大家来说都不难啊?问题其实不在于技术上,而是商业模式上,回到文章开头的第一个观点,半导体这个行业,很多时候不是技术导向,而是商业导向...做EMIB,同时需要对硅和基板有深入加工的能力,而英特尔是个IDM,它有fab和封装线,天然适合这么做,甚至英特尔可能比基板企业更了解基板材料和性质毕竟,ABF的一切几乎都是它定义的,而事实上,英特尔为了EMIB,开发了特殊的加成法基板制备工艺和硅桥嵌埋在基板上的特殊面板级封装工艺,贴装的DAF材料和电镀药水也是定制的,这种折腾程度只有IDM玩得转。而对于台积电来说,它能力在硅上,它不想也不希望动基板,基板良率又低价格又高,为什么我不安心搞我的2.5D中介层?甚至台积电连硅桥也不想做,因为硅桥价格比一整块中介层低太多 了(你们这帮芯片企业又想用上HBM和大面积MCM, 又不想买我800m㎡+的中介层!),对于用了硅中介层的芯片,台积电也只做到封好芯片+中介层,中介层贴装到基板上的步骤交给别的OSAT…而日月光等OSAT,缺乏做硅桥和中介层的能力,它们也不是很想碰这些东西,所以他们主推的是高密度RDL互联或者直接wafer to wafer键合。但是对于芯片设计公司来说,他们很希望有一个比硅中介层便宜,性能比传统RDL互联好的方案出现,他们也渴望自己不会被绑定在某一家封装厂或者载板厂上,这个需求又推进业界开发一个对标EMIB的硅桥技术。

硅桥自身也是要对外互联的,以前只有英特尔特制的ABF基板能满足硅桥对外互联的布线需求,但是你要fab和OSAT玩这个不是为难人家吗?于是,有人想到用扇出封装里的RDL层代替基板,包覆住硅桥(这就是为啥EFB会高出一层,这层是基板代餐

),可惜早期的晶圆级扇出封装的RDL不足以承担这个密度的布线,直到后来业界迎来了高密度RDL技术的突破(于是今年一下子AMD和苹果都上了),高密度的RDL使用了前道半导体级别的工艺,精度非常高,可以实现2微米线宽,一下子在技术指标上拉到和EMIB一个水平,而且成品是兼容标准FC工艺的!(这点很重要)。

小故事一则(复读我以前的微博):当年Fury显卡领先业界用上了HBM显 存,但是一直缺货,官方说法是HMB良率不行,这里有一个另一个版本的故事,Fury是业界最早用上 2.5D封装的显卡,AMD觉得核心和硅中介层不要都放在台积电做,台积电开价太狠了,于是找来了别的OSAT,OSAT说硅中介层我搞不定,于是AMD又拉来了联电,联电很开心,不光帮助设计了硅中介层甚至排了产能专门做硅中介层,然而等到量产的时候台积电,联电,OSAT,AMD四方终极拉扯...互相指责对方环节有问题,于是Fury就这样在拉扯中度过了一生从此以后,AMD还是决定在台积电把芯片+中介层做完封装完再拿出去找OSAT,但是,资本家怎么会让别人一直赚自己的钱呢?现在出现的EFB是一个兼容标准FC工艺的封装技术,硅桥、RDL层合封、贴装在基板上等工序都可以找不同的厂商来做,AMD依然没有放弃它的”灵活供应链“之旅,利益最大化没毛病,这行业都是这样打算盘的。

4.区分InFO与CoWoS

在苹果M1Ultra发布之后,国内媒体都在传一个台媒新闻,M1U使用了台积电CoWoS-S,我当时看了发布会上关于互联的演示,和朋友吐槽这绝对不可能是CoWoS-S,要么CoWoS-L要么InFO-LSI,还发了微博,后来台积电证实了M1U使用的是InFO-LSI,那么如何区分InFO与CoWoS?

由于有载板类的InFO封装的出现,InFO不再像以往只能封装一些面积小的芯片,封装尺寸可以比肩甚至超过CoWoS,而CoWoS本身也分为S、R、LSI三种,一般我们提到CoWoS,默认就是在说CoWoS-S,也就是所有芯片被承载在一层硅转接板上,这是最经典也是性能最好最常见的CoWoS,缺点就是成本很高,一般来说,当一个芯片用了硅桥而非整块的硅片,基本上可以确认是使用了InFO-LSI或者FoCoS-LSI等类似的工艺,CoWoS实际上也有一个R(用高密度RDL代替硅转接板,对位高密度的FoCoS),一个L(硅桥+RDL版本),这两个和InFO-oS、InFO-LSI看起来形式上是一样的,甚至参数上都重叠了,除非厂商自己回答或者开盒检测,不然是几乎无法通过纸面数据区别。

这两类东西在生产流程上倒是比较好区分开来,RL在流程上和CoWoS-S类似,即中介层是可以单独生产出来交给客户的,客户可以拿着中介层配上die找别人封装的,而InFO-oS和LSI则基本上不存在独立中介层一说,它的中介层也就是RDL层是扇出封装的一部分,交到客户手上一定是包含了芯片的一个整体,当然客户可以把这个整体拿去继续找别人做进一步封装,比如pop堆叠一个内存或者贴装在基板上。

5.关于M1U的杂谈

M1U发布以后,不知道谁先提出了的,M1U是一对M1Max不切割直接从晶圆上直接切下来的

其实这个谣言想一下就知道靠不住,首先果子为啥用先进封装,不就是封装技术演进到足够互联多个高性能SoC所以不用再制造单颗大SoC了吗,结果它又跑回去找一对面对面完好的M1MAX去做整切芯片了?这不是搬起晶圆砸自己的脚吗?其次,如果是一对整切,那实际上下半个M1MAX是要被翻转过来的,在量产中是没有人会这么干,像蓝宝石激流,看起来是4个一样的die,实际上是两种在不同晶圆上互为镜像的die。(还有如果一边M1MAX有瑕疵要屏蔽部分单元,那对面的M1MAX是不是也不得不屏蔽几个给你凑凑?乐

)

这时候就有人会说,不是很多大V都说苹果专利里面就是整切的啊,首先,702A1那个专利本质是写一种直接在BOEL上通过build-up做互连层的专利,可以不需要引入硅桥,不需要TSV就直接与周围的die形成互联,其实与目前的M1U关系不大。当然这个专利也说明了,如果die和周围的die互联没问题,可以考虑整切,这个玩意根据果子专利里给的图,每个die有等边的IO互联部分,整切出4连芯片,至于未来会不会见到这种技术,不好说,回到文章开头的第一个观点,看成本看商业,有兴趣可以借助晶圆良率计算器算算,要4个没问题或者品质一致的die整切,是不是个容易的事。

真正关于苹果目前商用的封装技术,应该是在504A1里,几乎就快把硅桥两字写在脸上了

另外这份专利可以看出果子在材料上也下了很大很大的功夫,有兴趣直接去搜这份专利吧~

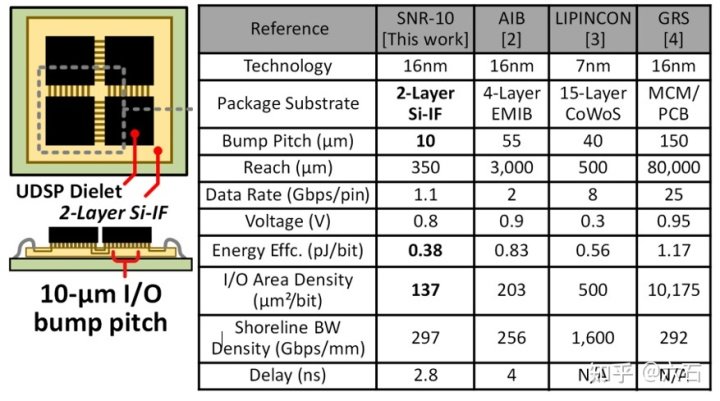

6.Si-IF技术

夹带一个私货

,Si-IF互联,在ISSCC2022论文里看到的一个挺有意思的”2.5D封装方式“,

Si-IF似乎是一种嵌埋式的“硅线?”,只需要两层,能够实现100um距离的高速通讯,基本上各方面都优于传统的板级MCM,占地面积和能耗比超过目前所有互联方案(虽然单位面积的速度不高),挺好奇这个Si-IF后续会不会被推广,是一个比板级MCM走线好不少的方案,目前我也不知道这个Si-IF的制作工艺和是哪家厂在推进的,但是一旦碰到了基板中的嵌埋,事情就会复杂起来

。顺便上图这个表里也说明了一个问题,板级MCM没有那么不堪,在不少关键数据上是不比表里早期的EMIB差多少的,这也说明了为啥ZEN系列和英特尔自己的合封了一个I/O die的笔记本处理器为啥不用硅桥技术了(当然是太贵了

)。

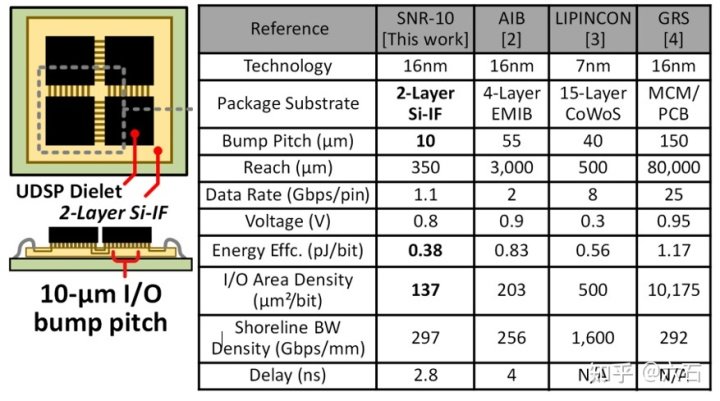

三.3D先进封装

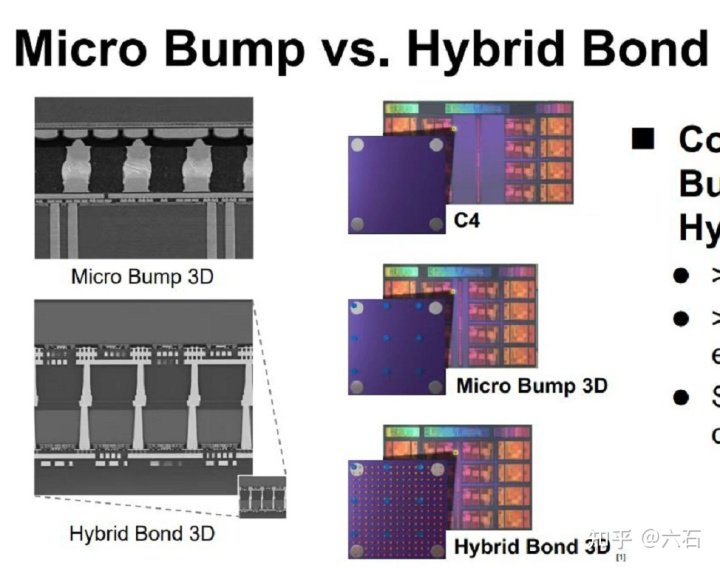

1.定义与限制条件(排除MEMS和CIS)

在说3D封装之前,有必要说说3D封装到底是啥,就如同上图所示一样,如果只是以简单的两个东西堆叠来定义3D封装的话,那3D封装有很多很多,也早就被应用在各个领域了(比如POP封装,现在的手机芯片基本都是SoC上堆叠了一个DRAM,比如NAND颗粒里的堆叠)。所以狭义的3D封装是排除了这类”简单“堆叠的封装,它一般是指,在一个封装体(比如一个molding里、一个金属顶盖下)两颗die在垂直方向上直接互联的封装(POP封装下,DRAM与下方的SoC并没有直接互联)。而这两个die,一般来说是被动芯片(一般是各类存储)叠在主动芯片上(计算芯片、BASE Die、I/O Die等等),比如5800XD,或者主动叠在主动上(主动叠在被动上那就是2.5D封装了

),比如LakeField。

目前见的比较多的是被动叠主动,业务已经有不少叠了SRAM的AI芯片出现,还有5800XD这种消费类的产品,这种3D封装形式常见的原因也很简单,因为设计上冗余程度更大,主动芯片的设计也更自由,下方的主动芯片本质上还是一个普通的SoC/chiplet,上方的被动芯片一般是一块SRAM,而主动叠主动则是把一个SoC拆成不同部分再堆叠起来,得考虑不同部分之间得互联还有散热问题,尤其是后者,几乎是现在主动叠主动的死穴,英特尔迟迟不在3D封装上用混合键合也是有这方面的考虑。

至于3D封装缺陷吗,这里不多介绍了,应该是人都想得到吧,发热、贵、设计复杂、电磁干扰严重、热应力、结构。。。。。

然后CIS和MEMS上的3D封装,下文就不讨论了,我也不太了解,CIS封装帮助行业试水和量产了很多关键技术,比如TSV、混合键合、CU直连、RW等等,做CIS封装的OSAT不少都有能力去做数字芯片领域的先进封装。还有射频、光电领域的先进封装这里也不讨论了,以后有机会另说。

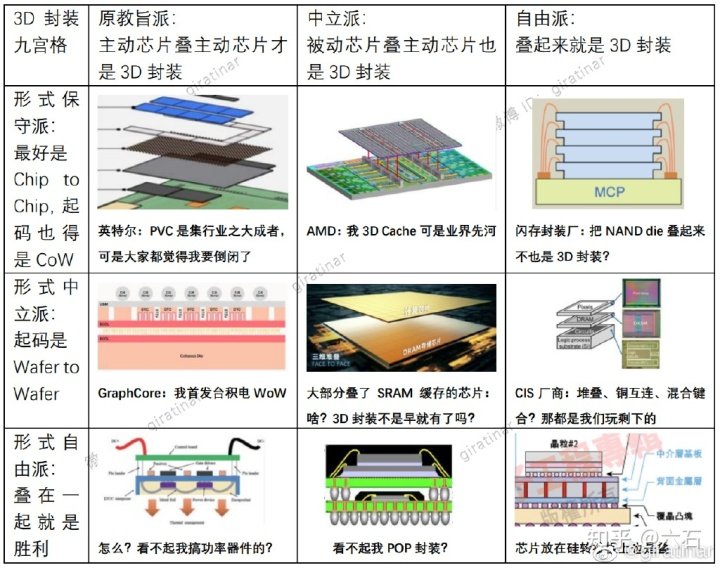

定义完3D封装,下面就介绍一下3D封装几个关键技术,一个是TSV,一个是混合键合。

2.关于3D Cache的误会(一部分搬运一下以前的回答)

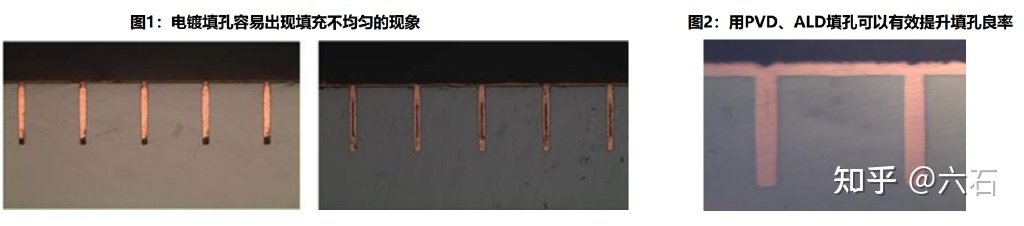

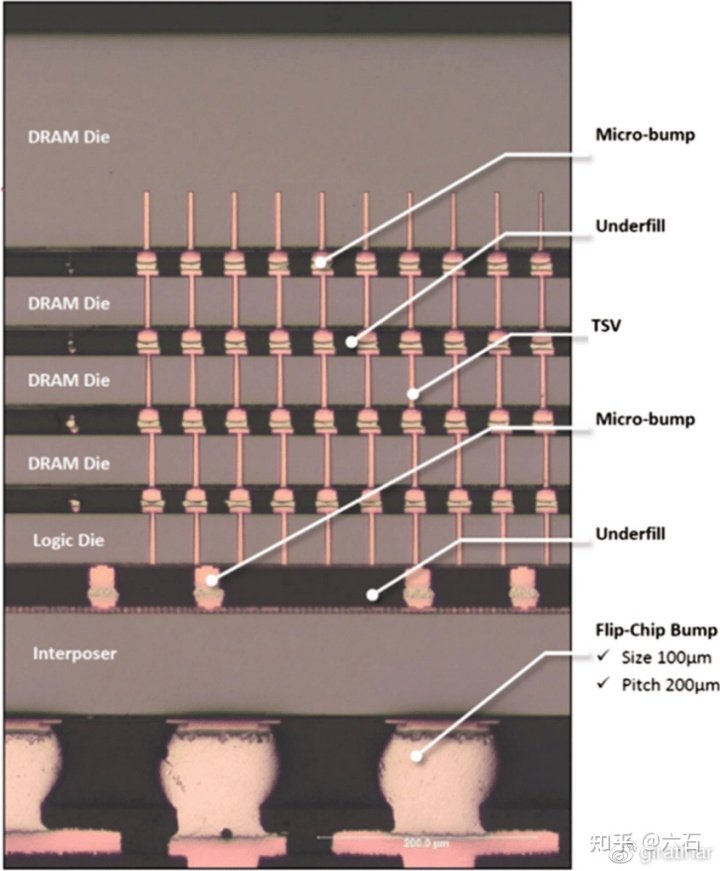

在聊TSV和混合键合之前,先扯几句AMD的5800XD上的3D Cache,也算作为一个引子吧,在3D Cache技术公布之后,包括linus、Anandtech、AMD油管官方平台、很多知乎和微信文章里,都把3D Cache的成功归结于TSV对比ubump的优势,对真正的核心点混合键合几乎无视,这其实让人很摸不着头脑(semiwiki就没有,而是直接点出了关键点在混合键合)

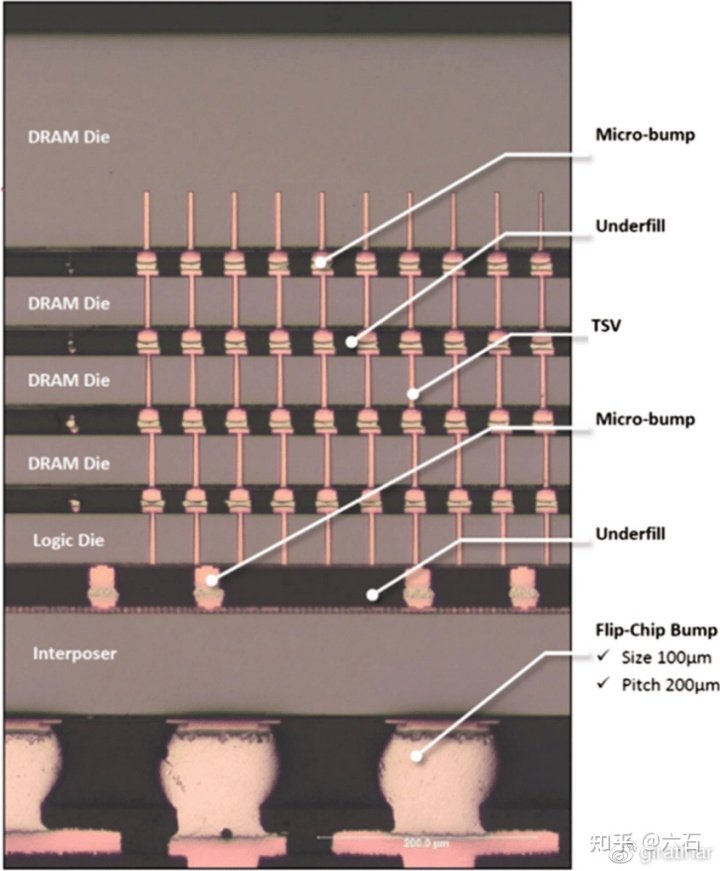

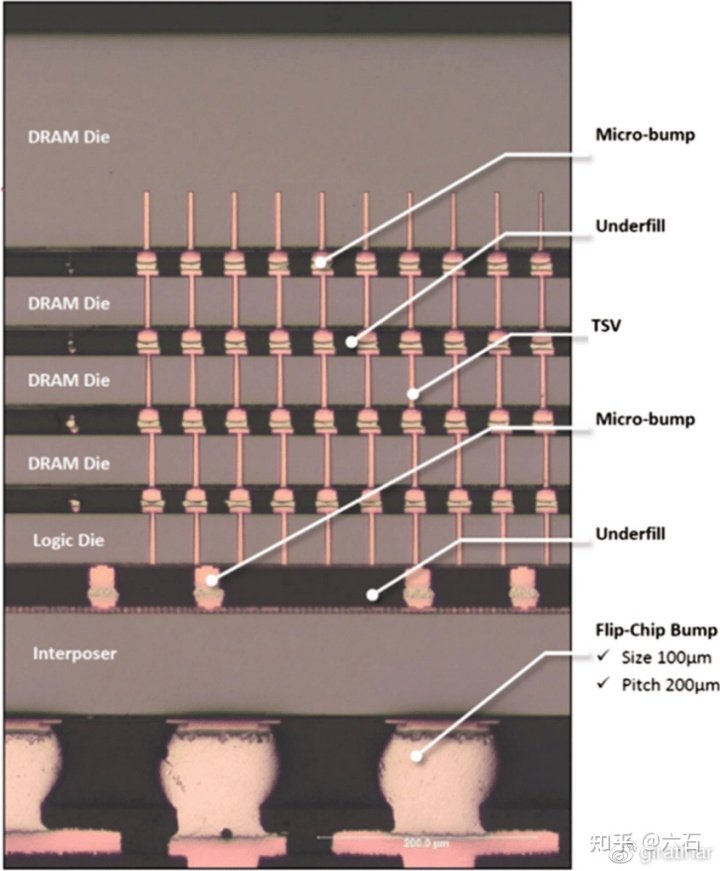

TSV在芯片内部的,作用是垂直方向传输信号,而且两个芯片垂直方向上3D物理互联是用不了TSV的…和TSV无关……因为这个已经在芯片外部了…ubump/混合键合/cu-cu互联/微铜柱这些和TSV不一样,这是两个东西,TSV/TDV/TGV都是芯片或者介质里做通孔,像在芯片里面建电梯一样,打通数据在垂直方向的传输,ubmp/混合键合这些是两个芯片垂直方向物理上的直接粘合/键合(当然它们也可以传数据和供电) ,所以那些文章说3D cache比英特尔3D互联封装强的原因是因为使用TSV而不是ubump真的让人摸不着头脑,何况英特尔3D封装里有TSV。。。

目前现有的3D主要有两种,一种是F2F(即晶体管、信号层所在那层面对面互联) ,因为信号层贴脸了,所以不需要TSV,使用晶圆级的混合键合就可以了,这类封装国内的武汉新芯做的很不错。另一种是F2B(B就是芯片的背面,那里只有没有实际作用的硅),这种一般是芯片对芯片/晶圆键合(c2c/c2w),由于底下的芯片自身是倒装贴装基板上的,所以需要使用TSV,一般是ubump+TSV,典型是英特尔现在的3D封装。ubump的IO密度是低于混合键合的,但是在芯片对芯片/晶圆的3D封装上,使用混合键合是很难对准的,所以一般得退而求其次使用ubump。而AMD这次展示的3D封装,是混合键合+TSV的,没有使用ubump(所以通稿还怼了英特尔一下哈哈),而且更狠的在于台积电现在这个3D封装在提供比英特尔等厂商现有3D封装厚度更低,I/O密度更高的性能指标下,还允许封装上层芯片面积自由选择,不需要和下方芯片面积一样!(传统的晶圆级键合没有这么自由,而在5800XD上我们可以看到AMD并不需要和CCD一样大的缓存芯片),我还记得和某做服务器芯片外包封装设计的人提到这个事的时候,他的第一反映是这是不可能的

除非台积电找设备厂定制了一套新方法,事实上,在3D cache技术亮相的那个时间节点附近,确实可以看到一则应用材料与合作伙伴在混合键合上取得重大突破的新闻。

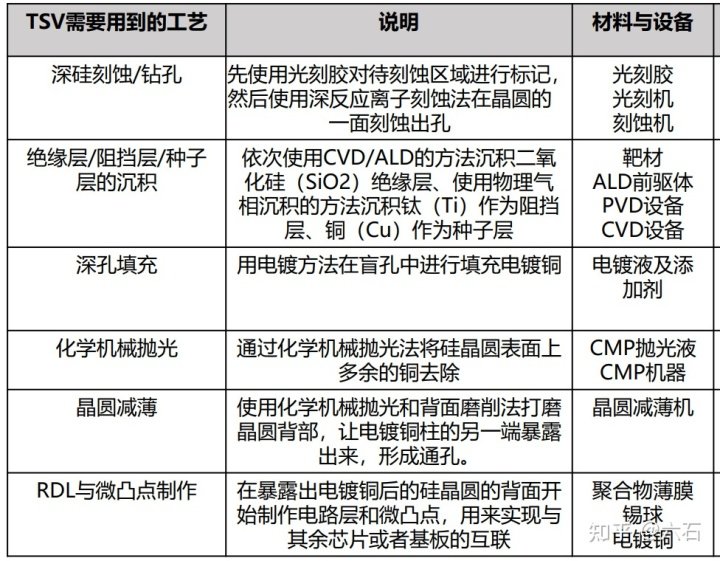

3.关键技术——令人痛恨的TSV

本来还想多写一些TSV,但是发现有篇很好的文章可以看看,《TSV简史》一些内容我就不再写了,大佬写的比我好多了。TSV从诞生之初到现在,业界其实一直在头疼他的良率、它的填孔好坏怎么解决,作为先进封装至关重要的组成部分,TSV一直是令人又爱又恨的东西。

可能有人会说,我看我家乡那里,某某小封装厂说自己的TSV工艺很成熟,怎么会难做,其实TSV也封好多种,很多封装厂口中的TSV,其实是一种梯形的斜孔,深宽比较低,一般只到芯片的信号互联层,难度自然也低。而穿过整个芯片,实现上下完全互通的TSV是一种深宽比较高的通孔,会直接侵入晶体管所在的位置,它的难度大,良率低。

更麻烦的在于,TSV如何更好更快的填充?传统的TSV都是使用电镀法,但是电镀法填充容易出现有空穴、孔壁有毛刺不够光滑等问题,尤其是在先进封装使用的深孔填充中,这是一个令人头疼的问题,除了良率更低以外,因为趋肤效应的存在,填充的不够好的通孔在传输高频高速信号会严重的损耗,使得芯片达不到预期的性能。目前业界已经开始尝试使用PVD甚至ALD来填充TSV(这两者本身就是TSV沉积绝缘层和种子层的常用设备),但是成本和速率还远远比不上电镀法,未来TSV填孔如何解决只能交给时间来回答了。

4.关键技术——混合键合

我还记得我2020年见到英特尔封装研究院前材料首席研究员(发明了喜闻乐见的CPU上的钎焊、各类bump、EMIB材料、Fovers封装的材料)的时候,她信誓旦旦的和我说,混合键合问题很多,解决不了发热和信号传输问题,英特尔不会用的!在当时Fovers还是用ubump实现了主动芯片上堆叠主动芯片,虽然是lakefield

,后来的GPU PVC也是。混合键合还只是在主动叠被动以及传感器上使用,甚至如今AMD的5800XD也是如此,(GraphCore的那颗用了台积电WoW3D封装芯片我仔细看了一下,下方的die是专门做供电的,严格来说不太能算主动叠主动)直到英特尔后来自己画了饼,说Fovers下一代Fovers-direct将会使用混合键合

我一时感到有点语塞,所以英特尔找到了方法用混合键合实现主动芯片叠主动芯片?我想大概率和那个ODI技术有关系,用大铜柱辅助散热和供电,也不知道14代处理器会不会用上混合键合。

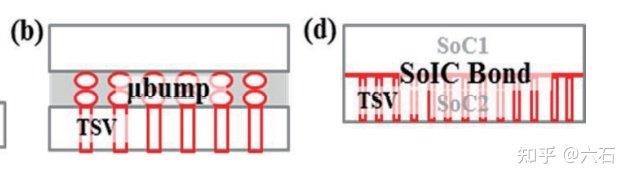

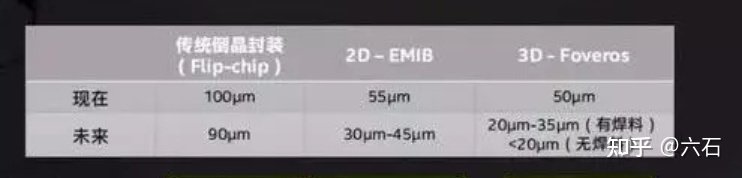

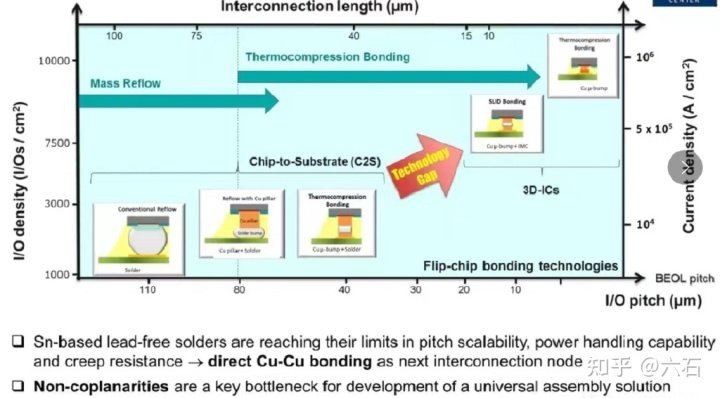

好了瞎扯完了,正经聊一下混合键合,混合键合这个技术逐步流行的原因很简单,如文章开头第二个观点所说,封装演进本质是提升I/O密度的提升,像上图一样,传统的FC每个焊点之间的间距只能到90微米,可以简单理解为间距越大,IO密度越低。EMIB努力努力,能达到30-45微米,和CoWoS到一个水平线上,3D-Foveros使用比C4还要小的ubump,间距在25微米左右,和InFO-LSI一致。

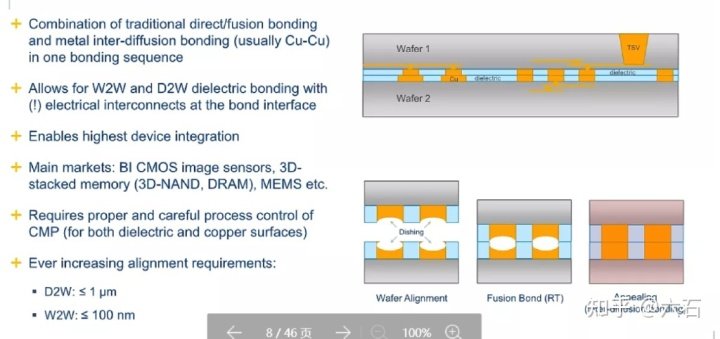

但是再往下,受制于原理,本身就是一个球的bump已经很难再缩小间距了(办法也有),于是以微铜柱为核心的混合键合就逐步走入先进封装领域。一般我们说混合键合,都是指铜混合键合,早在2005 年,一个叫Ziptronix的公司就推出了一种称为低温直接键合互连 (DBI) 的技术,后来这个技术被索尼买去了,用在CIS的模拟层和数字层堆叠上,这项技术也因此现在CIS领域普及开来,使得很多封装厂都有做晶圆级键合的能力。

bump本身是有是由局限性的,传统的bump只能把间距缩小到20微米,再改变材料,复用类似工艺流程,并借助TCB(后文会说)的情况下,也只能到7微米了,但是别忘了ubump本身还不小(直径5微米是目前最秀水平了),所以实际IO密度会更低。而混合键合可以缩小到3微米,本身尺寸可以做到1微米,这对于bump来说,几乎是碾压的。

但是同样的,混合键合也有很多麻烦,混合键合用于晶圆到晶圆w2w和芯片到晶圆c2w的键合。混合键合工艺一样也很复杂所需的芯片在晶圆厂的两个晶圆上进行处理,将需要的介电材料沉积在晶圆的一侧,然后为晶圆上的每个芯片在对应的沉积层上通孔。再将铜材料沉积上去。然后,化学机械抛光 (CMP) 工具抛光表面,把多余的铜抹去,剩下的是每个芯片的微小通孔中的铜金属化材料(与TSV异曲同工了),然后再经过检查、进一步的CMP,最后才是使用晶圆键合机,将其堆叠并键合到第二个晶圆上。

然而在键合的过程中,精度也是一个非常令人头疼的东西,尤其是c2c/c2w这类的键合,一旦上下两个die面积不一样(像5800XD),这难度还要成倍增加,另外键合的时候是需要“高温”让铜融化连在一起的这里面又会有很多幺蛾子,比如晶圆翘曲、键合过程中开裂,还有很多奇妙know-how:大家都知道热胀冷缩,所以像上图右下方的图示一样,黄色的铜会被减少一些,让它在受热过程中膨胀正好完成互联,但当这个铜柱缩到足够小的时候,反而要让铜多出来一些。。。。

总之,键合也不是一个善茬,但是让英特尔和很多以倒装为主的封装厂一直“抵触”键合的原因还有一个,混合键合所需要的设备和倒装基本不一样,相当于他们之前投的设备是不能用的,工艺积累也是白费的,反而像台积电这种它没有历史包袱,这又回到文章的第一个观点了,每个企业自身的商业模式和利益考量,也会影响它们的技术选择。下面就让我们来聊聊,大怨种英特尔和它的TCB

5.英特尔和他的TCB

前面我们提到,混合键合的设备与原本兼容倒装和bump的设备是完全不同的,这对于IDM的英特尔和很多封装厂来说是很不友好的(资本家:又要掏钱买设备?以前的为什么不能用?)英特尔是因为花了大钱买了很多TCB设备,而对于大多数OSAT来说,这项技术成本过高,需要昂贵的半导体晶圆设备来实现这些工艺,反而是UMC、台积电对混合键合很积极,它们可以复用自己的半导体晶圆级设备。

而bump再往下走通过改进材料(从锡球变成铜块)和工艺,是能把间距做到10微米以内的,这种bump现在一般叫做微凸块,而这种微凸块在大部分工艺流程和设备上与原本的bump是类似的(起码是一个技能树上的)英特尔封装开发工程师Zhaozhi Li在去年的ECTC大会上表示。“在保持与现有硅和封装技术兼容的同时,利用现有的基础设施,将焊料微凸点互连微缩至更小的间距可能仍然是有利的。”他这个话,代表了大部分OSAT和英特尔自身的想法,即尽量兼容原有工艺,然后使用的一种名为TCB(热压键合)的技术实现10微米间距以内的微凸块贴装用以满足先进封装需求,而不是直接上混合键合。(还有个技术路径是LAB,是安靠和长电主推,这里不谈了)

TCB 工艺有什么特殊之处?在这之前我们先看看传统的倒装,标准倒装芯片会被芯片放置工具将放置在基板、中介层或载体上,一次放置是上百甚至上千个。然后将放置好的模具组进入回流炉,这数百个甚至数千个封装放入烤箱中,加热到使焊料熔化的温度以完成粘合,然后继续批量进行后续步骤,这个过程很快效率也很高,但是由于回流炉中加热会导致芯片、基板、焊球以不同的速率膨胀,从而发生翘曲导致芯片不能很好的被粘合,最后导致良率出现问题。而随着bump本身在变小,间距在缩小,这个问题也越发困扰厂商,像早期2.5D封装的芯片普遍都遇到了良率问题就是因为倒装本身不够”精细“。随着bump逐步走到10微米以下,传统这种批量加工的方式显然已经不适合了,bump尺寸的减少转化为更小的错误余量,因此TCB应运而生。

TCB(热压粘合/键合)工艺中,不再有把大量芯片批量运送到回流炉这一步了,而是使用单一工具放置单个芯片,直接对这个芯片施加压力并加热它们以回流粘合焊球。这种方式从芯片顶部加热(因为本质还是倒装,所以加热的那面是没有晶体管的硅),因此只有芯片和bump焊接连接处会发热。这就避免了下方基板翘曲问题,而且由于是单一放置且主动施力,可以确保均匀粘合,没有间隙变化或倾斜。同时TCB设备在粘合时候还会伴随着快速振动,破坏铜焊盘和焊球上的金属氧化。也因此TCB在相同的bump间距下能实现更好的电气特性,也允许bump间距缩放到更小的尺寸,这种方式也适合对非常薄的芯片进行堆叠封装,这是HBM普遍使用TCB的原因(HBM厂商也在研究混合键合的办法),与标准倒装芯片工艺流程相比,TCB似乎是一种完全更好的技术,除了回流部分以外基本和倒装一致,为啥TCB实际上除了英特尔之外用的厂商不算多呢?当然是成本和商业模式的问题啦~

TCB每小时能处理的die数量只有传统倒装设备的三分之一甚至更低,成本却接近后者的三倍,这对OSAT厂商来说是一个巨大的坏消息,本身OSAT厂商毛利就不高,还要用上这种花钱工艺,在技术还没成熟、客户接受度不高的时期,这种降低毛利的办法真是令人难受,而且OSAT目前买TCB一般用于移动端等小面积、相对低功耗的处理器,这种应用的毛利实在没法和大芯片比,但是资本家为了不买全新的混合键合产线,还是咬牙接受了。

那么,那地球上有谁能肆无忌惮的上TCB呢?那当然是,我们,天天被人认为 的英特尔啦,英特尔拥有近 300 种 TCB 工具,远超过了英特尔的先进封装的需求,以至于英特尔在许多非高级封装应用中使用 TCB

,SemiAnalysis给出的理由很有趣,因为英特尔在高功率和高利润应用中占有很大份额,产量损失和可靠性问题远远超过了每单位封装工具的微不足道的摊销成本。这大概就是,毛利高的IDM的底气吧,地主家的余粮还是很多的

而且借助TCB,英特尔可以对自家的标准封装、2.5D 封装和3D封装使用相同的工具,前提是这些die使用的都是bump技术

这也解释了为什么,混合键合对bump几乎是降维打击,但是英特尔在混合键合上的动作却缓慢了,英特尔在TCB上积累十多年,投入了大量财力和研究,把bump上限拉到了混合键合的水平,不可能就弃之不用,而且对于英特尔来说,TCB的工艺更成熟,不需要新的投入,设备折旧也快做完了,对于毛利率来说是一个好事。还是文章开头的那个观点,这个行业都是要赚钱的,商业有时比技术更重要。

PS:另外某为和日月光在TCB上合作蛮深的,2020年年底还有谣传日月光在大陆给某为建设了封装厂,然后在2021年年底,日月光在行业景气度还很不错的情况下卖给智路资本4家工厂,结合智路资本以往的操作和后台,很难不联想呀

四.未来(这部分不少是推测!看看图个乐就好)

1.台积电的野望

前面我们一直在强调,成本、商业模式决定了很多这个行业很多的抉择与方向,TSV是一个3D封装领域几乎离不开的技术,一般来说狭义上的TSV是一种”后道“工艺,即它是在芯片做完之后,再做开孔、填孔,也就是说,芯片制造和TSV产生并不需要在一个公司手里

,而且目前这种方式制作的TSV还有上文说的这么多问题,你看啊,3D先进封装未来算是一个大肥肉,TSV问题这么多,我台积电有没有一种办法,解决了TSV的问题,这样大家就离不开我啦

当然有的,前面我们提到,TSV也分为在芯片上和在中介层上两种,在芯片内部做TSV的破坏性是很大的,需要芯片制作完成后再打孔。而台积电准备了一种”TSV-less“技术,”TSV-less“本质还是一种TSV,只是从”后道“变成”前道“工艺,有了解过3D NAND制备工艺的人应该知道在3D NAND的生产过程中,就会制造出从顶层到底层的深孔,然后用ALD、PVD等技术把这些深孔填充,起到的作用和TSV基本一样(其实他们这个也是一种TSV),但是不需要像狭义的TSV那样在完成制造之后再对晶圆做破坏性的操作。台积电的”TSV-Less“原理也是类似,在芯片光刻的过程中就把”TSV“给做出来,借助ALD、PVD这类沉积精度非常高的技术,可以沉积出孔壁光滑,深宽比大的通孔,这代来的优势是狭义上的后道TSV无法追上的。

这样子除了在技术上有优势,在商业上也很有好处,相当于客户对于台积电的依赖更深了,而且这个技术和F2F的晶圆键合天生很匹配,以前客户还能逃去外面做打通孔(指不定哪天还想换代工),后续封装也很方便就能找别人做,现在你想获得3D封装中最好的互联性能,那就乖乖的在台积电TSV-less+CoW 混合键合做一套吧把米都给我交了!

2.嵌埋式封装

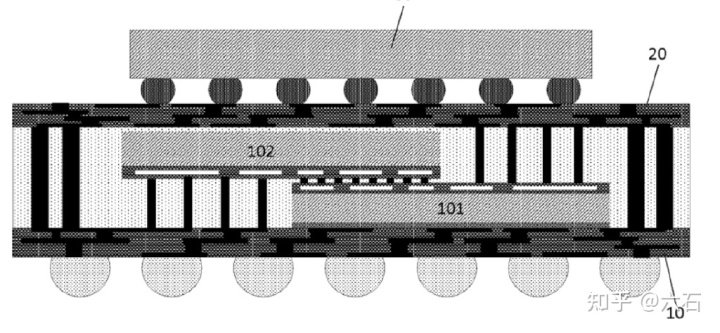

严格来说这不算是2.5D或者3D封装,也不是什么未来技术,嵌埋封装顾名思义,就是把die嵌埋到封装用的IC载板内部,这样的好处就是可以节省面积,方便小型化设计,在芯片的载板内部就集成了芯片所需外围器件,节约了主板的空间。嵌埋式封装的其实早在十几年前就出现了,但是在过往的应用中,嵌埋式技术主要是在载板中集成一些被动元器件或者电源管理芯片,将芯片放到下层层压基板之上,然后再制作镀铜的通孔和联线完成芯片的互联并用特殊的环氧树脂包覆芯片,之后再层压上上方的基板完成整块载板的制备,出售给客户的时候就是一块IC封装载板。由于工艺中存在各种各样的挑战(IC载板本身就很难做,嵌埋式的载板是半加成法制作,要求高),这项技术被归为比较小众应用,主要是一些电源管理芯片和蓝牙芯片(或许该叫模块,因为成品芯片自身就是一个包含了周边器件的模块)使用,几乎没有在数字芯片和大芯片领域见到。

除了工艺复杂的原因外,还有一个没有被推广开来的原因是嵌埋式封装的主推者大部分都是载板厂商,毕竟这最符合他们的商业利益,但是载板厂自身对die的封装积累不够深,使得客户也不敢把大芯片或者重要芯片交给他们做嵌埋,而封装普遍认为依靠RDL层代替载板做包覆/嵌埋芯片的载体更有前景也更符合利益(又回到我们开头说的第一点了)。而转机就在随着兼容PCB级别设备的面板级扇出工艺逐渐成熟,给载板厂带来了可以用的RDL工艺,解决了部分封装的难题,也带来远超传统嵌埋式互联方法的互联手段。

可能有人会说这不是某为前段时间3D堆叠封装的专利图吗?是的,不过我读完专利之后,觉得更像是一个堆叠式的嵌埋封装的专利,借由RDL技术,嵌埋式封装实现了一个创举,就是不再需要TSV就能实现堆叠芯片之间以及和外界的互通(毕竟载板本身上下就能通讯),前文我们也提过,TSV其实是一个令人又爱又恨的东西,有114514人想干掉它,而借助嵌埋封装,2.5D、3D封装是有可能去掉TSV的。当然,嵌埋封装如何用于大芯片这个问题应该还是没有解决,我个人倾向于某为这个专利是给可穿戴、物联网和电源管理类芯片准备的,上图顶上的芯片你把它想成是一个手表芯片,它的载板里借助嵌埋封装封装了原本在主板上的SRAM和电源管理芯片,现在一个芯片就成为一个可用的模块,剩下的空间给电池,不是美滋滋吗?

事实上,果子今年已经准备类似的封装了,联系了某载板厂,最快下半年就可能可以见到落地了,应该是应用在耳机上,把原本就很小的系统再缩小一点。另外,某为也一直在和某大陆载板厂合作搞嵌埋式封装,做的是一种类似Ti MicroSiP的产品,MicroSiP是嵌埋式领域最成功的一颗芯片(模块)了,借助嵌埋技术,TI将其电源管理IC嵌入到基板中,并将无源元器件安装在封装体的顶部,整个模块体积小的惊人,某某的基站我印象里好像用了不少。

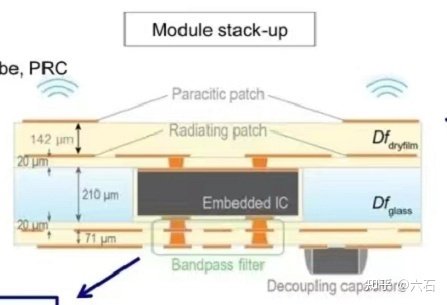

当然还有一种可能,这个技术是为射频领域准备的,射频领域对AiP、嵌埋式的探索一直没有停止,把天线、IC、各种滤波器、PA集成在一个模组甚至一个”芯片“(的载板)里一直是业界很想做到的,上图就是老美对5G射频IC的一个研究,它的形式就是把IC嵌埋在玻璃和层压载板中,同时载板上集成了很多器件。某为做做这类芯片,非常合理

3.14+14>7?

这部分我纯粹在”瞎扯“了,以下内容如让您感到乱说,以您为准,在说这部分前,有篇文章推荐大家看看,马恺声老师的《我亲历的Chiplet拆解难题》,他的这篇很好的探讨了chiplet、先进封装在实际应用中的遇到的种种情况和考量。然后以下是可看可不看的内容

当我们在讨论先进封装能不能1+1≥2或者14nm+14nm≥7nm的时候,其实有个潜在限定条件,就是这种芯片是通过多个die互联达成性能上对单一die芯片的追赶甚至超越的,而不是一个die+互联一块缓存这种形式,那其实可以把这个问题抽象成,落后制程芯片能否在先进制程芯片2倍的面积内集成相同的晶体管(或者是某落后工艺的密度X2能不能追上先进工艺)?假设不考虑功耗和发热,以100m㎡的芯片为例,14nm/16nm制程下,两块100m㎡做3D封装,完封后面积和一个100m㎡的7nm制程的芯片接近,其提供的晶体管数量能否接近甚至超越7nm?(按我印象,晶体管数量应该是介于10nm~7nm之间,如果换用10nm或者中芯的N+1是有希望接近7nm的,具体可以去翻MebiuW 的微博,他有详细统计各家的代工工艺节点),不过回到我们文章开头的第一个观点,这样做的代价是什么?理论是很美好甚至是可行的,但是实际上呢?还有发热、封装的良率、成本,甚至因为制程原因,芯片的运行频率也会降低,所以这种方式能在除了特定领域(信创、军工等)的市场上推广开来吗?我也不知道,留给时间来回答吧。

说回文章开头的第二个观点,2.5封装也好、3D封装也好,它并不是一种万能的灵丹妙药,不是说我今天上了先进封装,我就能化腐朽为神奇,你得先是个合格的芯片设计厂商,现有能力拿出合格的芯片,再用先进封装技术锦上添花,所以无疑某为绝对是国内甚至全世界前列的先进封装技术探索者和应用者,他们在材料和工艺上都有很深的布局,某思更是国内顶尖的芯片设计厂商,拿出过成功的先进封装应用,作为一个国人,肯定是希望他们最后能突破重重困难,成功破局的。

最后,半导体行业总是会有一些不符合”先进“、”反直觉“、甚至”落后“的东西被应用在量产产品之上,也有很多无比先进的东西最后一败涂地销声匿迹,这背后就是第一个观点所说的因素在推动,比如夏总有篇文章说到他们团队去北美推销ARM服务器芯片,亮点是功耗低,结果被甲方怼说我们要的是这点电费吗?要的是把电力尽可能变成算力(所以现在大家都”喜迎“he弹了),比如M1U亮相的时候,1.3TB/s的互联带宽让不少人奚落AMD ZEN系列那可怜的封装和IF总线,可是,AMD把一个CPU拆成不同部分,尽力解决了不同部分之间的同步、延迟,还把这个技术在载板上实现了带到了千元级别的产品上,这个技术真的那么”落后“吗?;比如20年前IBM的Cell,吹的秒天秒地,最后几乎身败名裂,但是今天放眼看去,怎么Cell那种架构思路又开始兴起,这是为什么捏?技术和商业交融,密不可分,互相影响和制约,这或许也是半导体行业的迷人之处吧。

好了,瞎扯的够多了,到这里结束了,下一篇可能是光电封装、射频封装,也可能是一些封装材料,或者是什么别的,最近正好迷上了图形学,听了点讲虎书的课,也顺手翻了翻以前顾杰老师讲GPU的一些东西,(我知道这图形学没关系但是费米架构好美啊 )anyway以后有缘再写半导体相关的东西吧,谢谢你看到这里~

参考文档

2.Signal Integrity of Submicron InFO Heterogeneous Integration for High Performance Computing Applications Chuei-Tang Wang, Jeng-Shien Hsieh, Victor C. Y. Chang, Shih-Ya Huang, T. Ko, Han-Ping Pu, and Douglas Yu

3.3D Multi-chip Integration with System on Integrated Chips (SoICTM) C.C. Hu, M.F. Chen, W.C. Chiou, Doug C.H. Yu

4.ISSCC 2022 Session2

5.https://mp.weixin.qq.com/s/p1za2O8ASg7R46JQncFYCA

6.https://mp.weixin.qq.com/s/rtsI0gAO35P9LIDQCEjlXA

原文始发于:先进封装杂谈——2.5D/3D先进封装