后摩尔时代,依靠缩小尺寸提升器件集成度的硅基CMOS技术面临物理原理和工艺技术的巨大挑战,具有高性能、低功耗和低成本优势的Chiplet技术成为延续摩尔定律的重要选择之一。该技术利用先进封装工艺,将多个异构芯片集成为特定功能的系统芯片,从而满足人工智能等领域的应用需求。但由于Chiplet异构集成密度大幅增加,热耗散问题对异构系统的可靠性造成严峻挑战。如何针对Chiplet异构集成系统的复杂性,提出新的热分析方法,实现高精准封装热模拟和散热结构设计,开发与Chiplet应用场景适配的热仿真模型和工具已成为Chiplet热分析领域的重要方向。

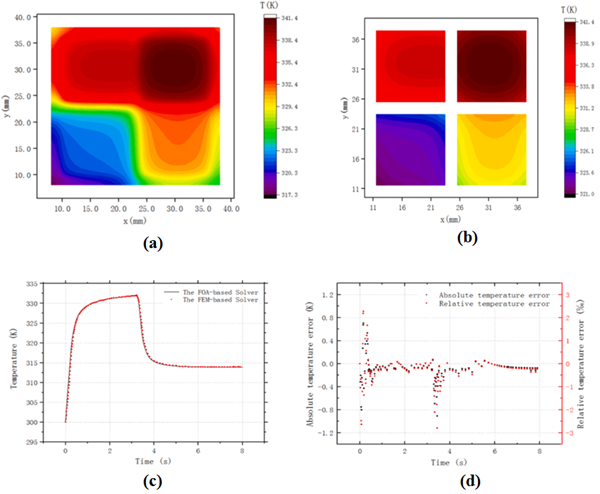

图1 四芯粒异构集成系统温度分布:(a) 中介层上表面温度分布; (b) Chiplet中心温度分布;(c) 中介层上表面温度与有限元仿真结果对比; (d) Chiplet热仿真模型误差

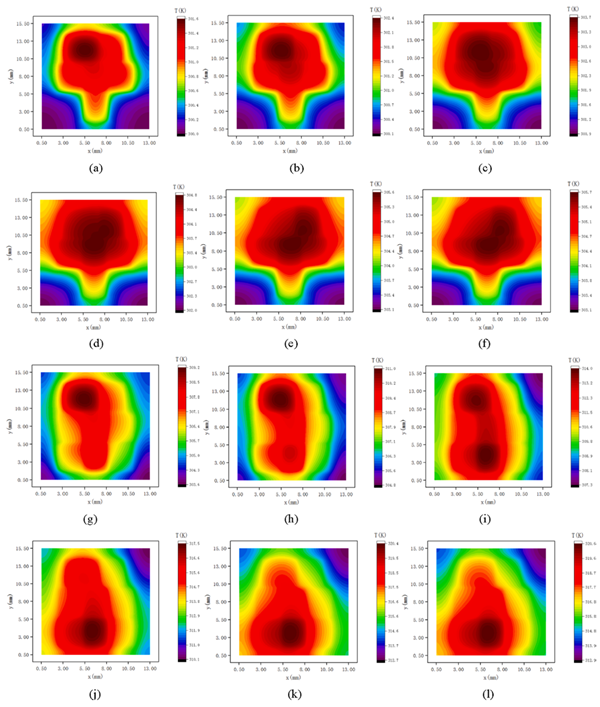

图2 一个典型Chiplet异构集成系统中介层上表面瞬态温度分布: (a) t = 0.1 s; (b) t = 0.2 s; (c) t = 0.5 s; (d) t = 1.0 s; (e) t = 3.0 s; (f) t = 5.0 s; ((a)-(f):状态1) (g) t = 5.1 s; (h) t = 5.2 s; (i) t = 5.5 s; (j) t = 6.0 s; (k) t = 8.0 s; (l) t = 10.0 s. ((g)-(l):状态2)

基于以上问题,微电子所EDA中心多物理场仿真课题组通过引入传导、对流和辐射效应,提出了芯粒异构集成复杂互连结构(TSV、bump和RDL)通用等效热导解析方法和一种改进型交替方向隐式浮点优化算法。通过快速精确求解超大规模稀疏矩阵离散方程,首次构建了芯粒异构集成三维网格型瞬态热流仿真模型和计算流程。在此基础上,课题组进一步将其拓展应用于更大规模和尺度的异构集成温度仿真。以上模型和求解器能够实现Chiplet异构集成系统瞬态热流的高效精确仿真,为芯粒异构集成系统温度热点检测工具和温感布局优化算法的开发奠定了核心技术基础。通过在芯粒热流仿真模型上改进数值离散格式和虚拟点构造算法,使浮点运算效率提升了2.74倍。与有限元方法相比,在满足计算精度的前提下,Chiplet热仿真器的计算效率提升了27倍。

该项研究得到了中国科学院战略性A类先导专项项目支持,研究成果先后发表于热力学领域顶级期刊《Applied Thermal Engineering》(Efficient Transient Thermal Analysis of Chiplet Heterogeneous Integration, DOI:10.1016/j.applthermaleng.2023.120609)和《Microelectronics Reliability》(DOI:10.1016/j.microrel.2022.114790; DOI:10.1016/j.microrel.2023.115006)期刊上。微电子所硕士生聂川俊、王成晗分别为上述论文第一作者,微电子所徐勤志副研究员为上述论文通讯作者。

来源:中国科学院微电子研究所

原文链接:http://www.ime.ac.cn/zhxx/zhxw/202305/t20230531_6765457.html