2023 年 7 月 10 日,应用材料公司推出的材料、技术和系统可帮助芯片制造商使用混合键合和硅通孔 (TSV) 将小芯片集成到先进的 2.5D 和 3D 封装中。 新的解决方案扩展了应用材料公司业界领先的异构集成 (HI) 技术范围。

HI 帮助半导体公司将基于各种功能、技术节点和尺寸的小芯片组合到先进封装中,使组合能够作为单一产品运行。HI 有助于解决行业挑战,部分原因是高性能计算和人工智能等应用对晶体管的需求持续呈指数级增长,而通过经典 2D 缩放缩小晶体管的能力正在放缓且变得更加昂贵。HI 是新剧本的核心组成部分,使芯片制造商能够以新的方式提高芯片性能、功耗、面积成本和上市时间 (PPACt)。

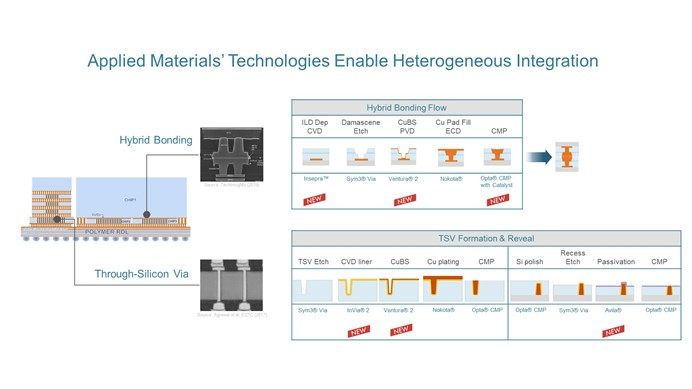

应用材料公司是最大的 HI 技术供应商,拥有优化的芯片制造系统,涵盖蚀刻、物理气相沉积 (PVD)、化学气相沉积 (CVD)、电镀、化学机械抛光 (CMP)、退火和表面处理。

应用材料公司半导体产品集团副总裁兼 HI、ICAPS 和外延业务总经理 Sundar Ramamurthy 博士表示:"异构集成正在迅速增长,因为它可以帮助芯片和系统公司克服经典 2D 扩展的限制,而传统 2D 扩展不再能够同时提高性能、功耗和成本。我们最新的 HI 解决方案推进了业界最新的方法,以 2.5D 和 3D 配置封装更多晶体管和布线,以提高系统性能、降低功耗、最小化尺寸并加快上市时间。"

使混合键合更可靠更高效

芯片到晶圆和晶圆到晶圆混合键合可用于使用直接铜到铜键合来连接芯片,使组合元件能够作为一个整体运行。 混合键合是当今业界最先进的 HI 生产技术,通过将更多布线装入更小的空间并减少信号需要传输的距离来提高吞吐量和功率。

Insepra™ SiCN 沉积系统扩展了应用材料公司行业领先的混合键合产品组合。 该系统采用新型氮化碳硅 (SiCN) 材料,可提供业内最高的介电结合强度,并提供卓越的铜扩散阻挡性能。 更强的介电键合为设计人员提供了在给定区域集成更多铜对铜互连所需的结构稳定性,从而降低了功耗并提高了器件性能。

Catalyst™ CMP 解决方案可帮助客户控制"凹陷"量,即铜材料在随后的高温退火步骤中粘合的两个表面上的有意凹陷。 CMP 凹陷会在铜焊盘的顶表面产生不必要的金属损失,从而产生气隙,从而降低铜与铜接合的保真度和强度。 应用材料公司的 Catalyst 解决方案是一种动态温度控制技术,可减少凹陷并提高产量。

将硅通孔提升到新高度

TSV 是用于精确连接堆叠芯片的垂直导线,已在大批量制造中使用了十多年。 它们是通过在硅中蚀刻沟槽,然后用绝缘衬里和金属线填充沟槽来形成的。 随着设计人员不断将更多逻辑、存储器和专用芯片集成到先进的 2.5D 和 3D 封装中,TSV 互连的数量已从每个封装的数百个扩展到数千个。 为了集成更多互连并容纳更高的芯片堆叠,设计人员需要使通孔变得越来越窄和越来越高,这会导致沉积均匀性变化,从而降低性能并增加电阻和功耗。

应用材料公司今天推出了介电和金属沉积新技术,可实现更高深宽比的 TSV,并帮助芯片制造商实现集成、性能和功耗目标:

Producer® InVia® 2 CVD 系统是一种新的 CVD 工艺,可在逻辑和存储器客户日益增长的各种 TSV 应用中所需的极端纵横比下,使电介质衬垫均匀且电气稳健。 InVia 2 系统采用适当的原位沉积工艺,可为高深宽比 TSV 提供出色的共形性。 该系统还提供比 ALD 技术更高的吞吐量,从而降低 TSV 的每晶圆成本,有助于进一步扩大其采用范围。

Endura® Ventura® 2 PVD 系统将其广泛采用的前身系统扩展到纵横比高达 20:1 的 TSV 应用。 Ventura 2 系统增强了对金属 TSV 线沉积的控制,以确保完全填充,从而提供高电气性能和可靠性。 新的 TSV PVD 工艺经过共同优化,可与 Producer® InVia® 2 CVD 工艺配合使用,为客户提供现成的解决方案来应对最具挑战性的 TSV 设计。 所有先进代工/逻辑芯片制造商和所有主要 DRAM 生产商都在部署 Ventura 2 系统。

应用材料公司的最新一代 Producer® Avila® PECVD 系统专为 TSV"揭示"应用而设计。 在 TSV 工艺流程中,晶圆被键合到临时玻璃或硅载体上,然后使用 CMP 和蚀刻进行减薄,以使 TSV 易于使用。 在 TSV 揭示步骤之后,使用等离子体增强 CVD 技术沉积薄介电层,使 TSV 彼此电隔离。 如果 PECVD 工艺产生的热量高于约 200o C,脆弱的临时粘合粘合剂可能会损坏,导致晶圆产量损失惨重。 应用材料公司的 Producer Avila PECVD 系统可在超低温和高速下制造高质量介电薄膜,满足 TSV 质量和成本所需的低热预算和高生产率。