11:08,仪式正式开始。晶瑞电材董事长李勍在欢迎词中指出:晶瑞湖北公司是未来集团公司最大的综合产品制造基地,涵盖高纯湿电子化学品及光刻配套材料等产品。湖北省九省通衢,未来公司产品可辐射供应华中地区乃至华中、华南地区的半导体及光电显示客户。该项目的正式投产,将进一步提升公司在半导体、面板显示领域内的综合实力:一是扩充产能以满足中国急剧增长的市场需求,二是不断创新更高技术水准的产品以解决更多的卡脖子产品。同时,借助湖北省长江产业基金和潜江市政府在资本、土地、政策以及上下游资源的大力支持,公司将努力打造一个有多项产品技术水平达到国际一流的企业,积极履行社会责任为客户创造更高价值,为地方社会经济高质量发展激活新引擎、增添新活力。

(晶瑞电材董事长李勍致辞)

(晶瑞电材董事长李勍致辞) (赠礼环节)

(赠礼环节) (潜江市委书记向斌致辞)

(潜江市委书记向斌致辞)

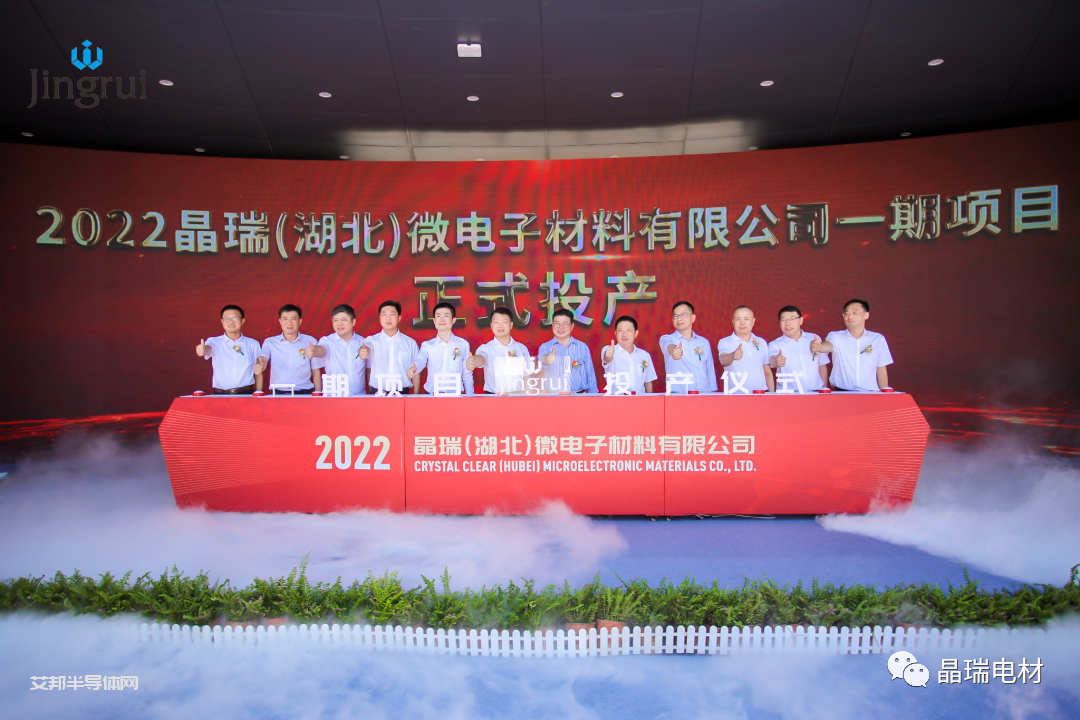

晶瑞湖北公司简介

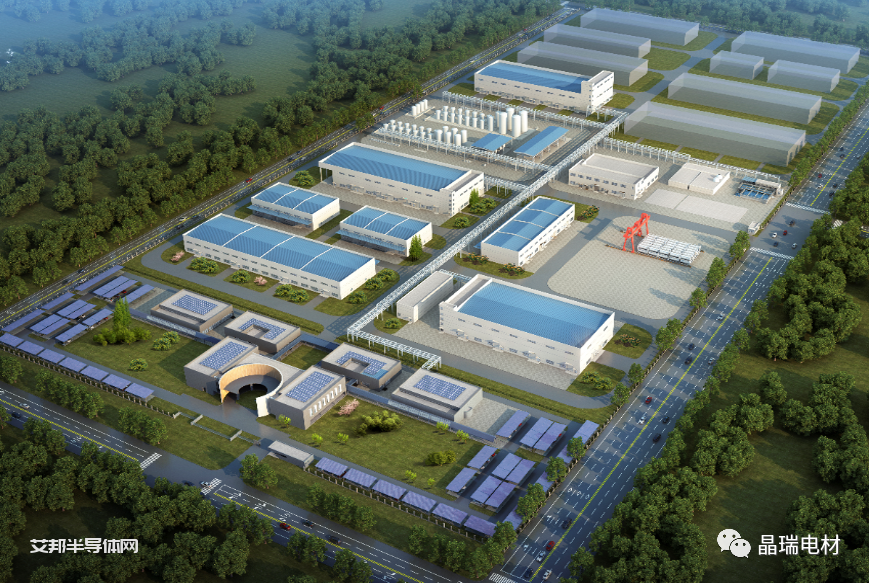

晶瑞(湖北)微电子材料有限公司位于潜江市江汉盐化工业园,成立于2019年11月13日,是上市公司晶瑞电材(股票代码:300655)协同湖北长江(潜江)产业发展基金共同创建的微电子材料项目。

公司主要生产G5级别超高纯电子化学品、光刻胶及其配套的功能性材料,广泛应用于半导体、面板和新能源等行业。公司是晶瑞集团重要的战略基地,立足湖北、服务华中、辐射全国,将为高端电子化学品国产化、完善中国先进制造产业链作出积极贡献。

原文始发于微信公众号(晶瑞电材):【集团动态】全新起航!热烈庆祝晶瑞湖北公司一期项目投产仪式圆满举行

一颗芯片的制造工艺非常复杂,需经过几千道工序,加工的每个阶段都面临难点。欢迎加入艾邦半导体产业微信群:

长按识别二维码关注公众号,点击下方菜单栏左侧“微信群”,申请加入群聊

应用终端 芯片设计 设备 晶圆 检测设备 视觉 自动化 半导体 芯片 封装 芯片测试 材料 设备配件 传动机构 清洗设备 化学品 塑料 硅片 光掩膜版 磨抛耗材 夹治具 切割设备 激光设备 光罩盒 IC载板 载具 CMP抛光垫 光学元件 抛光液 模具 电子特气 蚀刻设备 光刻胶 靶材 塑料制品 耐酸碱 管道阀门 氟材料 光刻机 环氧塑封 特种塑料 涂层 耗材 晶体生长炉 热工装备 划片机 磨抛设备 化学机械抛光设备 离子注入设备 PVD 涂胶显影设备 等离子去胶设备 胶带 清洗剂 包装设备 包装 管路 抗静电剂 陶瓷 元器件 碳碳制品 高校研究所 代理 贸易 其他 CVD 光源 胶水 载带 玻璃 有机硅 薄膜 密封圈