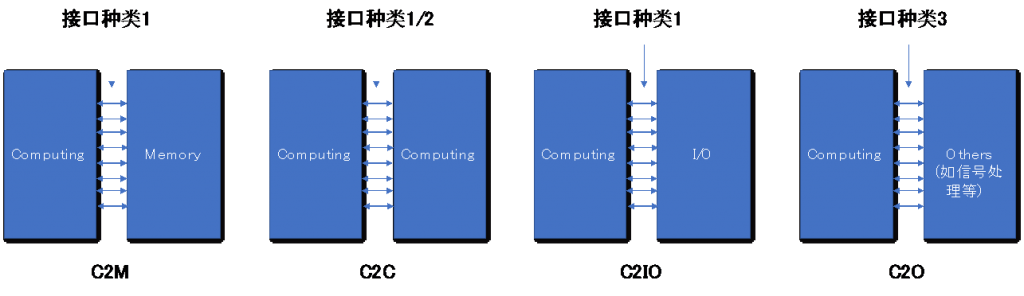

在制程工艺难以进步的情况下,Chiplet小芯片架构可以实现晶体管密度的突破,因此对于半导体行业来说非常重要。目前,英特尔、AMD、ARM等芯片巨头均已推出Chiplet小芯片架构,但是本土半导体厂商在这一领域仍比较欠缺。

因最近微信公众平台推送规则改变,很多读者反馈没有及时看到更新的文章。根据最新规则,建议多点击“推荐阅读、分享、收藏”等,成为常读用户。

推荐阅读:

原文始发于微信公众号(21ic电子网):突破!中国首个原生Chiplet小芯片标准来了

一颗芯片的制造工艺非常复杂,需经过几千道工序,加工的每个阶段都面临难点。欢迎加入艾邦半导体产业微信群:

长按识别二维码关注公众号,点击下方菜单栏左侧“微信群”,申请加入群聊

应用终端 芯片设计 equipment wafer 检测设备 视觉 自动化 半导体 芯片 封装 芯片测试 material 设备配件 传动机构 清洗设备 化学品 Plastic 硅片 光掩膜版 磨抛耗材 夹治具 切割设备 激光设备 光罩盒 IC载板 载具 CMP抛光垫 光学元件 抛光液 模具 电子特气 蚀刻设备 光刻胶 靶材 塑料制品 耐酸碱 管道阀门 氟材料 光刻机 环氧塑封 特种塑料 涂层 耗材 晶体生长炉 热工装备 划片机 磨抛设备 化学机械抛光设备 离子注入设备 PVD 涂胶显影设备 等离子去胶设备 胶带 清洗剂 包装设备 包装 管路 抗静电剂 ceramics 元器件 碳碳制品 高校研究所 代理 贸易 其他 CVD 光源 胶水 载带 玻璃 有机硅 薄膜 密封圈

先进封装设备类似前道晶圆制造设备,供应商受益先进封测产业增长。随着先进封装的发展,Bumping(凸块)、Flip(倒装) 、TSV 和 RDL(重布线)等新的连接形式所需要用到的设备也越先进。以长球凸点为例,主要的工艺流程为预清洗、UBM、淀积、光刻、焊料 电镀、去胶、刻蚀、清洗、检测等,因此所需要的设备包括清洗机、PVD 设备、光刻机、 刻蚀机、电镀设备、清洗机等,材料需要包括光刻胶、显影剂、刻蚀液、清洗液等。为促进行业发展,互通有无,欢迎芯片设计、晶圆制造、装备、材料等产业链上下游加入艾邦半导体先进封装产业链交流群。