本文由半导体产业纵横(ID:ICVIEWS)编译自tomshardware

英特尔的 IEDM 2022 研究论文讲述了有前途的新技术。

英特尔在IEDM 2022上发布了九篇研究论文,为未来的芯片设计奠定了基础,该公司有望兑现到2030年开发超过万亿晶体管处理器的承诺。

研究包括用于晶体管的新 2D 材料、新的 3D 封装技术将小芯片和单芯片处理器之间的性能和功率差距缩小到几乎无法察觉的范围,断电时“不会忘记”的晶体管,以及可以直接堆叠在晶体管顶部并存储多个的嵌入式存储器每个单元位,以及其他创新。

英特尔的组件研究 (CR) 小组为公司的未来技术奠定了初步基础,但并非所有这些举措都会导致产品上市。那些真正上市的产品通常会在五到十年内上市。

该团队在已经上市的创新方面有着令人难以置信的记录,例如彻底改变整个行业晶体管设计的 FinFET、应变硅、Hi-K 金属栅极等。英特尔的路线图上已经有其他几项技术,包括RibbonFET Gate All Around (GAA) 晶体管、PowerVia 背面供电、EMIB 和 Foveros Direct,它们都来自该研究小组。

该小组在今年的第 68 届年度 IEEE 国际电子设备会议上提交了九篇研究论文,下面我们将稍微详细地介绍其中的几篇。

来源:英特尔

晶体管密度的增长速度大致符合摩尔定律,但当今芯片的经济性并没有以同样的速度提高——随着我们转向更密集的节点,每个晶体管的价格正在上涨。此外,一些芯片元件(如模拟和缓存)的扩展性差,使事情进一步复杂化。因此,该行业正在集体转向基于小芯片的高性能芯片设计。

任何基于 chiplet 设计的首要目标是在利用基于 chiplet 的方法的经济效益的同时,保留单芯片单片处理器内部数据路径的功耗和性能(延迟、带宽)的最佳属性,例如采用前沿工艺制造的较小芯片提高产量,以及使用较成熟、较便宜的节点来实现密度改进较小的其他一些功能的能力。

因此,半导体霸权的战场正在从晶体管的速度转移到互连的性能,硅中介层 (EMIB) 和混合键合技术等新技术成为提高经济性的前沿。

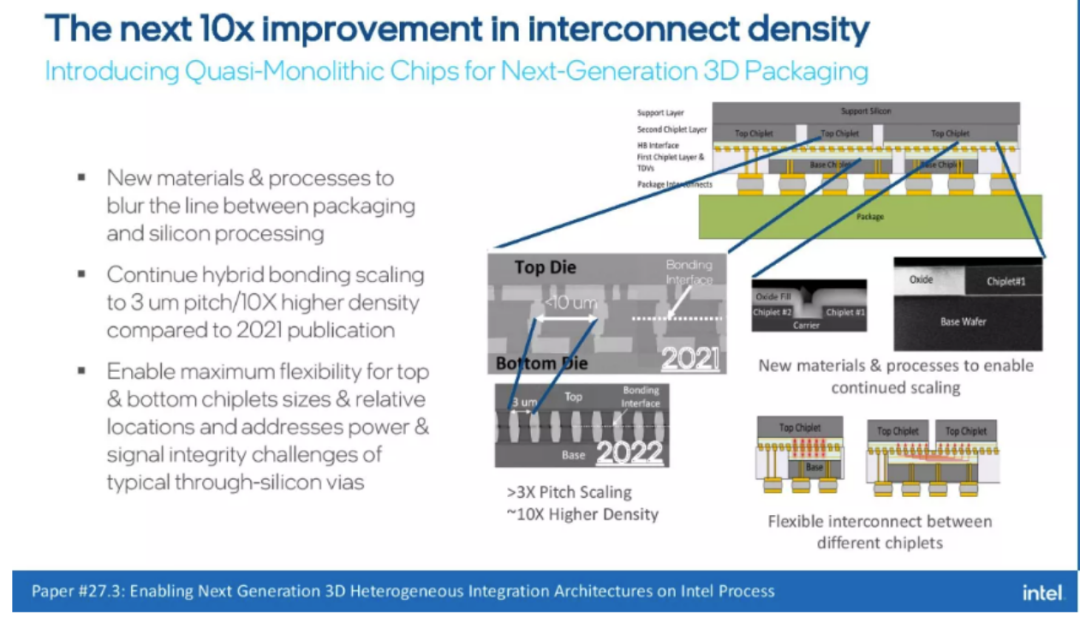

这些方法仍然会导致不可避免的性能、功耗和成本权衡,英特尔新的“准单片芯片”(QMC) 3D 封装技术希望解决这个问题。顾名思义,英特尔的 QMC 旨在提供与内置在单个芯片中的互连几乎相同的特性。

QMC 是一种新的混合键合技术,其间距小于 3 微米,与英特尔在去年 IEDM 上提交的研究相比,能效和性能密度提高了 10 倍。之前的论文涵盖了一种 10 微米间距的方法,这已经是 10 倍的改进。因此,英特尔在短短几年内找到了实现 100 倍改进的途径,表明该公司在混合键合方面的工作正在迅速加速。QMC 还可以让多个小芯片相互垂直堆叠,如上图所示。

文章概述了令人难以置信的每平方毫米数十万个连接的互连密度和可与我们在单片处理器中看到的相媲美的功耗(以每比特皮焦耳 - Pj/b 为单位)。此外,新论文概述了几种可用于制造此类设备的新材料和工艺,为现实世界的设备铺平了道路。

英特尔的工艺路线图已经下降到纳米级以下到埃级,尽管节点命名惯例早就与晶体管的实际物理测量失去了联系,但很明显,需要一种全新的方法来继续扩展。大多数行业都押注未来会转向 2D 原子通道,但与所有新技术一样,要实现这种根本性的改变需要很多步骤。

今天的芯片材料,如硅,由三维晶体组成,这意味着原子在所有三个维度上都结合在一起,从而对收缩提出了基本限制。相比之下,二维材料很有吸引力,因为所有的原子都键合在一个平面上,因此可以用小至三个原子的厚度来构建特征。

英特尔对2D材料的研究,也可以用于3D GAA晶体管。当前的 GAA 设计由堆叠的水平硅纳米片组成,每个纳米片都被一个门完全包围。这种“环栅”(GAA) 技术可减少防止晶体管关断的电压泄漏。随着晶体管的缩小,这变得越来越成为一个问题——即使当栅极在三边围绕沟道时,正如我们在 FinFET 晶体管中看到的那样。

英特尔将其 GAA 设计命名为 RibbonFET,目前计划于 2024 年上半年推出。然而,超越 RibbonFET 将需要进一步的创新,而这项 2D 研究符合潜在途径的要求。

英特尔的论文描述了一种全环绕栅 (GAA) 堆叠纳米片结构,其通道材料(纳米片/纳米带)厚度仅为三个原子,可以在室温下以低漏电流运行。

二维通道材料的厚度使得建立与纳米带的电连接成为一项艰巨的任务,因此英特尔还为二维材料建立了电接触拓扑模型。这是了解二维材料的特性及其功能的关键一步,从而使公司能够准确地模拟进一步的进步。

各种形式的内存都是计算不可或缺的一部分,但它也在芯片和系统级别消耗大量功率预算,同时也是性能的限制因素。

英特尔还进行了世界上第一个 3D 堆叠铁电存储器的功能演示。这项技术最令人印象深刻的方面是铁电沟槽电容器可以垂直堆叠在晶体管顶部的逻辑芯片上。这使得能够将存储器分层在逻辑元素之上,而不是像我们在其他类型的嵌入式存储器中看到的那样,将其置于其自己的不同区域中,例如用于 L1 和 L2 缓存的 SRAM。

铁电存储器还具有与我们在 NAND 闪存中看到的类似的功能——能够在通常只存储一位的结构中存储多位数据。在这种情况下,英特尔展示了每个沟槽存储四位的能力。

自然地,这种方法会增加带宽和内存密度,同时减少延迟,从而产生更大更快的片上缓存。

与二维结构的电接触建模一样,英特尔还分享了其对铁电氧化铪器件的混合相和缺陷的建模工作,这反过来将进一步推动公司自身的研发过程。

英特尔还在研究“不会忘记”的晶体管,这意味着它们在断电时不会丢失数据(开/关状态)。这类似于任何非易失性存储器,如 NAND,它可以在断电时保持其状态,但它以逻辑晶体管的形式出现。英特尔表示,它已经克服了在室温下使用该技术的三个障碍中的两个。我们特别期待这次演讲。

英特尔在此次活动中的其他论文概述了其他研究领域,如硅片上的氮化镓(GaN),可以实现5G以外的未来技术,以及存储量子信息的更好方法,为量子计算创造更好的量子比特。

原文始发于微信公众号(半导体产业纵横):英特尔:2D 晶体管材料,3D 封装研究

成员: 5306人, 热度: 153517

ceramics 天线 通讯 终端 汽车配件 滤波器 电子陶瓷 LTCC MLCC HTCC DBC AMB DPC 厚膜基板 氧化铝粉体 氮化铝粉体 氮化硅粉体 碳化硅粉体 氧化铍粉体 粉体 生瓷带 Ceramic substrate 氧化铝基板 切割机 线路板 铜材 氮化铝基板 氧化铍基板 碳化硅基板 氮化硅基板 玻璃粉 集成电路 镀膜设备 靶材 电子元件 封装 传感器 导电材料 电子浆料 划片机 稀土氧化物 耐火材料 电感 电容 电镀 电镀设备 电镀加工 代工 等离子设备 贴片 耗材 网版 自动化 烧结炉 流延机 磨抛设备 曝光显影 砂磨机 打孔机 激光设备 印刷机 包装机 叠层机 检测设备 设备配件 添加剂 薄膜 material 粘合剂 高校研究所 清洗 二氧化钛 贸易 equipment 代理 其他 LED