文章搬运自我自己的微博(ID:giratinar)

抛砖隐喻,扯一扯扇出封装技术,包括了一些自主化情况和行业情况

闲扯聊一聊一个已经应用比较广的先进封装——Fan-Out晶圆级扇出封装和台积电的InFO封装(面板级扇出见上一篇文章)

文章大体分为4个部分

一.扇出封装的定义

二.扇出封装的意义

三.扇出封装的难点和大陆没有突破的部分

四.以大陆企业为例,闲聊一下扇出封装的几个变种

五.台积电InFO封装

PS:本文仅仅是抛砖引玉,很多东西有兴趣可以自行了解,欢迎交流。读本文需前置了解的概念:1.WLP晶圆级封装、2.扇入、扇出大概是啥东西,尤其是扇入,本文默认大家都懂是啥。因为限于篇幅,这里就不写这些前置信息了(主要是懒,文章在动车上写的)

一.扇出封装的定义

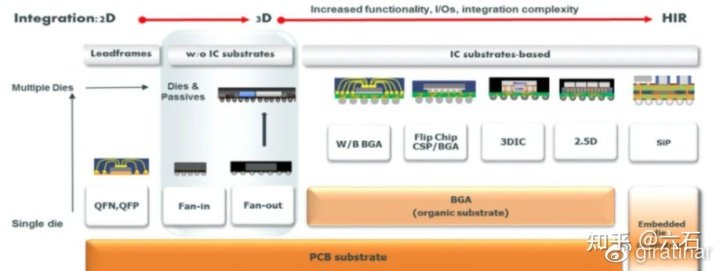

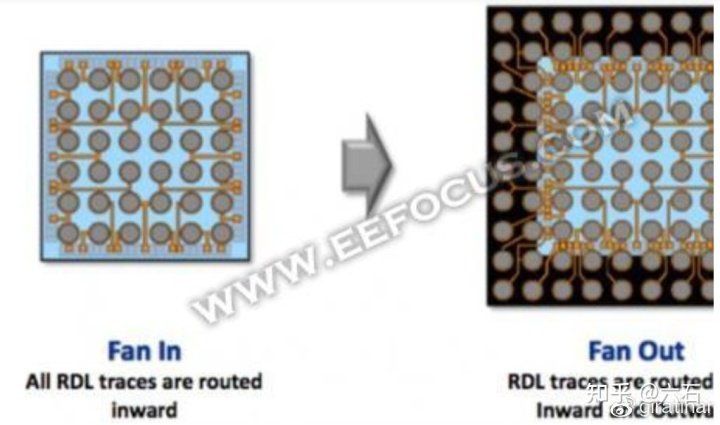

扇出和半导体行业很多概念一样,有广义和狭义等不同定义,广义上说,只要是封装面积比die的面积大,且die上的布线有被引出来的非WLP扇入型封装(废话),都可以叫做扇出封装(甚至引线框架封装,你也可以说是扇出封装),也有不少行业老兵会把BGA/PGA叫做扇出封装——很明显,借助基板(上图中绿色那一层),这些封装也实现了把线从die上引出来这件事。

但狭义上来说,扇出封装一般是指,晶圆级/面板级封装下,封装面积与die不一样,且不需要基板的封装,也就是我们常说的FOWLP/FOPLP。(实际上扇出封装发展到今天从早期的单die到多die处于同一个封装下,已经出现了使用基板的分支,所以对于多die封装来说,应该是指“不需要基板而是依赖RDL重分布层实现同一个封装内die之间的通信”)

扇出封装(下文所有扇出封装都是指狭义上的晶圆级扇出封装,面板级不讨论,有兴趣翻我上一篇文章)本身不是一个新技术,它的技术雏形甚至早期应用在十几年前就被提出且进行了商业化,扇出封装的核心要素就是芯片上的RDL重布线层,通过RDL替代了传统封装下基板传输信号的作用,使得扇出封装可以不需要基板而且芯片成品的高度会更低,所以扇出封装的发明初衷其实是降低成本(基板和框架都不便宜,像今年ABF基板还疯狂缺货),而且由于扇出封装在封装面积上没有扇入那么多限制,整个封装设计也会变得更加灵活和“自由”。因此扇出封装最先在一些小面积、低性能的领域被推广开来。

随着扇出封装技术自身的发展,越来越多人认识到这个技术不应该只用于低成本低性能领域,它有巨大的潜力,在行业公司不断努力的推动下,扇出封装今天已经成为了先进封装技术的代表之一,已经可以被广泛用于高性能领域。

二.扇出封装的意义

对于先进封装,首先提两个观点:1.封装技术演进的本质是对I/O密度的追求,2.套用功率器件领域的一句话来说,芯片设计已经快玩到“头了”(摩尔定律走到了深水区+设计上也很难有翻天覆地的突破了),该在封装上下功夫了。

我们所有人都听过木桶效应,木桶里最短的那块板,会决定木桶储水量的上限,封装好的芯片其实也是一个木桶,而封装作为芯片和外接通信的直接桥梁,时常扮演了短板的角色。

为什么封装会成为短板?抽象来说就是I/O密度不足了,我们知道芯片是nm级别的工艺,基板等封装载体是几十μm的级别,随着芯片缩小+性能提升,WLP/CSP这类封装的I/O密度已经无法满足需求了,道理也很简单,基板等载体布线间距无法再更小了,也就是放不下了,而扇出封装在这时候提供了一种比高层数大面积ABF基板(高层数ABF基板良率常常不到50%,材料供应商还只有一个,现在你知道为啥它天天缺货了吧)更为经济适用、面积灵活、支持多die封装且布线密度更高(意味着die之间的距离可以更进,直观一些可以看看大基板MCM封装代表锐龙5000的CCX和IOD之间的距离和InFO-MCM代表苹果M1上SoC和DRAM的距离)的选择,而且这还是不需要引入中阶层(2.5D封装)就可以实现的,所以行业里一下子发现,扇出封装,有搞头!

扇出封装非常简单粗暴,既然放不下那么多焊球等东西导致I/O密度不够,那我就扩大面积,借助RDL把线引到外部,这样我就能放下足够多的焊球提升I/O密度。RDL层的制作类似于半导体制程,需要引入光刻、刻蚀、沉积等工艺,这意味着它的布线密度增加的空间远大于基板,事实上高密度且连接多die的RDL层已经可以被看做近似2.5D封装中的中介层的东西(日月光在一些场合已经这么叫过了),当然相比使用CMOS工艺的中介层和硅桥,RDL还是差了一口气。

目前扇出封装主要分为低密度(或叫标准密度)扇出式封装,一般指的是I/O数量小于500个、RDL层线宽和间距大于8μm的封装类型。而高密度扇出封装I/O数量超过500个,RDL层线宽间距小于8μm(目前已经可以缩小到2-5μm),同时这类高密度扇出封装可以集成多个die,甚至有的需要基板且性能指标与2.5D封装无异,而台积电的InFO技术是高密度扇出封装中最典型的例子。具体扇出封装的作用,会放在四、五部分结合实例来说。

三.扇出封装的难点

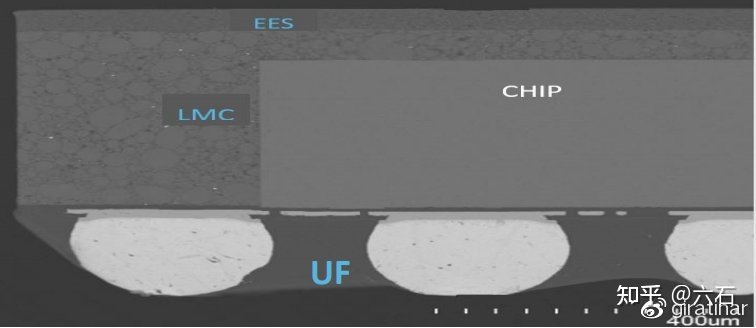

上图是一个台积电InFO封装的剖面图,可以看到扇出封装并没有使用基板,顶上也没有散热盖之类的东西,它的主体结构是通过周围一圈环氧树脂和顶上的环氧树脂膜完成支撑和散热的,这带来了一个问题,因为EMCLMC远不如基板来的牢靠,封装过程中很容易出现翘曲,进而影响良率,整个扇出封装流程中的很多难点都是围绕这一问题产生的。(所以到现在为止,不使用基板的扇出封装大部分只被使用于15mm*15mm以内的封装,再大的封装还是会回归传统的FCBGA)

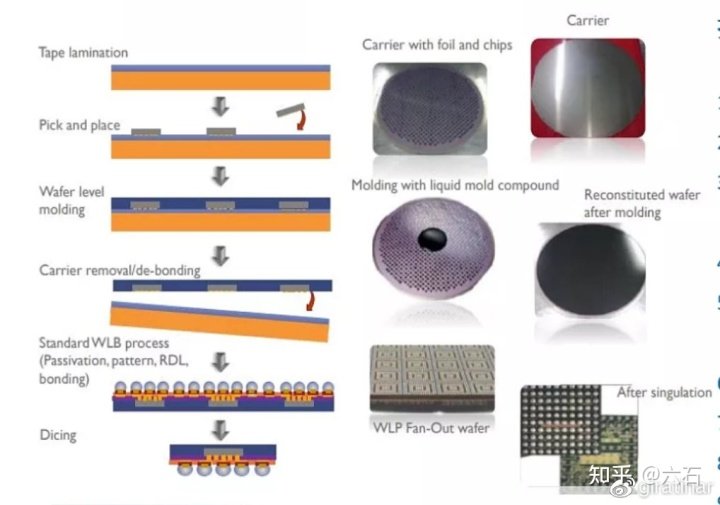

结合到具体生产中,晶圆级扇出封装需要经历过多次转移,根据工艺流派还可以分为die-down、die-up(主要是华天+台积电+ASE)、chip-first、chip-last,这四个工艺流程也不是完全互相排斥,会相互组合,比如既可以是die-down+chip-last,也可以是die-down+chip-first,具体有兴趣的可以自行看资料,这里就不一一展示了,总之die down/up指的是die被EMC包覆要布置引线那面的朝向,chip last/first指的是先做RDL层然后贴上包覆后完工的chip还是在完工后的chip上直接做RDL层。下面以一个die-down&chip-first的扇出封装为例:

先将做好的wafer切割,然后在拥有保护胶带贴膜的临时载体上进行RW(重新排列die),之后使用环氧树脂进行molding成型,再移除临时载体,制作RDL层,然后再植球+切割,封装就算完成了。在这几步工序中RW的精度会影响后续操作的良率、临时载体好不好剥离会影响chip会不会有翘曲、胶带不够牢固也会影响芯片出现die-shift和翘曲、Molding好坏也会影响chip的翘曲。当这些工作完成后,如何在一个晶圆大小的区域上制作出对准die的RDL层,对检测和对准精度也是一个巨大挑战。

就目前来说,中国大陆企业已经在低密度的扇出封装领域有所突破,在高密度高性能扇出封装上,还落后于中国台湾的日月光、台积电以及三星和安靠等一线大厂。而在设备和材料上,主要缺乏的设备是高精度的检测设备与RW设备,RW设备需要非常高的贴装精度,大陆暂时缺乏供应商。而材料方面,主要缺乏好的临时载体、热剥离膜和相应的剥离工艺、好的固晶胶膜(华为投了一家)、半导体级别的EMC和LMC(尤其是后者,虽然我们是EMC产出大国)、underfill(目前还是以汉高为主,烟台德邦正在攻坚这一领域)、EES(不难,但是大陆目前做的厂商很少,生益电子在进入这一市场)等。

四.以大陆企业为例,闲聊一下扇出封装的几个变种

鉴于一些原因,不太好把一些企业的资料放在网上,就以华天和云天两家公开展示过扇出封装技术的公司,闲聊一下扇出封装的几个变种。

我们之前说到,扇出封装下die的包覆物是EMC,在结构强度上有一定的缺陷,在面对封装多芯片和大面积芯片时候有点力不从心,所以衍生出了用硅来包覆(华天)和用玻璃来包覆(云天)两个细分的技术路径,至于使用基板的扇出封装如FCoS和InFO-oS我们留到下一篇2.5D/3D封装再讨论。

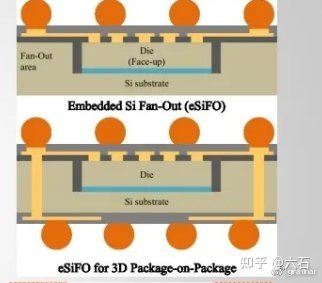

这是华天的eSiFO扇出封装,中间蓝色部分是TIM导热材料,可以看到原本EMC部分被换成了硅,整个封装也是通过在废弃硅片上刻蚀出洞然后把die嵌埋进去实现的。好处是啥呢?首先我们知道硅比EMC强度高很多,所以这种封装就极大避免了芯片的翘曲,提升了良率,让多芯片封装的难度降低,同时硅还是一个比EMC好太多的导热介质,散热压力也小了,还方便做TSV这类的垂直方向上的通孔。既然这么好为什么没有普及?当然是因为太贵了呀,硅片成本怎么都比EMC要高,而且工序复杂了很多,所以这个技术能不能大面积应用,还要打一个问号。

既然有人用硅,那就有人用玻璃,厦门的云天半导体就开发了eGFO嵌入式玻璃封装技术(本来想放图突然发现它官网给这个成品图都打码了,还是算了),玻璃其实是一个很好的载体,它绝缘性好,高温下也不容易膨胀,还可以透光,天生适合高频的射频应用和光电应用。高频下信号会有趋肤效应,硅不是彻底的绝缘,因此高频应用下比如毫米波应用中做TSV(硅通孔)会成为一个令人头疼的问题,而玻璃这种绝缘性的衬底上做TGV(玻璃通孔)是一个极佳的替代品,同时玻璃上可以直接做光路,满足光电共封装的需求,所以云天这个eGFO的技术,初衷也是冲着射频和光电领域的应用去的。但是玻璃有个巨大的问题,就是容易裂,因此在玻璃上开孔和挖出嵌埋区域是很难的,效率比较低下,良率也是一个巨大的问题,这是用玻璃做载体的最大拦路虎。

五.台积电InFO封装

为啥要单独把台积电的InFO封装拿出来说?因为InFO封装对行业的影响还是比较重大的,在InFO之前,扇出主要是用于单芯片+低成本封装,台积电作为一个Fab厂,上演了一出我来指导你怎么做扇出封装的好戏,把扇出变成了一个可以封装多芯片也可以用于高性能高I/O密度应用的东西,拔高了整个扇出封装技术的逼格。

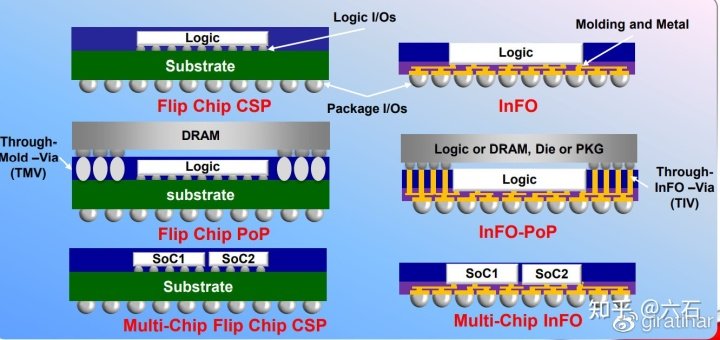

这张图左边是传统的FCCSP封装家族,可以看到,对比FCCSP,InFO封装之后,芯片的厚度大大降低了,而且不需要基板(绿色部分)这在一些领域,比如手机中,是非常吸引厂商的,事实上InFO的成名作就是苹果处理器上的InFO-POP, 台积电在InFO-POP上实际只做上图中的下半部分,顶上的DRAM等别的chip是交由别的OSAT厂商封装,一般为了节约成本,上半部分会使用FCCSP封装。对比传统的POP封装,InFO-POP封装除了厚度降低以外,还有个巨大的作用就是提升内存性能。传统的POP封装下,DRAM传输数据是要经有基板,而在InFO-POP下,则是经有RDL直接传到SoC上,距离和信号衰减都要好很多。而InFO-MCM,最经典的应用就是用M1上,苹果借助这个技术实施了统一内存架构。

放一个简单的对比图,台积电的InFO一经推出就获得成功不是偶然的,InFO封装Molding部分使用的不是常见的EMC,而是一种特殊的半导体级别的LMC(液态环氧树脂),目前这个材料只有日本的几个厂家能做,RDL层则用了一种的特殊的polymer,它是透明的,方便对位和光刻,同时所有InFO封装项目都会芯片客户进行深入合作,为客户的需求提供非常定制化的服务,以求满足性能上的需求。比如苹果的A系列处理器,苹果在InFO封装材料上有巨大的话语权,指定了包括underfill在内非常多关键材料的供应商,并指导了台积电怎么使用(PS:苹果在半导体和电子材料领域的积累是外人想不到的深厚),说白了就是台积电你做的已经很好了,但我苹果爸爸觉得你应该按我说的这样做

结语:先进封装的意义不用我再强调的,扇出封装会和2.5D/3D封装以及SiP、AiP相互交融,构成超越摩尔的重要组成部分。目前大陆虽然在先进封装上有差距,但无论是整体技术储备还是自主化率都有很不错的底子,这周刚去某厂交流过,在WLP设备和材料上,他们给了一个让我很吃惊的国产化率,这离不开无数技术人员夜以继日的攻坚。

同时我们也需要明白,世界上没有魔法,更没有完美的东西,一切商业化的半导体技术都是为了降低量产下完成某个目标的成本,下一篇我会聊一聊2.5D/3D封装,说说这个最高大上的封装的商业化难点和英特尔与台积电的路线之争。

PS:这篇文章比较早期,如今InFO-LSI(苹果M1U用的)、InFO-oS等等已经商用,这些属于2.5D封装范畴,详见另一篇文章

原文始发于:先进封装杂谈之扇出封装