共读好书

第一章 Patent Issues of Fan-Out Wafer-Level Packaging

1.1简介

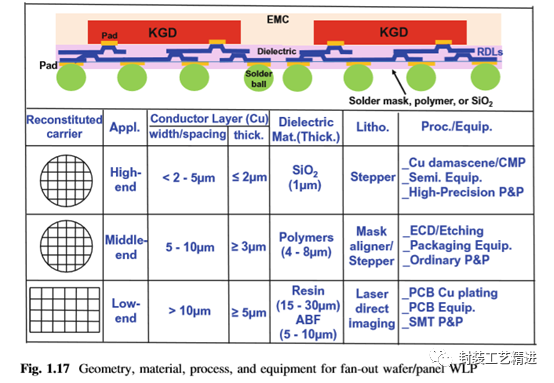

在行业,研究所和大学中,有许多工程师,研究人员,学生和教授从事扇出晶圆级封装的工作。为了避免获得该领域的专利,他们正在尝试各种方法,例如die-up, die-down, die-first, die-last, RDL(redistribution layer)-first, RDL-last, mold-first, mold-last, round temporary carrier, and rectangular temporarycarrier.。在本章中,将研究扇出晶圆/面板级封装的专利问题。重点将放在授予专利的权利要求以及专利可能涵盖的范围内。根据RDL线宽/间距,检查了扇形晶圆/面板级包装的材料,工艺,设备和应用,并提出了一些建议。迄今为止,将最先提及对半导体封装影响最大的专利。

1.2 半导体封装的功能

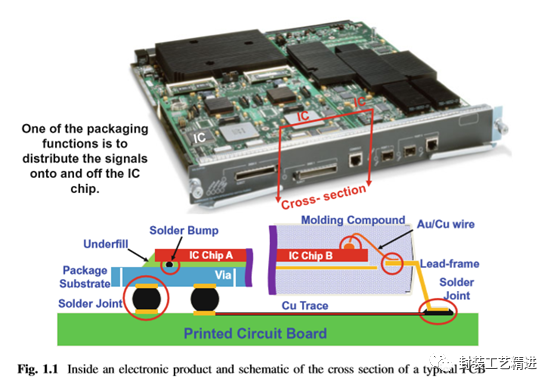

图1.1显示了典型电子产品的内部。它由带有某些半导体集成电路(IC)芯片组件的印刷电路板(PCB)组成。IC芯片不是孤立的孤岛,它必须通过互连的输入/输出(I / O)系统与电路中的其他IC芯片进行通信。此外,IC芯片及其嵌入式电路非常脆弱,要求封装既要携带也要保护它。因此,半导体封装的主要功能例如是:

(1)为电流提供路径,该电流为IC芯片上的电路供电;

(2)将信号分配到IC芯片上以及从IC芯片上分配出去;

(3)消除IC芯片上电路产生的热量;

(4)支持和保护IC芯片免受恶劣环境的影响。

1.3 半导体封装水平

半导体封装是一门艺术(工程学),其基础是建立从[1]零级封装(即芯片级连接,引线键合,焊料凸点芯片和胶带自动键合)到第一级封装的互连的科学(例如,引线框,基板,成型件和单/多芯片模块)和第二级封装,即板级互连或PCB。图1.1示意性地示出了简单的半导体封装的横截面。可以看出,芯片A是在带有焊料球的有机基板上的焊料凸焊倒装芯片。芯片A的电路通过通孔,焊点穿过基板散开,然后到达PCB。通过遍历PCB上的Cu迹线,电路使焊点,引线框,引线键合向上移动,并到达芯片B。这就是电子产品的工作方式。

1.4 专利影响半导体封装

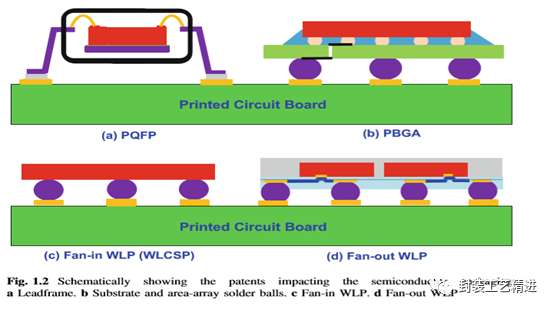

有许多重要的专利,例如焊料凸点的倒装芯片和影响半导体封装的硅通孔。但是,根据作者的观点,包含引线框,带有区域阵列焊球的有机基板,扇入式晶圆级封装和扇出式晶圆级封装(示意性显示在图1.2中)

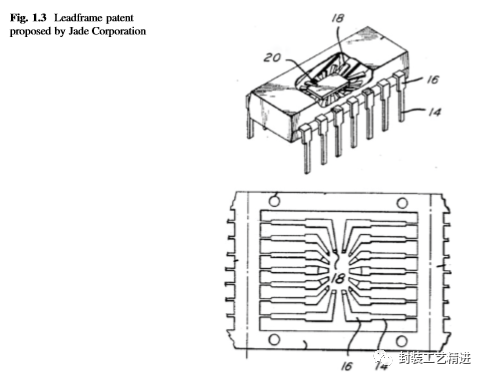

1.4.1 Leadframe引线框

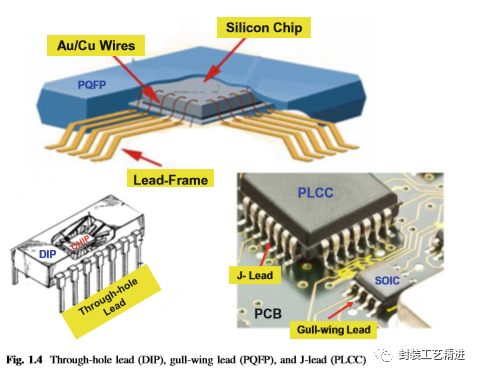

1967年7月17日,Jade Corporation的Kauffman [3]提出了一种使用带有端子(项目#18)的引线框架(参见图1.3中的项目14、16)将扇形电路从芯片上散开的方法(如图1.3所示的项目#20)连接至PCB。如今,几乎所有的电子产品都使用引线框架,例如鸥翼形引线(例如,塑料方形包装(PQFP)),J引线(例如,塑料引线芯片载体(PLCC))和/或双列直插式封装( DIP)将电路从芯片扇形展开至PCB(图1.4)。 PQFP的鸥翼式引线框的间距通常为0.4或0.5 mm,PLCC的J引线框的间距为1.27 mm,DIP的通孔引线框的间距为2.54 mm。在过去的近50年中,引线框架专利对半导体封装的影响最大。

1.4.2 Organic Substrate with Solder Balls带有区域阵列焊球的有机基板

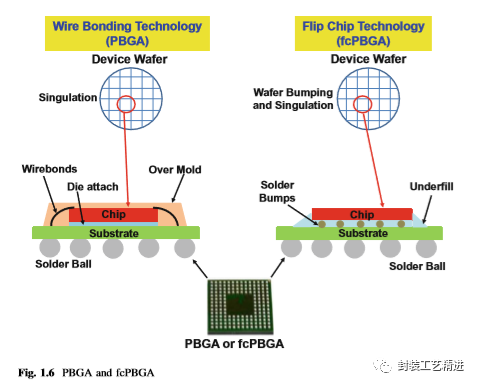

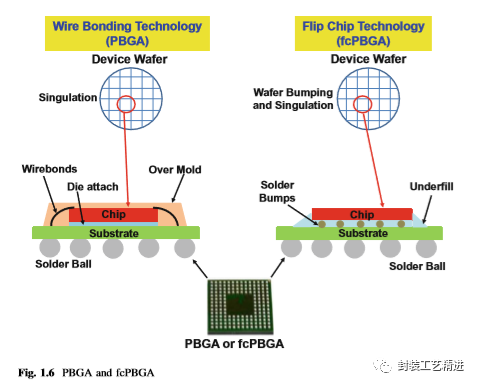

1992年3月2日,摩托罗拉的Paul Lin,MikeMcShane和Howard Wilson提出[4]使用带有区域阵列焊球(项目#26)的有机载体或基板(图1.5中的项目12)(而不是引线框)将电路(项目#22、30、33)从芯片(项目#18)(图1.5)散开到PCB,称为塑料球栅阵列(PBGA)封装。还参考图1.5,项目#22是引线键合,项目#32是将上布线层(项目#30)连接到下布线层(项目#33)的基板中的通孔。应当指出的是,1989年,摩托罗拉和《公民观察》发布了过模压焊盘阵列载体(OMPAC)封装,这是第一个PBGA。Amkor(1993)带领OSAT(外包的半导体组装和测试提供商)从摩托罗拉获得了这种封装技术的许可-BGA时代开始了。从那以后,在相关领域已获得了数百项专利,例如图1.6所示的有机基板上的焊料凸点倒装芯片。但是,它们是增量专利,而摩托罗拉的专利[4]是基本专利。与鸥翼式引线框架PQFP和J引线PLCC封装相比,带有有机基板和区域阵列焊球的PBGA封装的优点是

1.4.3 Fan-In Wafer-Level Packaging

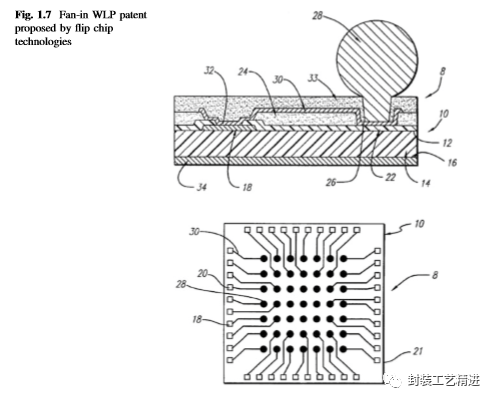

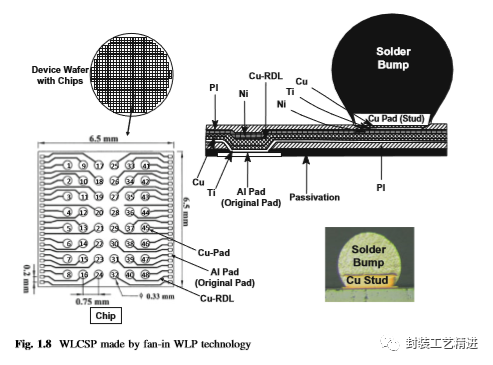

1998年7月13日,flip芯片技术的PeterElenius和Harry Hollack提出[6]使用重新分配层(RDL)(图1.7中的项目30)从原始外围接合垫(项目)中扇入电路#18,20)的筹码(项目#10)在晶圆上(第14项)和焊球(第28项)(图1.7)连接到PCB上而没有填充。RDL(项目#30)将外围键合焊盘(项目#18、20)上的电触点(项目#32)连接到焊料凸点焊盘(项目#26)。可以在晶片(项目14)的芯片(项目10)内制造大型焊球(项目28)。如图1.8所示,消除了引线框,基板和底部填充。应当指出,扇形晶圆级封装(WLP)的概念是由倒装芯片技术[6、7和8]首次提出的。但是,该领域的知识已被许多其他人提到/展示过,例如三菱[9,10],马可克斯[11],桑迪亚[12],ShellCase[13],弗劳恩霍夫IZM [14,15],DiStefano[16] ]和EPIC[17]。扇入式WLP制作的封装称为晶圆级芯片规模封装(WLCSP),其中最著名的一种是由ip芯片技术开发并获得专利的UltraCSP [18]。 2001年,Amkor再次领导OSAT和铸造厂获得UltraCSP许可,WLP时代开始了。在过去的16年中,WLCSP主要用于低引脚数(200),其重新分配的焊盘间距范围为0.5、0.4、0.35和0.3 mm,小芯片尺寸(6 mm 6 mm),低成本 ,低端,低性能和大批量应用程序。半导体IC,例如静电放电/电磁干扰保护,射频(RF)滤波,电源管理,功率放大器,表面声波/体声波滤波器,DC / DC转换器,发光二极管,电池和显示驱动器,音频/视频代码和放大器,逻辑门,电可擦可编程只读存储器(EEPROM),微控制器,蓝牙+频率 调制(FM)+ Wi-Fi组合,全球定位系统(GPS),基带和射频收发器已与各种WLCSP封装在一起,用于各种电子产品,例如手机,智能手机和平板电脑以及可穿戴设备。对于物联网(IoT)[19],CMOS图像传感器和MEMS传感器也将与WLCSP封装在一起。与PBGA封装相比,WLCSP的优势在于:(1)成本更低,(2)成型件,(3)尺寸小,(4)结构简单,(5)重量轻,(6)组装步骤少,(7)电气性能更好 性能;以及(8)消除了基板,底纹和一个水平的晶圆凸块。到目前为止,扇入式WLP专利是半导体封装中影响力第三大的专利。

1.4.4 Fan-Out Wafer-Level Packaging

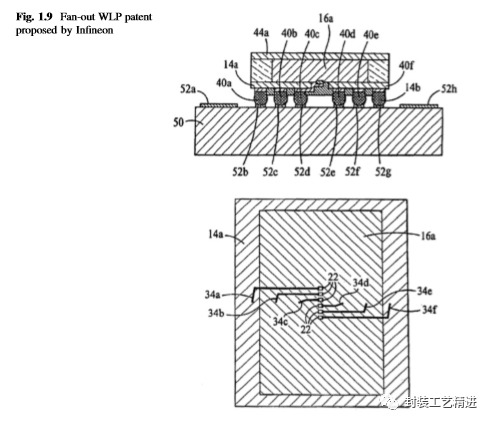

2001年10月31日,Infinion的HarryHedler,Thorsten Meyer和BarbaraVasquez提议[20]使用RDL(图1.9中的项目34a-f)将风扇扇出。从晶片上的芯片的金属焊盘(项目#16a)(项目#22a)和焊球(项目40a-f)到PCB上的金属焊盘(项目#52b-g)(项目50)的电路, 填充不足(图1.9)。一些RDL(项目#34a,34f)的一部分延伸超出(扇出)芯片(项目#16a)的边缘(项目#36a)。项目#26a是密封剂(模塑料)。项目#14a–b是介电层。应该指出的是,扇出WLP的概念是Infinone [20]首次提出的。尽管该技术的某些知识已经获得了通用电气[21,22]和EPIC [23]的专利,但是Infineon的专利[20]专门指出了使用RDL从金属焊盘上散开电路的方法。将晶片上的芯片和焊球连接到PCB上的金属焊盘上(图1.10)。 Infinon还特别指出,某些RDL的一部分延伸超出了芯片的边缘(呈扇形展开)。这些是[20]中的主要主张,GE和EPIC并未主张。英飞凌于2009年将其扇出WLP商业化,用于其无线基带SoC(片上系统),该功能具有LG手机的多种集成功能(GPS,FM无线电……)。自2010年以来,同一SoC也已在诺基亚手机中使用。从那时起,LG(无线基带),三星(基带调制解调器)和诺基亚(基带调制解调器和RF收发器)就在其手机和智能手机中使用了英飞凌的扇出WLP。Infinone的扇出WLP技术已获得ASE,STATSChipPAC,意法半导体和NANIUM(现为Amkor)的许可。

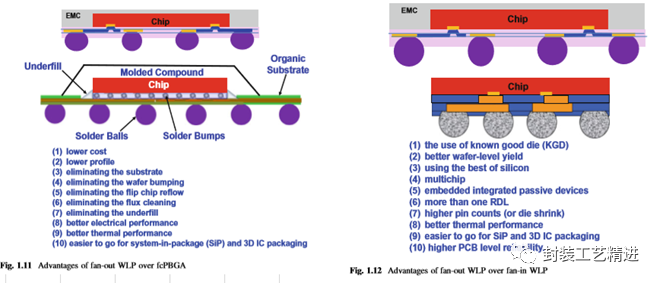

2011年,英特尔收购了Infinone的无线业务,其中包括扇出的WLP专利。英特尔使用扇出WLP技术将其RF IC(5毫米5毫米0.67毫米)与139个焊球以0.4毫米的间距封装在一起。扇出WLP优于具有焊料凸点ip芯片的fcPBGA封装的优点(图1.11)(1)成本更低,(2)轮廓更低,(3)消除了基板,(4)消除了晶片隆起,(5) 消除了倒装芯片的流焊;(6)消除了助焊剂的清洗;(7)消除了填充;(8)更好的电气性能;(9)更好的热性能;(10)便于系统级封装(SiP) )和3D IC包装[24]。与扇入WLP相比,扇出WLP的优势在于(图1.12)(1)使用已知的良好管芯(KGD);(2)晶圆级良率更高;(3)使用最好的硅,( 4)单芯片或多芯片;(5)嵌入式集成无源器件;(6)多层RDL;(7)引脚数更多;(8)更好的热性能;(9)更容易进行SiP和3D IC封装;以及 (10)更高的PCB级可靠性。扇出WLP可以实现扇入WLP的相同功能,例如用于低成本,低端,低性能,低引脚数,小尺寸和大批量应用。此外,扇出WLP可以完成PBGA的大部分工作,例如中端到高端微处理器,ASIC和存储器应用程序。但是,即使是扇出WLP也不是非常批量生产与扇入式WLP和PBGA相比的重要优势;它具有大幅增长的潜力。因此,作者认为扇出WLP是在不久的将来对半导体封装影响最大的四个。

1.5 Major Claims of Infineon’s Patent

Infinone专利[20]的主要主张是使用RDL将电路从芯片的金属焊盘和焊球散开到PCB上的金属焊盘。1.9和1.10。该公司[20]还声称,某些RDL的一部分延伸超出了芯片的边缘。事实上,Infinone [20]根本没有要求任何东西,例如,die-first or last, die-up or down, RDL-first or last, mold-firstor last, and reconfigured wafer or panel。这是一项“结构”专利。

1.6 TSMC InFO-WLP

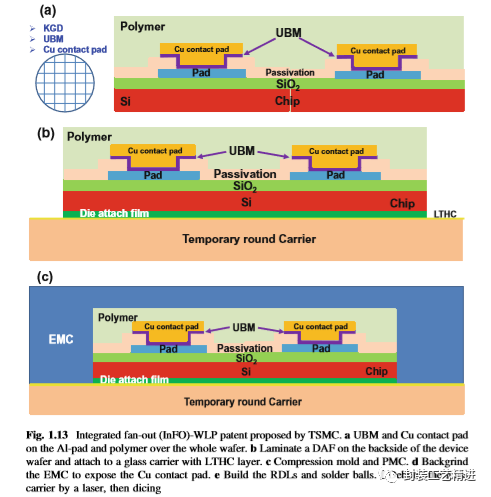

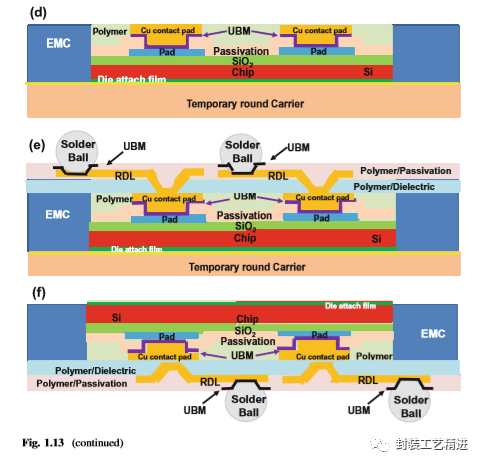

台积电的集成式扇出晶圆级封装(InFO-WLP)是最著名的扇出WLP之一。图1.13示意性地显示了InFO-WLP技术的典型过程[25-28]。它通过对器件晶圆的KGD测试开始。然后,通过具有物理气相沉积(PVD)的溅射(例如,Ti / Cu)来执行凸块下金属化(UBM),并且使用电镀来完成Cu接触垫(或柱)。这些步骤之后,在整个器件晶圆的顶部旋涂聚合物[例如,聚酰亚胺(PI),苯并环丁烯(BCB)或聚苯并双恶唑(PBO)],并在芯片的底部层压芯片连接膜(DAF)。整个器件晶圆。然后,将器件晶圆分割为单个管芯,图1.13a。如图1.13b所示,将单个的KGD放置(面朝上)在具有光热对话(LTHC)层的临时圆形载体(晶圆)上,然后分配EMC(环氧模塑料),压缩模制,然后在整个临时晶圆上使用KGD进行EMC的模后固化,以形成模制的重构晶圆(图1.13c)。接下来是对研磨后的晶片的EMC进行回磨,以暴露出铜接触垫(图1.13d),采用常规工艺[29]建立RDL(图1.13e),并安装焊球(图1.13)。 e。最后,移除临时晶圆(图1.13f),并将重新配置的晶圆分割为单个单元,然后我们采用InFO-WLP技术制成扇出封装。将图1.13f的横截面与图的。从1.9和1.10可以看出,它们是相似的,即RDL将电路扩展到芯片边缘以外。台积电(TSMC)一直在为应用处理器(AP)芯片组(移动DRAM + AP SoC)开发一种称为InFO-PoP的新型层叠封装(PoP)。就像台积电的CoWoS(晶圆上晶片)技术一样,他们称之为PoW(晶圆上封装)技术[30–32]。PoW表示将移动DRAM封装堆叠在AP InFO重新配置的晶片上,并且存储器封装与AP InFO封装之间的连接通过InFO-via(TIV)。台积电于2016年9月15日将采用FOWLP技术的AP的PoP投入量产。这非常重要,因为这意味着FOWLP不仅仅用于封装基带,电源管理IC,RF(射频)开关/收发器。RF雷达,音频编解码器,微控制器单元,连接性IC等,也可用于封装高性能和大型(> 120 mm2)SoC(片上系统),例如AP。有关台积电PoP的更多信息将在第8章中介绍。

1.7 Fraunhofer IZM FOPLP

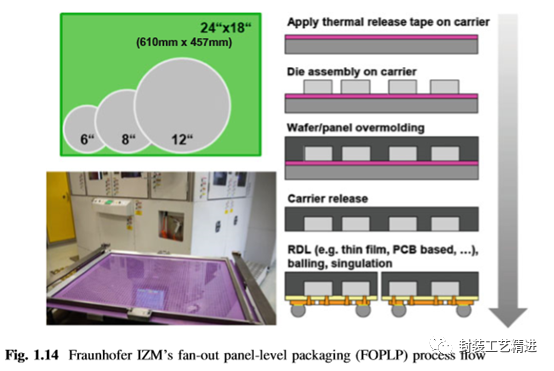

在2015 IEEE / ECTC期间,Fraunhofer IZM提交了一篇论文[33],总结了其在扇出面板级封装(FOPLP)方面的三年发展。他们表明,利用表面贴装技术(SMT)设备来拾取和放置裸片以及集成无源器件(IPD)和PCB技术来制造RDL,他们能够以非常低的成本制造FOPLP(使用大面板来代替 用于低端,低引脚数,小芯片尺寸和大批量应用。典型的FraunhoferIZM FOPLP工艺流程如图1.14所示,完整的FraunhoferIZM FOPLP集成线如图1.15所示。可以看出,没有任何半导体铸造设备。他们的测试工具是标准的PCB尺寸(610 mm 457 mm)矩形面板,如图1.14所示。将图1.14的横截面与图1和图2的横截面进行比较。从1.9和1.10可以看出,它们几乎是相同的,即RDL将电路扩展到芯片边缘以外。更多Fraunhofer的FOPLP将在第9章中介绍。

1.8 Ball/Bump Pitch/Size of PBGA, fcPBGA,WLCSP, and FOWLP

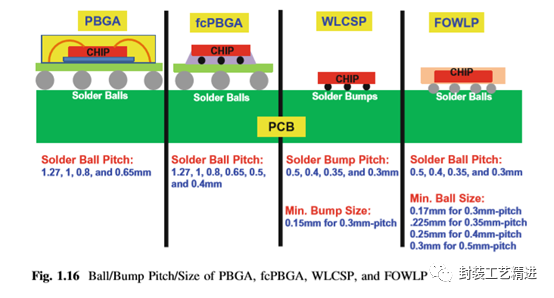

图1.16显示了PBGA,fcPBGA,WLCSP和FOWLP的焊球/凸点间距/尺寸。可以看出,引线键合PBGA的焊球间距为1.27、1、0.8和0.65 mm。fcPBGA的焊球间距为1.27、1、0.8、0.65、0.5和0.4毫米。引线键合PBGA和fcPBGA有所不同。WLCSP的焊料凸点间距为0.5、0.4、0.35和0.3 mm,对于0.3 mm的间距,WLCSP的焊料凸点尺寸为0.15 mm。FOWLP的焊球间距和尺寸尚无标准。但是,建议FOWLP的焊球间距为0.5、0.4、0.35和0.3mm。FOWLP的焊球尺寸为0.37毫米间距为0.17毫米,0.35毫米间距为0.225毫米,0.4毫米间距为0.25毫米,0.5毫米间距为0.3毫米。

1.9 Summary and Recommendations

已经研究了嵌入式扇出晶圆级封装的专利问题。一些重要的结果和建议如下:迄今为止,对半导体封装行业影响最大的专利是(1)引线框[3],(2)带有区域阵列焊球的有机基板[4],(3) 扇入WLP [6]和(4)扇出WLP [20]。

原文始发于微信公众号(半导体封装工程师之家):Fan-Out Wafer-Level Packaging

成员: 5306人, 热度: 153517

ceramics 天线 通讯 终端 汽车配件 滤波器 电子陶瓷 LTCC MLCC HTCC DBC AMB DPC 厚膜基板 氧化铝粉体 氮化铝粉体 氮化硅粉体 碳化硅粉体 氧化铍粉体 粉体 生瓷带 Ceramic substrate 氧化铝基板 切割机 线路板 铜材 氮化铝基板 氧化铍基板 碳化硅基板 氮化硅基板 玻璃粉 集成电路 镀膜设备 靶材 电子元件 封装 传感器 导电材料 电子浆料 划片机 稀土氧化物 耐火材料 电感 电容 电镀 电镀设备 电镀加工 代工 等离子设备 贴片 耗材 网版 自动化 烧结炉 流延机 磨抛设备 曝光显影 砂磨机 打孔机 激光设备 印刷机 包装机 叠层机 检测设备 设备配件 添加剂 薄膜 material 粘合剂 高校研究所 清洗 二氧化钛 贸易 equipment 代理 其他 LED