8英寸导电型4H-SiC单晶衬底制备与表征 娄艳芳,巩拓谌,张文,郭钰,彭同华,杨建, 刘春俊 北京天科合达半导体股份有限公司,北京 102600 摘要:使用物理气相传输法(PVT)通过扩径技术制备出直径为209 mm的4H-SiC单晶,并通过多线切割、研磨和抛光等一系列加工工艺制备出标准8英寸SiC单晶衬底。使用拉曼光谱仪、高分辨X射线衍射仪、光学显微镜、电阻仪、偏光应力仪、面型检测仪、位错检测仪等设备,对8英寸衬底的晶型、结晶质量、微管、电阻率、应力、面型、位错等进行了详细表征。拉曼光谱表明8英寸SiC衬底100%比例面积为单一4H晶型;衬底(004)面的5点X射线摇摆曲线半峰全宽分布在10.44″~11.52″;平均微管密度为0.04 cm-2;平均电阻率为0.0203 Ω·cm。使用偏光应力仪对8英寸SiC衬底内部应力进行检测表明整片应力分布均匀,且未发现应力集中的区域;翘曲度(Warp)为17.318 μm,弯曲度(Bow)为 -3.773 μm。全自动位错密度检测仪对高温熔融 KOH刻蚀后的8英寸衬底进行全片扫描,平均总位错密度为3293 cm-2,其中螺型位错(TSD)密度为 81 cm-2,刃型位错(TED)密度为3074 cm-2,基平面位错(BPD)密度为138 cm-2。结果表明8英寸导电型4H-SiC衬底质量优良,同比行业标准达到行业先进水平。 关键词:8英寸SiC单晶衬底;物理气相传输法;X射线摇摆曲线;微管密度;翘曲度和弯曲度;位错密度

碳化硅(SiC)作为第三代半导体材料,具有更宽的禁带宽度、更高的击穿电场、更高的热导率等性能优势,在高温、高压、高频领域表现优异,已成为半导体材料技术领域的主要发展方向之一。SiC衬底主要包括导电型和半绝缘型两类,二者在外延层及下游应用场景不同。导电型SiC衬底经过同质外延生长、器件制造可制成SiC二极管、金属-氧化物半导体场效应晶体管(MOSFET)等功率器件,被应用于新能源汽车、光伏发电、轨道交通、智能电网、航空航天等领域[1];半绝缘型SiC衬底经过氮化镓外延、器件制造可制成高电子迁移率晶体管 (HEMT)等微波射频器件,主要应用于5G通信、卫星、雷达等领域[2]。在半导体产业链中,衬底是晶圆制造的基础,是所有半导体芯片的底层材料,主要起到物理支撑、导热及导电作用,特别是在 SiC功率半导体器件中,由于使用了同质外延,SiC衬底质量直接影响外延材料的质量,进而对SiC功率半导体器件的性能发挥具有决定性的作用。

高质量SiC衬底的获得存在单晶制备和加工两方面的难度:一方面SiC通常需要在高温 (>2000 ℃)的环境中生长[3],而且SiC存在250多种晶型,因此制备高质量单一晶型的成本和难度非常大;另一方面,SiC硬度与金刚石接近,单晶的加工难度和成本都很高。据测算,在SiC器件制造各环节中,衬底成本占总成本近50%。衬底尺寸越大,单位衬底可集成芯片数量越多,单位芯片成本越低。采用8英寸(1英寸=2.54 cm)衬底比6英寸可多切近90%的芯片,边缘浪费降低7%,有利于进一步降低芯片的成本,因此大尺寸化是SiC产业链降本增效的主要路径之一。

目前,6英寸衬底是SiC衬底市场上的主流产品,而8英寸衬底是SiC半导体产业发展的主要方向之一。在国际上,行业龙头美国Wolfspeed Inc.(原 Cree)最早在2015年展示了8英寸SiC样品,其他多家企业也陆续宣布研发出了8英寸SiC衬底,例如Coherent Corp.(原Ⅱ-Ⅵ Inc.)、Rohm semiconductor Co. Ltd.、STMicroelectronics等。Wolfspeed Inc.是目前唯一一家实现8英寸SiC衬底量产的企业,其位于纽约莫霍克谷的8英寸SiC衬底工厂已于2022年4月正式投产[4]。国内产业界和科研机构虽然起步稍晚,但也取得不错的进展。2022年,多家单位公布了8英寸产品开发成功[5],这些单位有北京天科合达半导体股份有限公司、中国科学院物理研究所、山西烁科晶体有限公司、山东天岳先进材料科技有限公司、山东大学[6]等。

北京天科合达半导体股份有限公司(简称“天科合达”)成立于2006年,技术来源于中国科学院物理研究所科研项目及研究成果,是国内首家专业从事SiC单晶衬底研发和产业化的高新技术企业,十几年来一直坚守SiC衬底细分领域,6英寸SiC衬底产品已实现批量销售,得到了国内外知名半导体器件企业的广泛认可。天科合达从2020年开始开展8英寸导电型SiC单晶衬底的研发工作,经过2年多艰苦卓绝的技术攻关,突破了8英寸晶体扩径生长和晶片加工等关键技术难题,成功制备出高品质8英寸导电型SiC单晶衬底,并计划在2023年实现小规模量产。

2.1

晶体生长和衬底制备

本实验通过以自主研发的由c轴偏向<11-20>方向4°的6英寸4H-SiC衬底作为籽晶和扩径生长的起始点,采用物理气相传输(physical vapor transport, PVT)法进行扩径生长获得直径放大的SiC单晶。将放大的晶体进行切、磨、抛得到放大的新籽晶,通过多次迭代实现直径放大到200 mm以上,从而获得8英寸SiC晶体。生长过程中选择籽晶的碳面作为生长表面,原料端温度维持在2300 ℃左右,籽晶端的温度控制在2100 ℃左右,压力控制在4000 Pa以下,保持一定比例的氩气和氮气流动气氛调控n型掺杂,从而实现导电型4H-SiC单晶的稳定生长。生长完成后的晶体进行滚圆、磨平面得到标准直径的8英寸晶柱,以多线切割的方式进行切片,而后将切片进行研磨、抛光、清洗等一系列流程,制备出标准尺寸的8英寸导电型4H-SiC衬底。

2.2

性能表征

使用LabRamHR800型拉曼测试仪对8英寸4H-N-SiC衬底进行拉曼光谱检测,激发光源为532 nm,光斑大小为直径721 nm,共检测357点位,对衬底的晶型进行表征;

使用Panalytical-X’Pert3 MRD XL型高分辨X射线衍射仪进行结晶质量检测,采用单色源Cu Kα射线(λ=0.15406 nm),测试范围为±0.02°,步长0.0001°, 积分时间0.1s,检测衬底上、下、左、中、右半径中点处共5点位(004)衍射面的摇摆曲线,用以表征衬底的结晶质量;

使用光学显微镜检测衬底的微管数量和分布位置,并计算出微管密度;

使用非接触式电阻仪,参照SEMI-MF673中的方法Ⅱ[7],即非接触涡流法测量衬底55点位的电阻率;

使用应力检测仪对8英寸衬底的应力进行表征,该设备利用光在不同应力条件下传播会产生相位差这一特性,通过观察叠加偏振的光明暗来定性辨别应力大小和分布;

使用Tropel® FlatMaster 200对8英寸衬底的面型进行测量,该设备利用分析样品与设备参考平面反射光形成的干涉条纹来识别样品的面型和厚度变化;

使用540 ℃熔融KOH对衬底进行20 min刻蚀,并采用全自动位错扫描仪对其位错分布及密度进行扫描和统计。

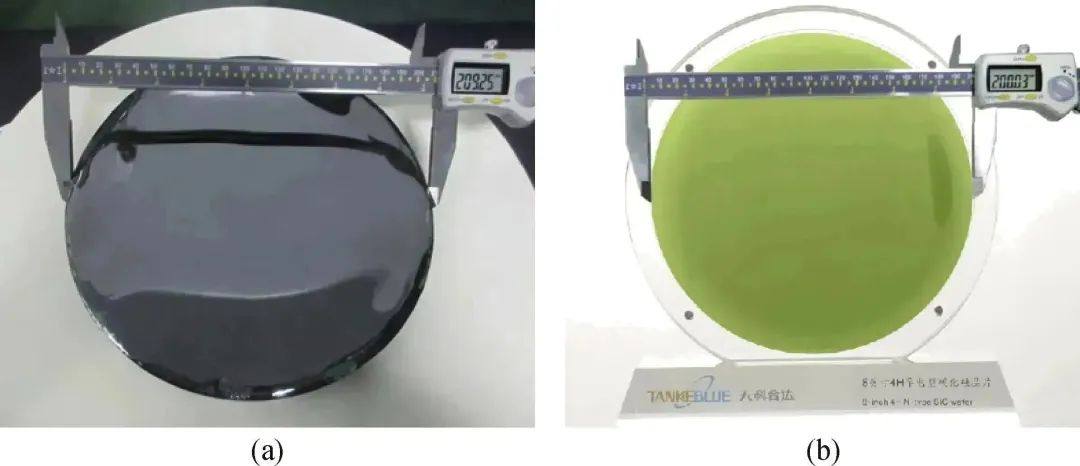

对于SiC晶体扩径生长,温场和流场决定了扩展边缘结晶完整度和晶型单一性,在晶体边缘处存在的SiC、石墨、气态分子多种物质交织发生化学反应的驱动力与表面沉积、原子迁移、吸附-解吸附等过程之间的动力学关系,决定能否实现晶体扩径生长。随着SiC晶体尺寸的增大,温场和流场的不均匀性更加明显,扩径生长难度也显著增加。 采用热场模拟与工艺试验相结合方法,开展设备关键结构设计、高匹配籽晶黏接、局部热场设计优化改进,解决大尺寸晶体扩径生长边缘缺陷增殖和热应力问题,实现低应力8英寸SiC单晶扩径生长。PVT法生长的8英寸导电型SiC晶体如图1所示,晶体直径达到 209.25 mm。生长界面微凸,表面光亮平滑且无任何裂纹,表明生长过程结晶比较稳定。按标准加工流程制成直径为200.03 mm的标准8英寸衬底,自然光下呈棕绿色,表面无明显多晶、划痕、崩边等肉眼可见缺陷。

图1 天科合达8英寸SiC晶锭和晶片。(a)直径达到209 mm的SiC晶锭;(b)标准8英寸SiC晶片

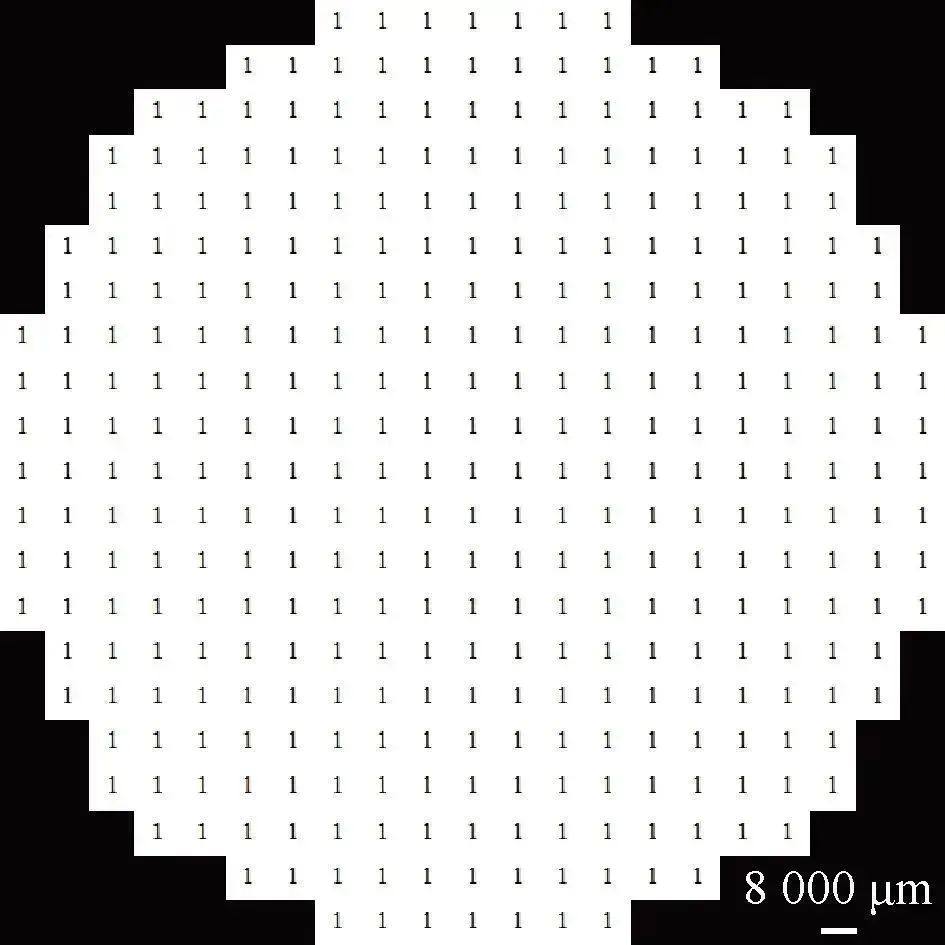

拉曼光谱对晶片357点位的测试结果如图2所示。各测试点位均出现形貌相似的拉曼峰,且与声子模以及简约波矢和对称性为204 cm-1(FTA,x=0.5,E2)的拉曼峰偏差不大于0.65 cm-1。与此同时,结果中未测得6H晶型对应的FTA模(150 cm-1),以及15R晶型对应的FTA模(174 cm-1)等高强度简约波矢模[8]。由此可得8英寸SiC晶片的4H晶型占比为100%。

图2 8英寸4H-SiC晶片拉曼光谱扫描图(1为4H-SiC,2为6H-SiC,3为15R-SiC)

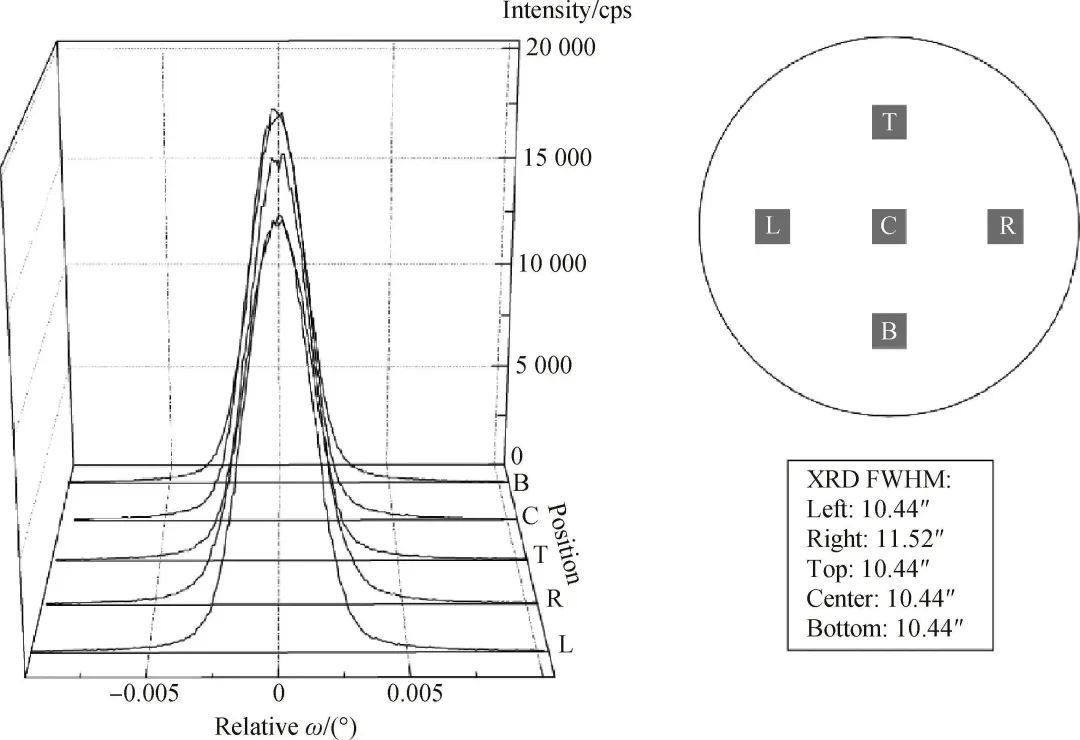

高分辨率X射线摇摆曲线测试结果如图3所示,测试点位为衬底中心和上、下、左、右半径的中心位置共5点。从图中可以看出,各测试点位的(004)衍射峰均为单一峰,其对应的半峰全宽分布在10.44″至11.52″之间,表明8英寸4H-SiC衬底结晶质量良好,不存在多晶、小角晶界等影响结晶质量的缺陷。

图3 8英寸SiC晶片(004)晶面高分辨X射线衍射图谱

使用光学显微镜对8英寸衬底的微管密度进行全自动扫描,去除边缘3 mm区域的微管进行统计后得出,该8英寸衬底的微管密度为0.04 cm-2。整片中共发现微管14个,且均分布于边缘,如图4所示。

图4 8英寸SiC晶片微管分布

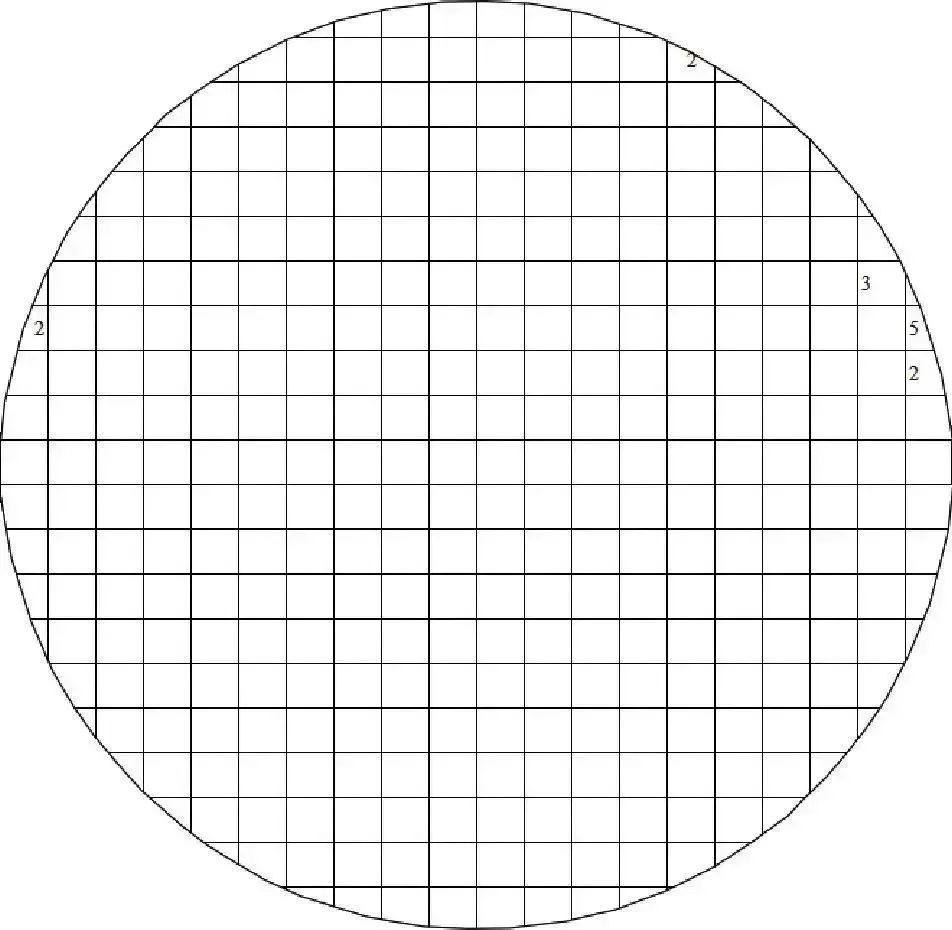

采用非接触式涡流法测试8英寸SiC衬底电阻率,结果如图5所示。结果显示,8英寸衬底的平均电阻率为0.0203 Ω·cm,最大值为0.0208 Ω·cm,最小值为0.0199 Ω·cm,相对标准偏差为1.11%。

图5 8英寸SiC晶片电阻率测试结果

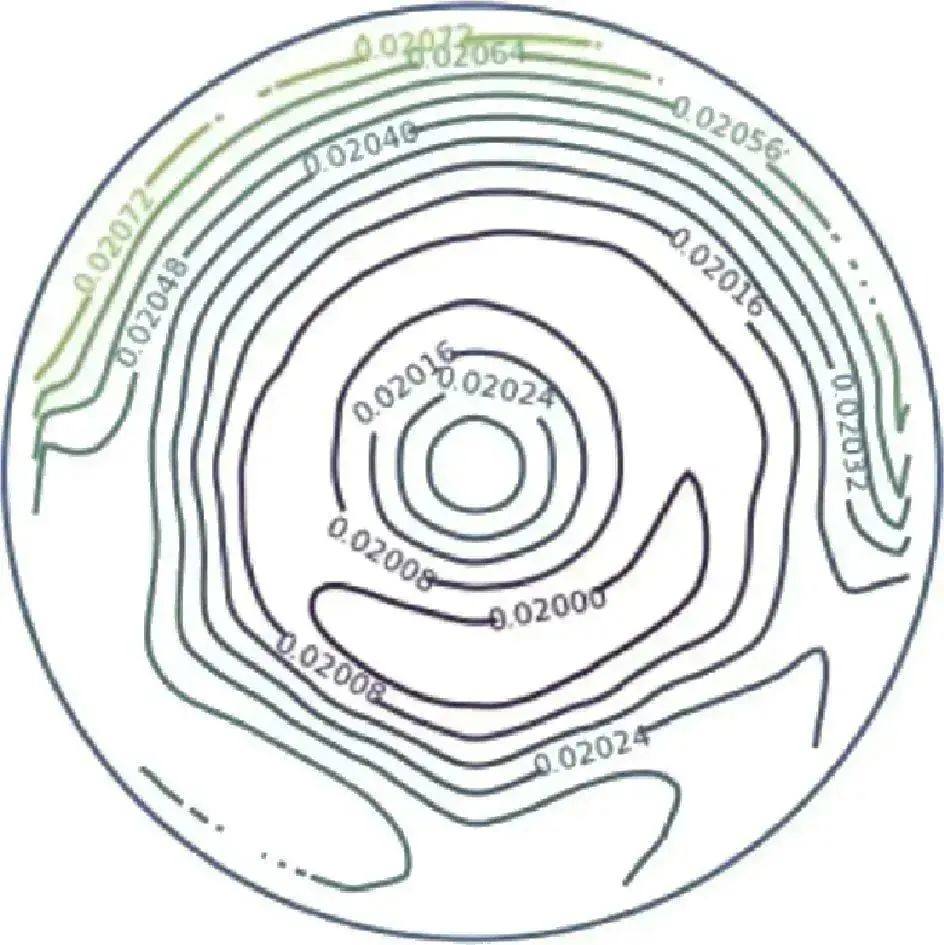

采用偏振光应力仪检测的8英寸衬底应力分布,如图6所示。一般地,测试结果中明暗波动较大的区域应力较大[9]。该8英寸SiC衬底整体应力分布均匀,除在小面位置外侧以及衬底边缘位置存在低强度应力区域外,大部分区域未见明显的应力集中区域,表明晶体的结晶质量良好。

图6 8英寸SiC晶片偏振光应力测试结果

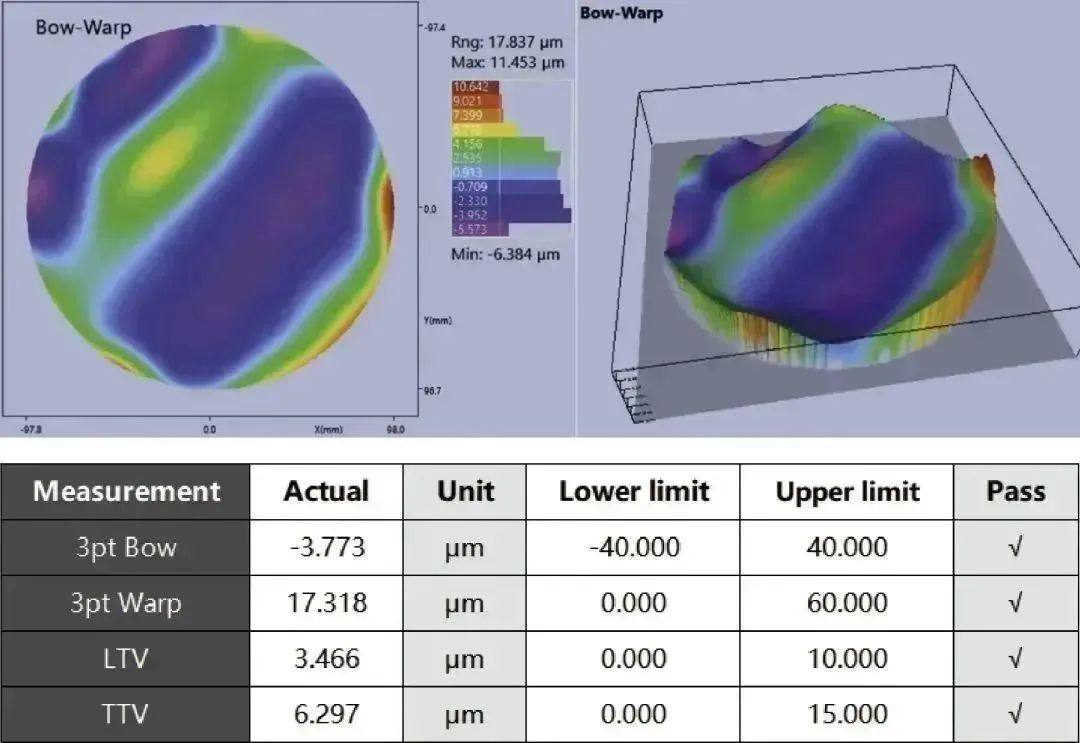

使用FM200测试的晶片面型结果如图7所示。通过测量得出该8英寸晶片的3点弯曲度(Bow)为-3.773 μm,3点翘曲度(Warp)为17.318 μm。

图7 8英寸SiC晶片平整度测试结果

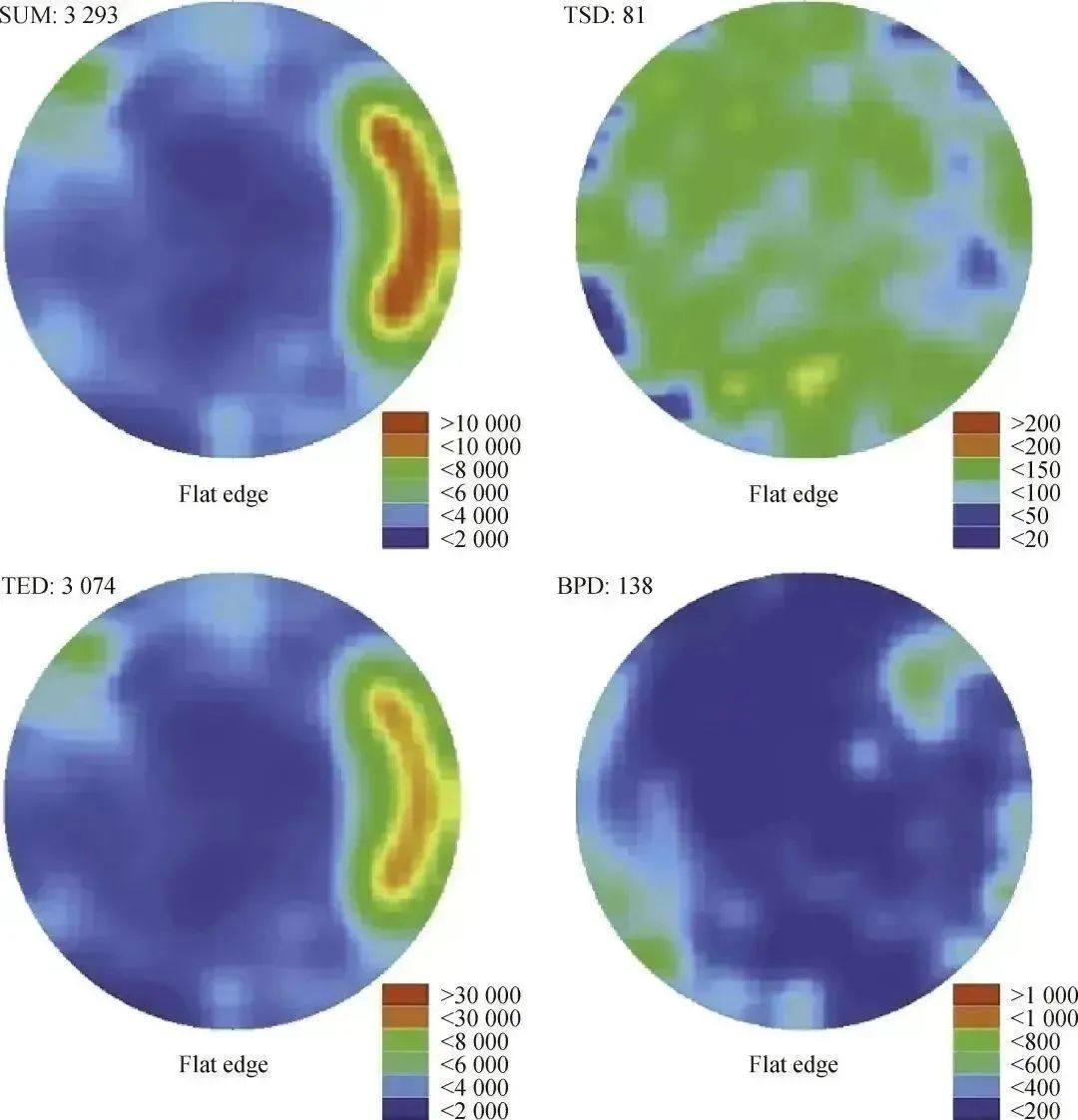

通过熔融KOH刻蚀,SiC衬底硅面表面的位错位置被择优腐蚀放大,即位错腐蚀坑。使用自动位错检测仪对腐蚀坑的形貌进行识别和分类,并统计出位错在衬底上的分布和位错密度。结果显示,该8英寸衬底的位错腐蚀坑密度(etch pit density, EPD)为3293 cm-2,其中螺型位错(threading screw dislocation, TSD)密度为81 cm-2,刃型位错(threading edge dislocation, TED)密度为3074 cm-2,基平面位错(basal plane dislocation, BPD)密度仅为138 cm-2。各类型位错的分布如图8所示。由于小面区域的生长习性与其他区域不同,导致位错密度在此位置明显高于其他区域,符合理论预期。

图8 8英寸SiC晶片位错分布图

综合上述结果,该SiC衬底的各项指标与当前6英寸SiC衬底的行业标准[10-11]相当,可满足后续8英寸外延、器件等加工要求。

使用PVT法通过多次扩径生长将SiC晶体直径从150 mm扩大到209 mm,并通过多线切割、研磨、抛光等一系列加工工艺,制备出标准的8英寸衬底产品。8英寸4H-SiC衬底4H晶型比例为100%,5点X射线摇摆曲线半峰全宽分布在10.44″~11.52″,平均微管密度为0.04 cm-2,平均电阻率为0.0203 Ω·cm。衬底不存在明显应力区,Warp值为17.318 μm,Bow值为-3.773 μm,总位错密度为3293 cm-2,其中TSD密度为81 cm-2,BPD密度为138 cm-2,各项检测指标均达到了行业先进水平。为满足国内外客户对于8英寸SiC衬底的迫切需求,天科合达公司预计2023实现小规模量产。

转发自《人工晶体学报》2022,51(12):2131-2136

原文始发于微信公众号(天科合达):天科合达研发团队在《人工晶体学报》上发表8英寸导电型SiC单晶衬底制备与表征重要文章